���ЙnFPGA���F����DDR3�惦��������

������

��������ϵ�y������������ӣ����ᘌ����ߵ��ٶȺ����ܣ��OӋ�ˆT���惦���g�M���˃�������һ���p�������ʣ�DDR��SDRAMоƬ��DDR3 SDRAM�� DDR3 SDRAM���б�DDR2����ă��ݡ��@Щ�����Ĺ��ĸ��ͣ����Ը��ߵ��ٶȹ������и��ߵ����ܣ�2���Ď����������и�����ܶȡ��cDDR2��ȣ�DDR3�����Ĺ��Ľ�����30������Ҫ������С��оƬ�ߴ���͵��Դ늉���DDR3 1.5V��DDR2 ��1.8V���� DDR3����߀�ṩ�����Ĺ��s�YԴģʽ����ֲ�ˢ�¡��cDDR2��ȣ�DDR3����һ���@�����c�Ǹ��ߵ�����/�������@�������и������Aȡ���_���c4λ��DDR2��ȣ�DDR3��8λ�������Լ����ߵĹ����r��l�ʡ�Ȼ�����OӋ��DDR3�Ľӿ�Ҳ׃�ø��������ԡ���FPGA�Ќ��F���١���Ч�ʵ�DDR3��������һ��D���΄ա�ֱ�������ֻ���ٔ��߶ˣ����F����FPGA��֧���c���ٵ�DDR3�惦���ɿ��ӿڵĉK��Ȼ�����F����һ���Йn��FPGA�ṩ�@Щ�K������FPGA�ܘ����r犹����YԴ����Ҫ���F��һ��DDR3��������I/O�Y��������̽ӑ�OӋ�������������Լ������һ���ض���FPGAϵ��LatticeECP3���FDDR3�惦����������

����DDR3�惦��������������

����ᘌ��惦����������DDR3�������Rһϵ�е�����DDR3�Ĺ����l����ʼ��DDR2�ĸ��ߵĹ����l�ʣ�Ȼ��څ�ڸ��ߵ��l�ʡ� DDR3�ӿ���Ҫ�ĕr��ٶȳ��^400 MHz���@�nj�FPGA�ܘ���һ���ش�����ᘌ�DDR3�惦���������ļܘ���fly-by�Y�����x���{��׃�ø��ӏ��s��

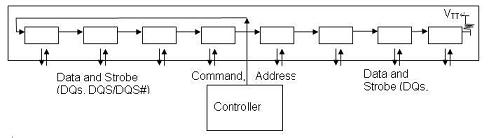

������ͬ��DDR2��T�ͷ�֧�ؓ�Y����DDR3������fly-by�ؓ�Y�����Ը��ߵ��ٶ��ṩ���õ���̖�����ԡ�fly-by��̖�������ַ�����ƺ͕r���̖����D1��ʾ��Դ�ڴ惦�����������@Щ��̖�Դ��еķ�ʽ�B�ӵ�ÿ��DRAM������ͨ�^�p�ٷ�֧�Ĕ����ͷ�֧���L�ȸ��M����̖�����ԡ�Ȼ�����@��������һ�����}�����ÿһ���惦��Ԫ�������t�Dz�ͬ�ģ�ȡ�Q����̎�ڕr���λ�á�ͨ�^����DDR3Ҏ���Ķ��x�������x�{���͌��{�����g���a���@�N���t�IJ��fly-by�ؓ�Y�����Դ�_���rУ���惦��ϵ�y���@��Ҫ����DDR3�����������~�����Ϣ�����SУ�ʹ����چ��ӕr�Ԅ���ɡ�

�D1 ᘌ�DDR3��Fly-by�Y��

�����x�͌��{��

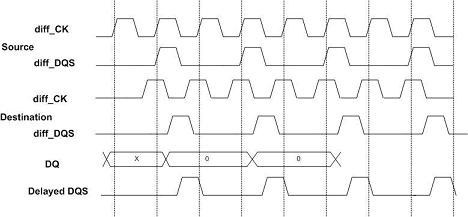

�����ڌ��{�����g���惦����������Ҫ�a���~��Ŀ�Խ�r�gƫ�ƣ���ÿ���惦����������̖���t�Dz�ͬ�ģ����@������fly-by�ؓ�Y�����xͨ�͕r�����ġ���D2��ʾ��ԴCK��DQS��̖���_Ŀ�ĵ������t�����ڴ惦��ģ�K��ÿ���惦��Ԫ�����@�N���t�Dz�ͬ�ģ��������оƬ�M���{�������оƬ�ж���һ���ֹ��Ĕ���������Ҫ�����ֹ����M���{����ԓ�D�f����һ���惦��Ԫ�����惦�����������t��DQS��һ��һ����ֱ���z�y��CK��̖��0�^�ɵ���1���@���ٴΌ��RDQS��CK���Ա�DQ�����ϵ�Ŀ�˔������Կɿ��ر����@�������@����DDR3�惦���������Ԅ����ģ��·���OӋ�ˆT�o횓��Č�ʩ�ļ������OӋ�ˆT�����~���ԣ���еõ���̎���@����DDR3�惦���������еČ��{���������������ġ�

�D2 ���{���ĕr��D

����DDR3�惦���r��YԴ�ͽӿ�ģ�K

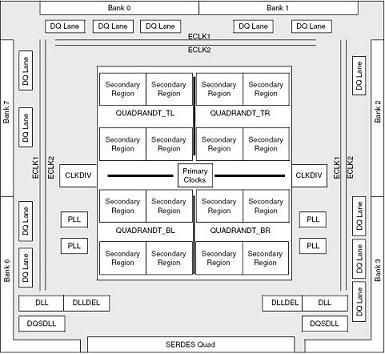

����LatticeECP3 FPGA��I/O�Ќ��T���·֧�ָ��ٴ惦���ӿڣ�����DDR��DDR2��DDR3 SDRAM�惦���ӿڡ���D3��ʾ��ECP3ϵ��߀�Ќ��õĕr��YԴ����֧����һ��DDR3���ٴ惦����������߅���r犣�ECLK1��ECLK2���Ǹ��٣�����ƫ�ĕr犣����ڕr犿��Ɣ������ٵ��M����������DQS��ͨ���ṩ�r�ݔ�루DQS�����cԓ�r����P�Ķ��_10��ݔ�딵��λ��DQSBUF������ÿ��DQSͨ�����Կ��ƕr��L�������t��DQSDLL֧��DQSͨ����ÿ����������Ⱥ��҂ȶ���һ������DQSDLL�nj��T���ژ���90�ȕr����t��DLL����

�D3 LatticeECP3 DDR�惦���r��YԴ

�����R��˼��DQS�·����һ���Ԅӕr��D�Q�·�������˴惦���ӿ��OӋ�����_���˿ɿ��IJ��������⣬DQS�����t�K�ṩ��ᘌ�DDR�惦���ӿ�����ĕr犌��R��ͨ�^DQS�����t��Ԫ�����õ�DQS�����YԴ����PAD�ṩDQS��̖���ضȣ�늉���ˇ׃��������DQS���t�K�a���IJ���O�õ�У����̖���a����7λ���t���ƣ���У����̖Դ��������߅�ăɂ�DQSDLL����������һ�룬ÿ��DQSDLL���a����߅��DQS���t��ͨ�^ϵ�y�r犺͌��÷����h·����DLL�h�M�����a������

����LatticeECP3 FPGA���i��h��������ᘌ�DDR3�惦���ӿڕr犡����磬����һ��400 MHz��DDR3�ӿڣ�ͨ���i��h�������������r犣�400 MHz�ĕr犣���90 �����Ƶ�400 MHz�r犺�200 MHz�r犡���90 �����Ƶ�400 MHz�r���������DQ��DQSݔ�����]�����Ƶ�400 MHz�r����ڮa���r犣�CLKP��CLKN����DDR3�惦����200 MHz�r��������ɵ�ַ�����ADDR/CMD����̖��ԓ�r犵Č��F���͑������ģ������R��˼���OӋ�����Ԅӵ،��F�� <-- 2010/1/23 19:24:08-->