圖解半導(dǎo)體制程概論(2)

圖解半導(dǎo)體制程概論(2)

邏輯IC

電子機(jī)器的動(dòng)作所必需的內(nèi)部信號(hào)處理大致可以分為模擬信號(hào)處理和數(shù)字信號(hào)處理。處理前者的是模擬用半導(dǎo)體器件,處理后者的數(shù)字信號(hào)處理的就是邏輯IC,邏輯IC中也有很多種類。

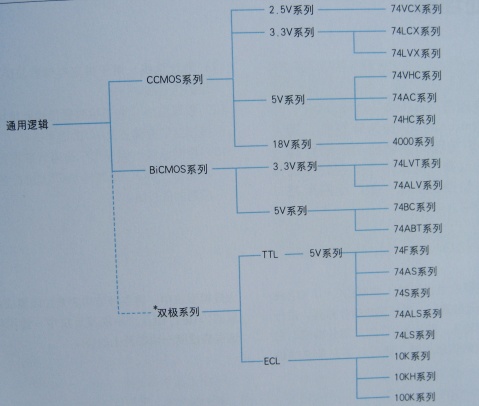

IC、LSI在制造程序上大致分為雙極系列和MOS系列,還可以再分為混合兩者的BiCMOS等復(fù)合型。

邏輯IC是執(zhí)行數(shù)字信號(hào)處理的IC、LSI,雙極系列(也就是雙極邏輯)現(xiàn)在只有TTL和ECL,因此提及邏輯IC時(shí),一般可以視為指CMOS邏輯系列以及BiCMOS系列。

而且,邏輯IC也可分為(1)通用邏輯、通用MPU之類的標(biāo)準(zhǔn)品;(2)ASIC(特殊用途用IC);(3)配合本公司規(guī)格開發(fā)的定制LSI專用產(chǎn)品這幾類。

ASIC可以分成ASCP(顧客專用品)和ASSP(待業(yè)專用品),ASCP還能進(jìn)一步細(xì)分成門陣列(GA)、可現(xiàn)場編程式門陣列(FPGA)、標(biāo)準(zhǔn)單元(SC)、嵌入式單元陣列(ECA)等。但是,即使是完全的定制IC,但通訊用或數(shù)碼家電、車載系統(tǒng)中基本使用的電路及構(gòu)件等都是相同的,開發(fā)上的平臺(tái)大都由半導(dǎo)體生產(chǎn)廠家準(zhǔn)備。通過以平臺(tái)為基礎(chǔ)進(jìn)行設(shè)計(jì),可以縮短開發(fā)時(shí)間。像這樣定制IC和ASIC的界限沒有明確區(qū)分,有時(shí)也將定制IC作為通用產(chǎn)品進(jìn)行銷售,由此可見,目前情況下這樣的分類是非常困難的。

邏輯IC中有被稱為MPR(microperipheral:微控制器周邊設(shè)備)的器件。這是和于硬盤、圖像處理、打印機(jī)等,主要用于計(jì)算機(jī)周邊設(shè)備的專用LSI。各機(jī)器生產(chǎn)廠家大都采用ASIC的方法進(jìn)行開發(fā),和上述一樣很難做出明確的分類。

邏輯IC可以分為制造工藝、應(yīng)用領(lǐng)域、設(shè)計(jì)方法等3種,因此分類越來越困難。

邏輯IC、LSI的分類

О雙極邏輯IC、LSI

TTL(Transistor Transistor Logic)

目前,只有部分生產(chǎn)廠家在生產(chǎn),市場也在不斷縮小。

ECL(Emitter Coupled Logic)

通過把NPN雙極晶體管放在非飽和區(qū)域使用,并縮小理論振幅來獲得高速特性,可用于要求高速性的IC測試器、通訊用等。

О代表性的CMOS邏輯IC/LSI

通用CMOS邏輯

MPU(Micro Processing Unit)

MCU(Micro Controller Unit)

DSP(Digital Signal Processor)

MPR(Micro Peripherals)

ASIC(Application Specific IC)

GA(Gate Array)

SC(Standard Cell)

DSP的例子

面向各種用途的邏輯IC

CMOS和反相電路

CMOS電路是由P通道能及N通道雙方的MOS晶體管構(gòu)成的電路。由于具有消耗電流少、高速化方便、抗雜音能力強(qiáng)、輸入輸出全擺式等特點(diǎn),因此現(xiàn)在幾乎所有的LSI都是在這種技術(shù)的基礎(chǔ)上構(gòu)成的。

CMOS技術(shù)

CMOS的結(jié)構(gòu)是在N型基板中形成P通道的晶體管,在N型基板中做成較大的低濃度P型區(qū)域(叫娓娓動(dòng)聽 P井),在P井中形成N通道晶體管。還有與基相反,使用P型基板做成N井的。

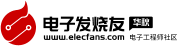

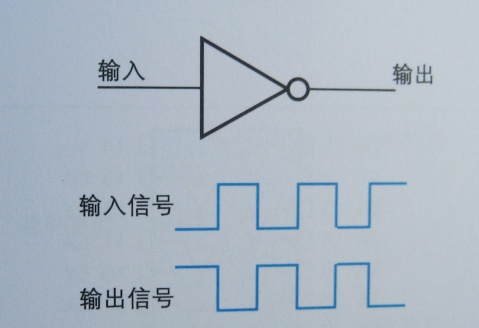

反相器

是邏輯IC/LSI的基本電路。如圖所示,舉例說明N型或P型晶體管(TN、TP)串聯(lián)形成的反相電路。門極G上輸入 “1”信號(hào)(SP電位)的話,TN將為ON,而TP則成為OFF。相反,輸入“0”信號(hào)(SN電位)的話,TN為OFF,而TP則成為ON。對(duì)于任何輸入,總有一個(gè)對(duì)應(yīng)的晶體管是OFF狀態(tài),且由SP到SN的電流不會(huì)流通,因此消耗電流將減少(PMOS、NMOS的1/100-1/1000)。ONOFF切換時(shí)因寄生電容會(huì)充放電,因此隨著工作頻率增加,耗電量將增大。

優(yōu)點(diǎn)

·非常少的耗電量

·快速的動(dòng)作速度

·抗雜音較強(qiáng)

·和TTL可兼弱容性

·以低電壓動(dòng)作簡單

缺點(diǎn)

·制作和序復(fù)雜且耗時(shí)長

用途

·標(biāo)準(zhǔn)邏輯(相當(dāng)于TTL邏輯)

·幾乎所有的數(shù)字LSI(MPU\MCU)\DSP\圖象處理LSI\語音處理)

·電子計(jì)算器\鐘表\游戲機(jī)

·掌上電腦

·電話機(jī)

·存儲(chǔ)器(RAM\ROM)

·其他\客戶規(guī)格邏輯電路等

CMOS反相器的圖形記號(hào)和動(dòng)作

?

CMOS反相器的電路圖

例:CMOS反相器的結(jié)構(gòu)圖

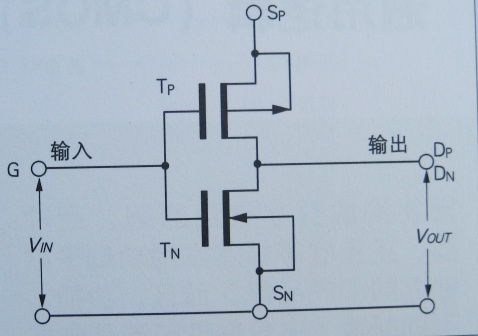

通用邏輯(CMOS)

指將構(gòu)成數(shù)字電路的閘、緩沖器、正反器等最基本的功能予以獨(dú)立的IC產(chǎn)品群。而且,功能、引腳配置、電氣特性等都是全球性標(biāo)準(zhǔn)化的產(chǎn)品群。在制程上還有CMOS、BiCMOS、雙極等。

通用邏輯的主要功能

·邏輯運(yùn)算功能(閘電路)圖1

·開關(guān)功能

·數(shù)據(jù)的保持功能 圖2

·總線驅(qū)動(dòng)器(緩沖器)功能 圖3

·計(jì)數(shù)器/除頻功能

·電平移動(dòng)功能

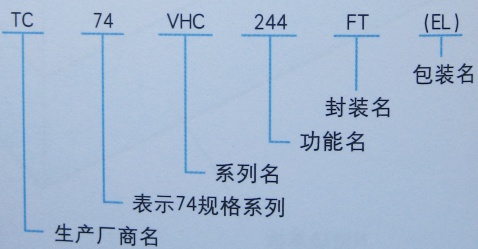

品名和標(biāo)準(zhǔn)化

附加74XXX的品名的標(biāo)準(zhǔn)邏輯作為74規(guī)格,其功能、引腳配置都加以標(biāo)準(zhǔn)化。如果品名(上述XXX的部分)相同,則功能、引腳配置無論哪個(gè)生產(chǎn)廠商、哪個(gè)系列都相同。系列名不同,數(shù)據(jù)處理速度、驅(qū)動(dòng)能力等性能將不同,相反,如果系列名相同,則無論哪個(gè)生產(chǎn)廠商的性能大致相同。各系列中有數(shù)十品種到百數(shù)十品種的產(chǎn)品(功能)。

*通用邏輯最早以使用雙極系列邏輯為主,現(xiàn)在能方便地實(shí)現(xiàn)低耗電量/低電源電壓的CMOS邏輯已成為主流。而且,雙極系列中,ECL也用于超高速應(yīng)用領(lǐng)域(高速測試器等)。

圖1 閘IC例/74VHC04

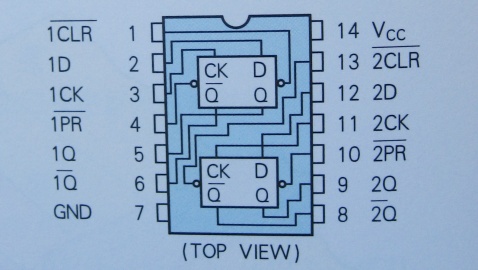

圖2 正反器IC例/74VHC74

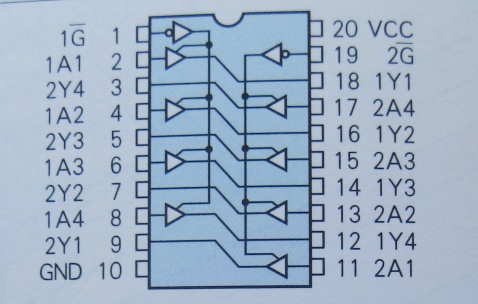

圖3 緩沖器IC例/74VHC244

品名的辨認(rèn)證

通用邏輯的種類

微處理器(micro-computer,簡稱micon),作為計(jì)算機(jī),通過LSI實(shí)現(xiàn)必要功能的小型計(jì)算機(jī)。從身邊的家電產(chǎn)品到計(jì)算機(jī)及小型控制機(jī)器,被廣泛應(yīng)用在系統(tǒng)中。

策處理器由進(jìn)行運(yùn)算、控制的CPU(中央運(yùn)算處理裝置)、進(jìn)行記憶的存儲(chǔ)器、進(jìn)行和外部輸入、輸出的I/O的三部分構(gòu)成。它們之間的信息交換,通過以下三務(wù)總線進(jìn)行。

(1)?????? 地址總線:用于指定存儲(chǔ)器及I/O地址的信號(hào)線;

(2)?????? 數(shù)據(jù)總線:用于將數(shù)據(jù)傳輸?shù)降刂房偩€指定的存儲(chǔ)器及I/O的信號(hào)線;

(3)?????? 控制總線:用于指示是否讀取或?qū)懭氪鎯?chǔ)器及I/O、或其他從CPU進(jìn)行各種控制的信號(hào)線。

大規(guī)模系統(tǒng)中,將各種結(jié)構(gòu)要素加以集成化后的LSI進(jìn)行組合,小規(guī)模系統(tǒng)中,使用將這些集成到一塊芯片上的LSI。

CPU和各種總線連接圖

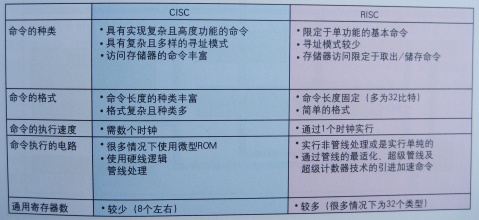

CISC和RISC

計(jì)算機(jī)心臟部分——CPU大致分為兩類。一類是具有實(shí)現(xiàn)復(fù)雜且高度功能的命令,旨在提高性能的CISC。還有一類是將命令設(shè)置單純化,旨在提高命令執(zhí)行速度的RISC。

CISC方式

減少一個(gè)處理所需的命令數(shù),旨在提高性能。通過1個(gè)命令就可以執(zhí)行復(fù)雜的動(dòng)作,因此叫做CISC(Complexed Instruction Set Computer:復(fù)雜命令集計(jì)算機(jī))方式 。相反,命令長度可變,且比較復(fù)雜,因此解讀需要一定的時(shí)間,用于執(zhí)行的內(nèi)部電路變得復(fù)雜,硬件設(shè)計(jì)的負(fù)擔(dān)增加。

RISC方式

只具有少數(shù)的單純性命令,旨在加快執(zhí)行速度。命令長度固定,因此解碼器電路及執(zhí)行電路的規(guī)模較小。命令只有最基本的,因此叫做RISC(Reduced Instruction Set Computer:縮小命令集計(jì)算機(jī))方式。命令數(shù)量少,因此需要軟件的負(fù)擔(dān)增加,但通過使用C語言等高級(jí)語言,可以提高開發(fā)效率。

CISC和RISO的特征

微處理器(MPU)

MPU是意氣風(fēng)發(fā)計(jì)算機(jī)所需的運(yùn)算、控制功能集成到一塊芯片上的LSI。隨著半導(dǎo)體集成電路技術(shù)的不斷發(fā)展,以往將多個(gè)IC進(jìn)行組合后構(gòu)成CPU的器件現(xiàn)在可以用一個(gè)MPU加以實(shí)現(xiàn)。

何謂MPU

我們將構(gòu)成微處理器要素中的運(yùn)算部分和控制部分合在一起的心臟部分叫做CPU,將這個(gè)CPU通過1個(gè)LSI加以實(shí)現(xiàn)的器件就是MPU(微處理器)。MPU不能單獨(dú)作為計(jì)算機(jī)動(dòng)作,因此將存儲(chǔ)器及I/O進(jìn)行組合后構(gòu)成計(jì)算機(jī)。

MPU的基本動(dòng)作

目前的大部分計(jì)算機(jī)都是從存儲(chǔ)器讀取命令、一個(gè)個(gè)逐步執(zhí)行的被叫做諾依曼型的器件。MPU讀取寫在存儲(chǔ)器內(nèi)的程序,解讀寫在程序內(nèi)的命令,按照指示,執(zhí)行將數(shù)據(jù)存儲(chǔ)到存儲(chǔ)器內(nèi),或?qū)?shù)據(jù)取出等作業(yè)。

微處理器的功作單元例

微型周邊設(shè)備(MPR)

所謂微型周邊設(shè)備(周邊LSI),是指存在于MPU和輸入輸出設(shè)備之間接口的LSI。主要分為支持MPU的LSI和控制周邊設(shè)備以及傳輸數(shù)據(jù)的LSI,根據(jù)不同用途,有各種種類。

MPR用于減輕對(duì)MPU的負(fù)擔(dān),提高整個(gè)微控制器系統(tǒng)的性能。因?yàn)橥ㄟ^專用LSI控制周邊設(shè)備,因此也可以減輕軟件的負(fù)擔(dān)。MPR不斷在必須采取圖形用及MPEG等圖像處理、聲音識(shí)別等高速處理的領(lǐng)域中得到應(yīng)用。

MPU支持用MPR

存儲(chǔ)器管理單元(Memory Management Unit:MMU)

采用大量且多種存儲(chǔ)器的系統(tǒng)中,管理存儲(chǔ)器變得復(fù)雜,因此要使用MMU,減輕MPU的負(fù)擔(dān)。

可編程中斷控制(Programmable Interrupt Control:PIC)

在需要多個(gè)中斷輸入的系統(tǒng)中,通過PIC擴(kuò)大中斷處理的功能。在連接很多周邊設(shè)備等情況時(shí),發(fā)揮整理交通的作用。

直接存儲(chǔ)器存取控制器(Direct Memory Access Controller:DMAC)

通過使用DMAC,可以在不通過MPU的情況下,直接在周邊設(shè)備及存儲(chǔ)器之間高速傳輸數(shù)據(jù)。在DMAC傳輸數(shù)據(jù)期間,MPU也可以進(jìn)行其它處理,因此可以大幅度提高系統(tǒng)的效率。

周邊控制用MPR

實(shí)時(shí)時(shí)鐘(Real-Time Clock:RTC)

這是用于系統(tǒng)的時(shí)鐘專用LSI。使用MPU的數(shù)據(jù)總線,輸入輸出時(shí)刻數(shù)據(jù)。一般情況下,備有專用電池,即使系統(tǒng)電源斷開,也將保持時(shí)鐘動(dòng)作。

硬盤控制器(Hard-Disc Controller:HDC)

這是用于控制硬盤驅(qū)動(dòng)器的專用LSI。硬盤可以高速保存大容量的數(shù)據(jù),因此成為計(jì)算機(jī)的輔助存儲(chǔ)裝置的主流。

除此以外,還有圖像處理用圖形顯示控制器(Graphic Display Controller:GDC)、CD-ROM/DVD-ROM驅(qū)動(dòng)用的伺服處理器、音頻用數(shù)字信號(hào)處理器(DSP)等各種專用的MPR。

微控制器(MCU)

微控制器是將除了執(zhí)行運(yùn)算及控制的MPU功能以外,還有存儲(chǔ)功能、輸入輸出控制功能集成在一塊芯片LSI上的器件。也叫做單芯片微控制器。

何謂MCU

MCU在1個(gè)LSI中,收納應(yīng)用設(shè)備所必須的大部分功能,做成極為小型的電路,因此成本低,適合量產(chǎn)。作為安裝在家電設(shè)備及產(chǎn)業(yè)設(shè)備等中的控制器,被大量使用。應(yīng)該內(nèi)置的周邊功能根據(jù)應(yīng)用設(shè)備不同而不同,因此針對(duì)特定用途的性格較強(qiáng),根據(jù)各種用途,做成多品種的MCU。

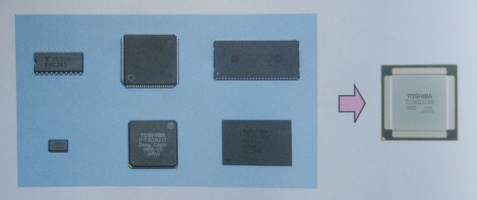

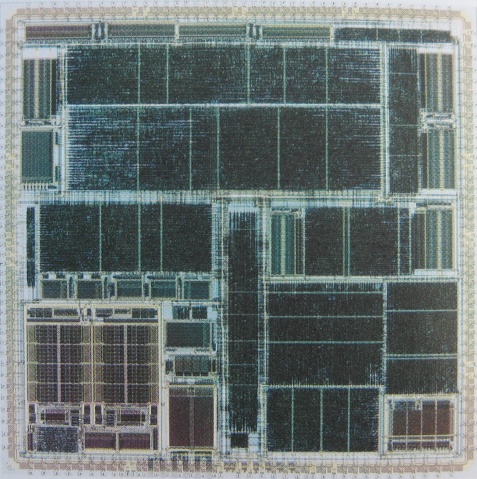

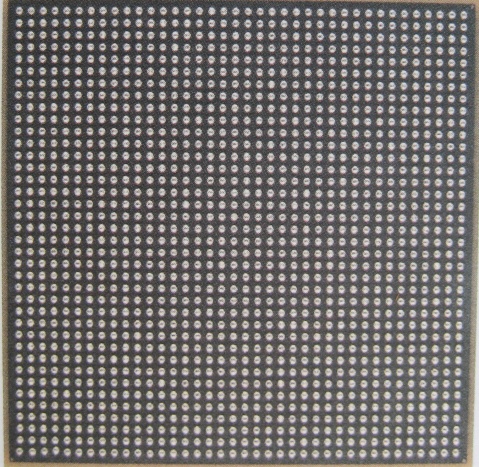

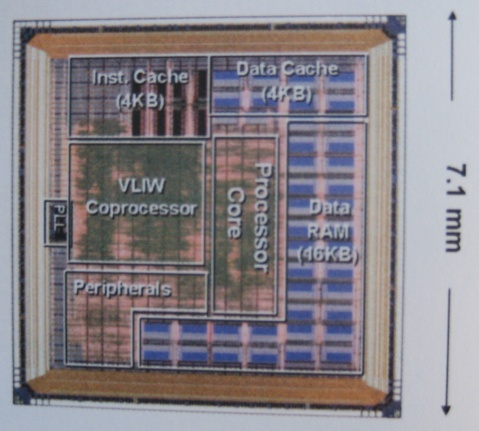

芯片放大照片

芯片的放框(左面照片)

微控制器的內(nèi)部結(jié)構(gòu)例

MCU應(yīng)用到彩色串聯(lián)打印機(jī)的舉例

微控制器開發(fā)系統(tǒng)

開發(fā)應(yīng)用了微控制器的產(chǎn)品時(shí),必須開發(fā)產(chǎn)品本身(硬件)及使微控制器動(dòng)作的程序(軟件)。這些開發(fā)以及驗(yàn)證所必須的一套器材統(tǒng)稱為開發(fā)系統(tǒng)。

★ 語言工具

?

語言工具是對(duì)用戶源程序執(zhí)行從編碼到編譯、匯編、鏈接等一系列作業(yè),用于輸出對(duì)象(執(zhí)行)文件的系統(tǒng)的總稱。

★ 設(shè)計(jì)支持工具(CASE工具)

CASE工具是用于支援以設(shè)計(jì)工程到編程工程以及文檔制作為中心的維護(hù)工程的系統(tǒng)名稱。

★ 嵌入控制

嵌入控制是對(duì)用戶源編程提供特定功能的軟件的總稱。

<實(shí)時(shí)OS>

用于控制安裝系統(tǒng)中多任務(wù)動(dòng)作的軟件。

<中間件>

通過軟件實(shí)現(xiàn)以往靠硬件實(shí)現(xiàn)的功能。

測試工具

用于確認(rèn)對(duì)象文件動(dòng)作的系統(tǒng)的總稱。

<調(diào)試工具>

“模擬器”及“仿真器”的用戶接口。

<模擬器>

用軟件模擬MCU動(dòng)作的軟件。無須控制器的系統(tǒng),適合于理論調(diào)試。

<實(shí)時(shí)仿真器>

在實(shí)際設(shè)備系統(tǒng)上確認(rèn)動(dòng)作的方法,是將“仿真控制器”及“仿真埠”進(jìn)行組合的系統(tǒng)的總稱。我們將在此設(shè)備上加上用戶接口——“調(diào)試工具”后的系統(tǒng)叫做“實(shí)時(shí)仿真系統(tǒng)”。

<輔助工具>

用于聯(lián)結(jié)“實(shí)時(shí)仿真器”和用戶對(duì)象的工具的總稱。

開發(fā)系統(tǒng)的概念圖

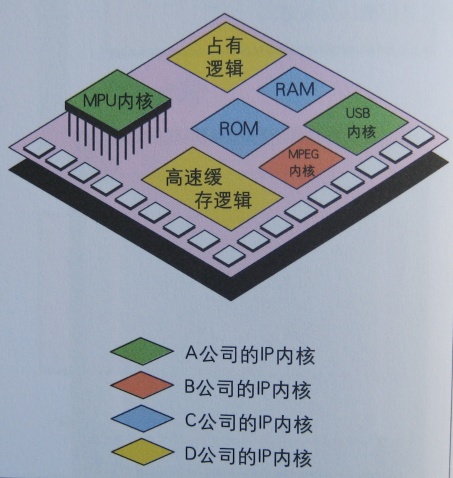

何謂系統(tǒng)LSI

主要將數(shù)碼家電、手機(jī)等通信用、以及汽車用所必須的系牢進(jìn)行集成的大規(guī)模設(shè)備專用的LSI即為系統(tǒng)LSI。隨著應(yīng)用領(lǐng)域的不斷擴(kuò)大,各種系統(tǒng)LSI的開發(fā)正在不斷發(fā)展,超出千萬柵的產(chǎn)品也陸續(xù)登場。

系統(tǒng)LSI沒有明確的定義。好像各公司有不同的定義,以下是一般的例子。

·具有多內(nèi)核(MPU、存儲(chǔ)器、邏輯或模擬)的單塊集成電路LSI;

·擔(dān)當(dāng)系統(tǒng)或子系統(tǒng)主要功能的LSI;

·10萬柵以上規(guī)模的LSI;

·針對(duì)單個(gè)或多用戶的特定應(yīng)用所開發(fā)的LSI。

不包括單芯片的微控制器及電子計(jì)算器用、時(shí)鐘用LSI、SRAM及快閃式存儲(chǔ)器的多芯片封裝產(chǎn)品、系統(tǒng)模塊。

系統(tǒng)LSI的具體應(yīng)用領(lǐng)域有數(shù)碼家電(數(shù)字TV機(jī)頂盒、DVD數(shù)碼相機(jī)、數(shù)碼攝像機(jī)等)計(jì)算機(jī)及周邊設(shè)備用(MPEG、圖形等圖像處理、硬盤用馬達(dá)及磁頭控制)、通信用(網(wǎng)絡(luò)、手機(jī)等)、汽車用(引擎控制、導(dǎo)航、智能傳輸系統(tǒng)等)等,還有一部分為產(chǎn)業(yè)用而開發(fā)。

用于數(shù)碼相機(jī)的系統(tǒng)LSI

系統(tǒng)LSI的具體應(yīng)用領(lǐng)域有數(shù)碼家電(數(shù)字TV\機(jī)頂盒\DVD\數(shù)碼相機(jī)\數(shù)碼攝像機(jī)等)

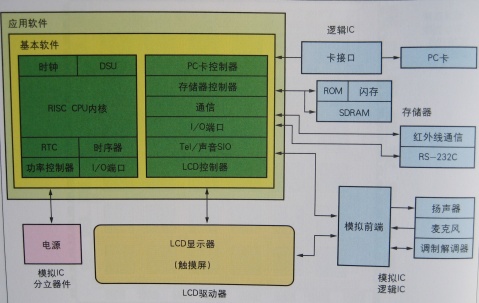

下一代多媒體LSI的系統(tǒng)圖

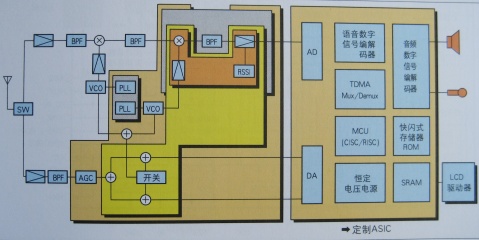

手機(jī)的方框圖

何謂DSP

DSP正如其名(Digital Signal Processor),是將數(shù)字信號(hào)處理加以特殊化的處理器。一般被稱為DSP的信號(hào)處理用處理器的內(nèi)部硬件或結(jié)構(gòu)和一般的MPU有幾大不同點(diǎn)。

DSP的重要特征如下所示。

·擁有高速乘法器(一般情況下也具有累加運(yùn)算結(jié)果的功能);

·具有哈佛型結(jié)構(gòu)(針對(duì)程序和數(shù)據(jù)擁有多個(gè)專用總線的結(jié)構(gòu));

·將程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器進(jìn)行分離、獨(dú)立;

·擁有高速化數(shù)據(jù)地址計(jì)算單元。

甚至還有根據(jù)需要,擁有AD轉(zhuǎn)換器等。即以高速乘法器為中心的哈佛型結(jié)構(gòu)、程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器加以分離、獨(dú)立,具有高速化數(shù)據(jù)地址計(jì)算單元的處理器叫做DSP。通過這些結(jié)構(gòu),比如必須采用乘法及其運(yùn)算結(jié)果的累加的數(shù)字式濾波器,可以在一般處理器十幾倍的速度下進(jìn)行運(yùn)算。但是,一般的MPU也不斷發(fā)展高速化,也開發(fā)出了具有上述特征的產(chǎn)品。今后,MPU和DSP的區(qū)別越來越難。促使區(qū)別越來越難的是用于實(shí)現(xiàn)上述共同的高速化的各種結(jié)構(gòu)、硬件。因?yàn)樗俣纫笤絹碓娇欤虼薉SP和MPU一樣,有使用相同結(jié)構(gòu)的趨勢。

應(yīng)用領(lǐng)域

·數(shù)字TV等數(shù)碼家電的各種信號(hào)處理用;

·數(shù)字手機(jī)的模擬、數(shù)字式基帶處理、聲音壓縮、調(diào)制/解調(diào)制用;

·硬盤、DVD-ROM等存儲(chǔ)設(shè)備的軸馬達(dá)及磁頭(讀取器)傳動(dòng)器的旋轉(zhuǎn)控制以及精密定位用;

·自動(dòng)控制馬達(dá)的轉(zhuǎn)矩控制、速度控制、精密定位用。

而且,DSP的應(yīng)用領(lǐng)域中采用高速的RISC處理器的情況也越來越多。在必須彩高速運(yùn)算處理的應(yīng)用領(lǐng)域中,過去好像不能將RISC和DSP絕對(duì)性的分開。今后,在RISC中安裝DSP的主要功能、硬件的一部分,或者反過來安裝,兩者的分界線越來直不明顯。

系統(tǒng)LSI應(yīng)該以最適合的信號(hào)處理運(yùn)算法則以及必須的結(jié)構(gòu),來符合其所需要的功能。無論是DSP還RISC處理器,甚至CISC處理器的主要功能、硬件,都是上述整合的方向。

DSP IC的結(jié)構(gòu)例

CD用DSP(將應(yīng)用加以特殊化的專用DSP例)

ASIC

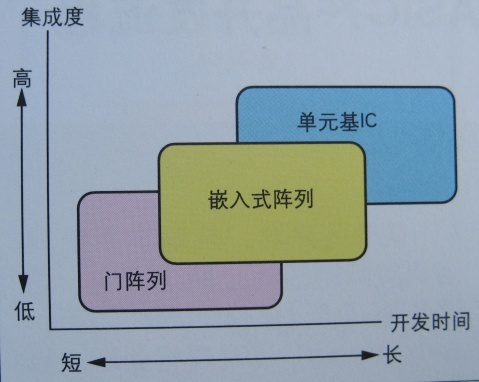

ASIC(Application Specific Integrated Circuit)是面向特定IC的總稱,包括全定制LSI、半定制LSI等各種LSI。代表性的有門陣列、單元基IC、嵌入式陣列。

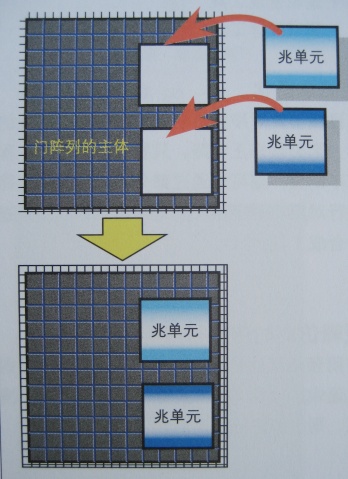

★門陣列(Gate Array)

門陣列是半定制LSI的一種,事先準(zhǔn)備好的稱為主體的晶圓。主體是晶體管呈陣列狀鋪設(shè)的結(jié)構(gòu)。門陣列的制造是在邏輯設(shè)計(jì)結(jié)束后在主機(jī)上實(shí)施布線,構(gòu)成希望的邏輯電路后完成。為此,具有開發(fā)時(shí)間短的特征。

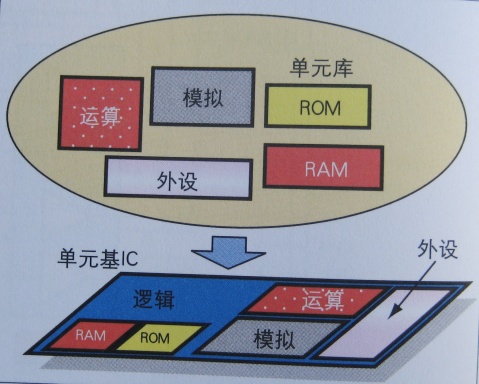

★單元基IC(Cell Based IC)

單元基IC是將最合適設(shè)計(jì)后的內(nèi)部邏輯及存儲(chǔ)器、模擬電路作為單元事先準(zhǔn)備好,再通過組合后設(shè)計(jì)LSI的器件。單元基IC為了從前道工程(擴(kuò)散工程)開始制造,LSI芯片的制造時(shí)間比門陣列的長,但具有設(shè)計(jì)靈活性高、功能高、集成化高等特征。

單元基IC(Cell Based IC)

ASIC實(shí)施例(嵌入式陣列)

嵌入式陣列是在門陣列的主體內(nèi)安裝單元基IC的高集成存儲(chǔ)器及高功能微單元的陣列。具有和單元基IC相同的集成度、高功能特征,同時(shí)也具有和門陣列相同的開發(fā)時(shí)間短的特征。

優(yōu)點(diǎn)

·小型化、重量輕

·高可靠性

·開發(fā)效率的提高

·高速化

·低價(jià)格化

·保持機(jī)密

·低耗電

用途

·計(jì)算機(jī)、工程、工作站、計(jì)算機(jī)相關(guān)設(shè)備

·OA設(shè)備

·通信設(shè)備

·數(shù)字AV設(shè)備

·一般產(chǎn)業(yè)用電子設(shè)備

·家庭用電子設(shè)備、游戲機(jī)等。

CMOS? ASIC的芯片照片

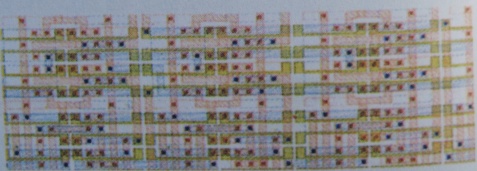

主體芯片的部分?jǐn)U大圖

門陣列布線后的部分?jǐn)U大圖

單元基IC的說明圖

各種ASIC的集成度和開發(fā)時(shí)間

嵌入式陣列的概念

ASIC產(chǎn)品開發(fā)流程

ADIC產(chǎn)品開發(fā),從確定系統(tǒng)規(guī)格到實(shí)際制造為止的工程中,難過各種EDA(Electronic Design Automation)工具進(jìn)行處理、驗(yàn)證。

邏輯合成、測試設(shè)計(jì)

使用邏輯合成系統(tǒng),從上位設(shè)計(jì)記述生成柵極的設(shè)計(jì)記述。還根據(jù)需要進(jìn)行考慮了測試的設(shè)計(jì)。

★使用EDA工具

邏輯合成工具

測試設(shè)計(jì)工具

邏輯最適化

當(dāng)邏輯仿真時(shí)序解析的結(jié)構(gòu)發(fā)生違反情況的話,則必須修正電路。只要違反的地方、程序不明顯,都可以通過部分修正原先的電路進(jìn)行對(duì)應(yīng)。時(shí)序違反的電路修正可以使用邏輯合成工具執(zhí)行。

邏輯仿真時(shí)序解析(配置布線前)

使用預(yù)估值進(jìn)行仿真。如果沒有違反,則快速sign-lff(簽名發(fā)布),但如果違反情況,則必須進(jìn)行邏輯最適化。

★EDA工具

Verilog模擬工具

VHDL模擬工具

時(shí)序解析工具

配置布線

以sing-off(簽名發(fā)布)后的柵層級(jí)設(shè)計(jì)記述為基礎(chǔ),以滿足時(shí)序之規(guī)定進(jìn)行配置布線。一旦結(jié)束配置布線處理,將計(jì)算出基于實(shí)際配置布線的時(shí)序信息。

★使用EDA工具

配置布線工具

CTS(Clock Tree Synthesis)工具

論邏輯仿真時(shí)序解析(配置布線后)

使用實(shí)際的配置布線結(jié)果,進(jìn)行驗(yàn)證。處理內(nèi)容和配置布線之彰相同。如果結(jié)果沒有問題,將第二次sing-off(簽名發(fā)布),如果有違反的情況,則必須再次進(jìn)行電路修正,反饋到配置布線工程。

Sign-off:就是半導(dǎo)體制造商和用戶就LSI設(shè)計(jì)正確性相互進(jìn)行確認(rèn)并承諾。

ASIC產(chǎn)品開發(fā)流程

ASIC的完成(表面)

ASIC的完成(背面)

I P

IP(Intellectual Property)一般表示專利和知識(shí)產(chǎn)權(quán),但在半導(dǎo)體領(lǐng)域中,表示已經(jīng)設(shè)計(jì)完成的功能電路塊(內(nèi)核、單元),即設(shè)計(jì)資產(chǎn)。可以分成硬件IP和軟件IP,其利用已經(jīng)成為大規(guī)模LSI設(shè)計(jì)效率化的關(guān)鍵。

IP的種類

IP作為設(shè)計(jì)資產(chǎn),大體分為以下兩大類。

·硬件IP(硬件宏)

用于LSI制造的掩模數(shù)據(jù)。

因模擬及配置(布置)使得時(shí)序變?yōu)閲?yán)格的IP。

·軟件IP(軟件宏)

RTL或網(wǎng)絡(luò)表

大部分的數(shù)字邏輯IP。

容易對(duì)應(yīng)設(shè)計(jì)規(guī)則時(shí)代的變遷。

IP的流通和標(biāo)準(zhǔn)界面化的重要性

現(xiàn)在若由一家公司準(zhǔn)備所有的IP,適時(shí)地提供是比較困難的。對(duì)系統(tǒng)機(jī)器生產(chǎn)廠商而言,用于提高功能的附加價(jià)值較高的IP由自己公司開發(fā),除此以外的標(biāo)準(zhǔn)性IP從外部(從半導(dǎo)體供應(yīng)商或IP專業(yè)供應(yīng)商)調(diào)配的體制非常有必要。而且,為了將從不同供應(yīng)商獲得的IP進(jìn)行組合,從而開發(fā)效率良好的系統(tǒng)LSI,需要公開的標(biāo)準(zhǔn)界面,現(xiàn)在除了VSI(Virtual Socket Interface)聯(lián)盟以外,還有幾個(gè)標(biāo)準(zhǔn)化團(tuán)體正在不斷推進(jìn)該進(jìn)程。

使用IP的有效性

隨著LSI的高集成化的同時(shí),集成在1塊芯片上的功能的種類也不斷多樣化。例如,在多媒體相關(guān)系統(tǒng)中,圖像處理、通信控制、數(shù)據(jù)控制、數(shù)據(jù)存儲(chǔ)等多種功能組合在一起。為了將這些功能集成在1塊芯片上,必須混合集成數(shù)字邏輯電路、模擬、存儲(chǔ)器等不同的器件及電路技術(shù)。另一方面,對(duì)系統(tǒng)產(chǎn)品投入市場的交貨期短的要求越來越強(qiáng)。

雖然LSI不斷大規(guī)模化、多功能復(fù)雜化、高性能化,但目前尚處于不允許包括電路設(shè)計(jì)驗(yàn)證在內(nèi)的LSI開發(fā)時(shí)間增大的情況。為了解決這些問題,使用已經(jīng)得到驗(yàn)證的設(shè)計(jì)資產(chǎn)(IP)是極為有效的,可以大幅度削減設(shè)計(jì)時(shí)間。

將IP進(jìn)行組合后的系統(tǒng)LSI

可編程器件(CPLD/FPGA)

可編程器件是指使用RAM或ROM,在可以實(shí)現(xiàn)程序的范圍,使用者可以實(shí)現(xiàn)任意電路的器件。代表性的器件有CPLD、FPGA。

★CPLD(Complex Programmable Logic Device:復(fù)雜可編程邏輯器件)

擁有多個(gè)邏輯塊(PLD塊),可利用內(nèi)部布線網(wǎng)連接任意塊之間的結(jié)構(gòu)。EEPROM、FLASH方式為主流方式。

CPLD的結(jié)構(gòu)

★FPGA(Field Programmable Gate Array:現(xiàn)場可編程門陣列)

是一種同時(shí)包括用戶可以自由設(shè)定、更改功能的正反器等存儲(chǔ)器件在內(nèi)的集成電路,擁有整體可以相互連接的邏輯單元陣列,有2種類型。與CPLD相比,容量較大,適合于大規(guī)模的電路

(基于SRAM)可重復(fù)編程(reprogrammable)

指SRAM決定相互連接或是以檢查表格(LUT)決定邏輯功能的器件,所以可以多次重寫覆蓋。但是,一旦電源斷開,寫入的內(nèi)容不能保存下來,因此采取安裝到線路板時(shí),附上電池或準(zhǔn)備好非揮發(fā)性存儲(chǔ)器,將布線信息保存到內(nèi)部,在接入電源時(shí)裝載該內(nèi)容的方法。

可一次編程(OTP)

以保險(xiǎn)絲互相連接,一旦寫入后,不可以重寫覆蓋。

優(yōu)點(diǎn)

·較短的開發(fā)TAT(周轉(zhuǎn)時(shí)間)

·低廉的開發(fā)費(fèi)

用途

·個(gè)人計(jì)算機(jī)、工程工作站(EWS)、計(jì)算機(jī)相關(guān)設(shè)備

·備通信設(shè)備

·數(shù)字AV設(shè)備

·一般產(chǎn)業(yè)用電子設(shè)備

·家庭用電子設(shè)備、游戲機(jī)等通信機(jī)器

FPGA的結(jié)構(gòu)

復(fù)合器件技術(shù)和混載技術(shù)

沒有明確的定義,但作為復(fù)合器件技術(shù),擁有將雙極型和CMOS邏輯或功率器件等集成在單片電路的制造技術(shù)。混載技術(shù)是指將向系統(tǒng)LSI、ASIC等邏輯LSI中混合安裝存儲(chǔ)器的技術(shù)。

復(fù)合器件技術(shù)

電子設(shè)備中有數(shù)字信號(hào)處理、模擬信號(hào)處理、大功率控制,甚至還有高頻信號(hào)處理等很多信號(hào)處理,使用符合各自用途的半導(dǎo)體。例如,復(fù)合器件技術(shù)是將數(shù)字和模擬信號(hào)處理集成在一塊芯片上、或同樣將數(shù)字信號(hào)處理和功率控制電路集成在一塊芯片上所必須的半導(dǎo)體技術(shù)。

另外還開發(fā)了邏輯IC中混合安裝模擬電路、功率器件(雙極功率晶體管、功率MOSFET、IGBT等)的工藝,這些也可以叫做混載技術(shù),一般情況下也可以將該技術(shù)叫做混合器件技術(shù)。這些代表性器件有BiCMOS、IPD(Intelligent Power Device)等。

這是將模擬信號(hào)處理電路、數(shù)字信號(hào)處理電路、功率器年、存儲(chǔ)器等集成在一塊芯片上的技術(shù),根據(jù)混合安裝的電路、器件不同,有很多種類。

目前,正在開發(fā)系統(tǒng)LSI內(nèi)混合安裝存儲(chǔ)器、顯示用專用LSI的器件、馬達(dá)、螺線管等制動(dòng)器的驅(qū)動(dòng)器、邏輯LSI內(nèi)混合安裝一部分模擬電路等多種混合LSI、復(fù)合器件裝置。

混載技術(shù)

電子設(shè)備很少有只采用一種半導(dǎo)體的應(yīng)用,一般情況下使用很多半導(dǎo)體。例如,如圖所示的PDA(便攜式信息末端)中,只是信號(hào)處理電路中就使用了專用LSI、微控制器、存儲(chǔ)器、驅(qū)動(dòng)器IC等很多半導(dǎo)體。

將這些器件集成在一塊芯片上,可以節(jié)省空間、減小體積、提高可靠性、降低成本等,但必須解決各種半導(dǎo)體制程工藝上的不同而引起的各種問題。

過去,曾經(jīng)在高集成化的存儲(chǔ)器工藝中混合安裝了追求高速化的邏輯,而目前是在同一制程中將存儲(chǔ)器和邏輯集成在一塊芯片上,也就是混合化。

PDA的系統(tǒng)結(jié)構(gòu)

系統(tǒng)LSI和混載技術(shù)

在圖形等圖像處理所必需的系統(tǒng)中混合安裝了存儲(chǔ)器,旨在提高信號(hào)處理速度。

當(dāng)然在系統(tǒng)LSI中也采用了混載技術(shù)。但是,采用了和一些目的不同的其他小規(guī)模邏輯IC使用。也就是除系統(tǒng)LSI以外,都是集成在一塊芯片上,這樣可以提高可靠性、減小體積重量等,但很少是以提高信號(hào)處理上的特性為目的的。

系統(tǒng)LSI為了增加提高信號(hào)處理上的機(jī)能、縮短開發(fā)時(shí)間的目的,積極采用混合工藝。例如,將存儲(chǔ)哭混合在一起后,將原來連接在外部的存儲(chǔ)器不能靈活決定存儲(chǔ)器總線長度變?yōu)榭赡埽⒖梢酝ㄟ^并列處理實(shí)現(xiàn)高速化。也解決了外部連接存儲(chǔ)器時(shí)因布線而產(chǎn)生的信號(hào)延遲問題。

另外,混合安裝閃存,實(shí)現(xiàn)了程序的重復(fù)寫入,從而提高了開發(fā)的靈活性,結(jié)果可以實(shí)現(xiàn)縮短從開發(fā)到大規(guī)模生產(chǎn)的時(shí)間。

微控制器一般為了儲(chǔ)存程序等,搭載ROM或RAM等存儲(chǔ)器,但這個(gè)不叫做存儲(chǔ)器混載技術(shù)。

針對(duì)ITS(高度交通系統(tǒng))的圖像識(shí)別LSI

存儲(chǔ)器混載技術(shù)

使用混合安裝DRAM的系統(tǒng)LSI時(shí),可以削減封裝的總引腳數(shù),除了實(shí)際安裝時(shí)節(jié)省空間、高速化以外,還有很多優(yōu)點(diǎn)。而且,混合安裝閃存后,可以提高IC設(shè)計(jì)的靈活性,實(shí)現(xiàn)QTAT化。

相對(duì)于半導(dǎo)體的內(nèi)部布線而言,外部布線較長,且延遲及與布線有很深關(guān)系的漂移電容較為嚴(yán)重,而且少了與布線的電阻較大的外部存儲(chǔ)器的連接,即可減少延遲。甚至內(nèi)部總線可以在半導(dǎo)體內(nèi)部進(jìn)行自由設(shè)定,因此可以通過靈活的并列處理實(shí)現(xiàn)高速化,特別是在信號(hào)處理方面具有高速化的優(yōu)點(diǎn)。

而且,對(duì)EMI(Electro Magnetic Interference,電磁波干擾)采取對(duì)策方面也非常有效,還可以靈活設(shè)定存儲(chǔ)器容量。像這樣,混合安裝存儲(chǔ)器的LSI不是單純的將外置存儲(chǔ)器內(nèi)置,而是積極用于圖像處理或圖形等超高速信號(hào)處理所必須的電路中。

混合安裝了可以重復(fù)寫入的閃存后,寫入的程序在設(shè)計(jì)后也可以修正,因此可以實(shí)現(xiàn)靈活的開發(fā)量產(chǎn)體制。

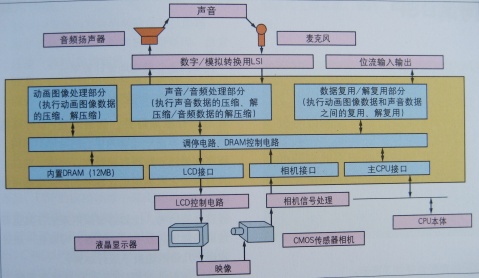

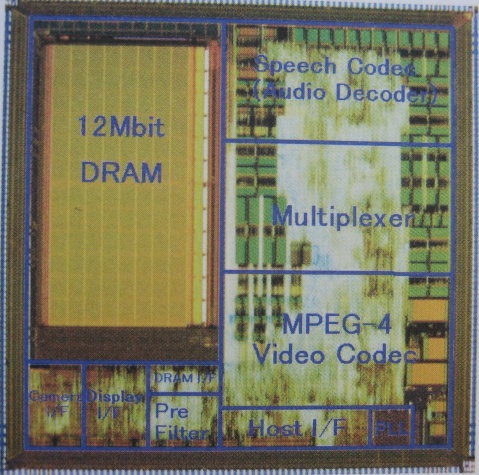

以下照片中的LSI中安裝了個(gè)人電視電話及多媒體瀏覽器所必需的多個(gè)信號(hào)處理部分及12M位DRAM的同時(shí),內(nèi)置用于連接CMOS型固體攝像器件及液晶面板的圖像輸入輸出接口電路。

內(nèi)嵌針對(duì)手機(jī)用MPEG4混合安裝DRAM的系統(tǒng)LSI

SOI、IPD、BiCMOS技術(shù)

作為器件之間的分離,從以往PN接合時(shí)到利用絕緣物氧化硅的制程技術(shù)就是SOI。作為混合功率器件、邏輯、模擬電路的制程技術(shù),有IPD、BiCMOS技術(shù)。

★SOI

SOI(Silicon On Insulator)是一種在氧化硅的絕緣體上形成單結(jié)晶硅的制程技術(shù)。IC可以將很多器件集成在一塊芯片上是因?yàn)閷⒎蛛x各器件之間的P型及N型半導(dǎo)體區(qū)域反偏置,在各器件之間進(jìn)行電氣性絕緣。將PN接合反偏置后進(jìn)行絕緣的方法會(huì)由于寄生器件產(chǎn)生故障、或由于泄漏電流引起各種問題,通過采用絕緣體—氧化硅改善問題的制程就是SOI技術(shù)。

該技術(shù)大致可以分為功率系列和信號(hào)系列。

★IPD(Intelligent Power Device)

IPD是采用可以內(nèi)置邏輯電路、模擬電路以及功率器件的數(shù)百個(gè)到數(shù)千個(gè)器件的較小規(guī)模復(fù)合器件技術(shù)的器件。

應(yīng)用領(lǐng)域有汽車用(ABS、氣囊)、各種馬達(dá)驅(qū)動(dòng)器、燈驅(qū)動(dòng)器、螺線管驅(qū)動(dòng)器等。該制程可以將輸出PW-MOS、Nch MOS、Pch MOS、PNP Tr、NPN Tr、電阻、電容器等所有器件都集成在一塊芯片上,適合于多功能產(chǎn)品。還有采用簡單的制程,在MOS FET中內(nèi)置過電流及過熱保護(hù)功能電路的復(fù)合MOS FET。

★BiCMOS

這是一種將善于處理模擬信號(hào)的雙極器件技術(shù)和善于處理邏輯信號(hào)的CMOS技術(shù)進(jìn)行融合后的制程技術(shù)。

有可以處理功率的高耐壓系列、大功率系列BiCMOS技術(shù)和不能處理大功率的高頻(以及高精度模擬系列)以及可以處理邏輯信號(hào)的高頻BiCMOS技術(shù)。

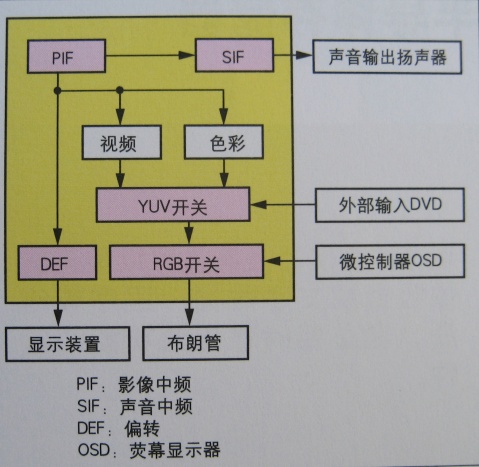

右圖為發(fā)揮后者特征的TV用混合信號(hào)LSI方框圖、芯片照片、結(jié)構(gòu)圖。TV用LSI中也不斷發(fā)展引進(jìn)模擬CMOS技術(shù),以內(nèi)置濾波電路。

IPD的芯片照片

復(fù)合MOSFET(混級(jí)驅(qū)動(dòng)器)

TV信號(hào)處理LSI的方框圖

LSI芯片

?LSI的結(jié)構(gòu)圖

非常好我支持^.^

(2) 100%

不好我反對(duì)

(0) 0%

相關(guān)閱讀:

- [電子說] 芯片為什么用銅作為互聯(lián)金屬?鋁為什么會(huì)被替代呢? 2023-10-12

- [電子說] 芝識(shí)課堂【CMOS邏輯IC基礎(chǔ)知識(shí)】—設(shè)計(jì)大業(yè)始于學(xué)會(huì)讀數(shù)據(jù)表(下) 2023-09-21

- [電子說] 群創(chuàng)3.5 代線轉(zhuǎn)為面板級(jí)封裝,明年底量產(chǎn) 2023-09-18

- [模擬技術(shù)] 什么是FET?FinFET將半導(dǎo)體制程帶入新境界 2023-07-12

- [電子說] Nexperia(安世半導(dǎo)體)率先推出紐扣電池壽命和功率增強(qiáng)器 2023-07-11

- [電子說] 揭秘半導(dǎo)體制程:8寸晶圓與5nm工藝的魅力與挑戰(zhàn) 2023-06-06

- [電子說] 半導(dǎo)體制程280C高溫耐酸堿PI基材雙面膠帶 2023-04-20

- [電子說] CD4051八選一模擬開關(guān) 邏輯IC 模擬電路 2022-05-05

( 發(fā)表人:admin )