采用40G/100G以太網體系結構來支持OTN - FPGA實現100G光傳送網的設計

IEEE802.3ba是正在為40Gbps和100Gbps開發的標準。現階段的目標是:

???? ■只支持全雙工工作

???? ■保留使用802.3MAC標準的802.3/以太網幀格式

???? ■保留當前802.3標準的最小和最大幀長度

???? ■MAC/PLS業務接口支持優于10-12的BER

???? ■為OTN提供相應的支持

???? ■支持40Gbps的MAC數據速率

???? ■提供支持40-Gbps工作的物理層規范,包括:

???? ●在SMF上大于10km

???? ●在OM3MMF上大于100m

???? ●在銅纜上大于10m

???? ●在背板上大于1m

???? ■支持100Gbps的MAC數據速率

???? ■提供支持100-Gbps工作的物理層規范,包括:

???? ●在SMF上大于40km

???? ●在SMF上大于10km

???? ●在OM3MMF上大于100m

???? ●在銅纜上大于10m

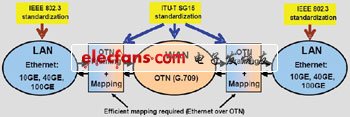

如圖5所示,該工程要在2010年中完成。業界對于100G的實施工作主要集中在傳送網和以太網上。傳送網和以太網標準在100Gbps速率等級上達成一致,這一過程從10G就開始了。

圖5 以太網和光傳送網從10Gbps就開始了融合

StratixIVFPGA為100GbEOTN設計鋪平了道路

目前的業界發展趨勢是使用WDM承載以太網進行數據包傳送,通過IP/MPLS/以太網傳送數據。Altera40-nmStratix?IVFPGA系列的定位非常適合滿足100G以太網和傳送系統設計的性能和系統帶寬要求。StratixIVGTFPGA密度非常高,集成了在單片器件中實現100GbE/光纖通道/RPRMAC功能使用的11.3-Gbps收發器,以及OTN數據包前向糾錯(FEC)、映射和成幀等關鍵處理功能。100GbE的OTU-4標準使用增強FEC(EFEC),必須采用專用算法進行設計才能確保最大限度的發揮光帶寬優勢。由于其優異的架構性能,StratixIVFPGA能夠處理EFEC功能,是OTN系統算法實現和測試的理想平臺。圖6顯示了客戶在設計100GbEOTN設備時怎樣使用StratixIVGTFPGA來實現上面介紹的所有功能。

圖6 100GOTN應用:LAN到WAN

OTN以及對通用客戶端口的需求

OTN含有各種光網絡單元,是高效傳送業務的基礎。獨立的語音、視頻、數據和存儲網絡演進構成公共骨干網,由OTN為其提供服務。OTN設備必須能夠將很多不同類型的業務(以太網、SONET/SDH、ESCON、光纖通道和視頻)映射到這一公共骨干網中。

光設備生產商不斷降低成本,采用跨平臺元器件,因此,靈活映射各種客戶側端口的解決方案得到了應用。FPGA是實現“通用客戶側端口”的主要元件,可以配置支持各種客戶側接口。這樣,單片器件能夠高效用于多種應用中。

為OTN提供靈活的支持

Altera提供適用于OTN體系結構的全系列產品,如表2所示。

表2 Altera器件系列產品

隨著應用的推廣,OTN1和OTN2對成本和功耗越來越敏感。如表3所示,含有嵌入式收發器的AlteraArria?IIGXFPGA提供實現OTN1和OTN2波長轉換器和交叉連接所需要的功能,具有很高的性價比和功效。

表3 為OTN應用提供的AlteraArriaIIGX收發器協議

相對于固定標準產品解決方案,靈活的ArriaIIGXFPGA具有以下優點:

■支持新出現的映射技術,例如,用于將GE映射到OTN所需要的ODU0等。

???? ■可以配置支持各種客戶側接口,采用同一器件實現多種應用。

???? ■只需要重新配置FPGA就可以在同一器件中支持多種FEC和EFEC技術。

在單片FPGA中實現40G波長轉換器設計

波長轉換器(復用轉發器)主要用于將多路低速客戶側信號匯集到高速波長上。它避免了為每一路客戶側低速信號分配獨立的波長,因此,大大提高了WDM頻譜效率。

業界分析師預測,到2013年,40G光端口應用會急劇增長。40GOTN設備越來越大的吞吐量迫切要求進一步改進FEC技術,以便能夠將信號傳送得更遠。由于實現這些EFEC標準需要很大的邏輯容量,因此,在40Gbps速率時將通用客戶端口、映射器、成幀器和EFEC集成到單片器件中難度很大。

然而,AlteraStratixIVGX系列經過規劃,能夠在單片器件中支持40G波長轉換器功能,如圖7所示。StratixIVGXFPGA支持各種數據、存儲、TDM和視頻協議的高效實現,包括GbE、光纖通道(1G、2G、4G)、SONET(OC-N)和SDH(STM-N)等,為這些需求提供所需要的邏輯密度和架構性能。所有列出的協議由Altera直接提供支持或者通過合作伙伴提供支持。

圖7 使用StratixIVFPGA實現波長轉換器

StratixIVGX系列提供32個具有時鐘數據恢復(CDR)電路的收發器,數據速率從600Mbps到8.5Gbps,以及帶有CDR的另外16個收發器,支持從600Mbps到6.5Gbps的數據速率。StratixIVGXFPGA具有530K邏輯單元(LE),能夠支持40G全波長轉換器應用。表4列出了為OTN數據速率提供的StratixIVGX收發器支持。

表4 為OTN應用提供的StratixIVGX收發器協議數據速率

采用StratixIVGTFPGA進行100GOTN設計

最近制定標準的活動圍繞100G光傳送網OTN-4而進行。這些應用需要結合高速收發器和10G收發器來支持所需的吞吐量以及內核性能和邏輯密度,以便實現管理100G數據流量所需要的復雜處理功能。StratixIVGTFPGA支持客戶側10G光接口的直接連接,還可以直接連接至網絡側的100GCFP或者QSFP模塊。這是非常重要的優點,因為它避免了使用外部PHY器件,大大降低了系統復雜度。表5列出了StratixIVGTFPGA支持的協議。

表5 為OTN應用提供的StratixIVGT收發器協議

而且,器件支持綁定接口,例如芯片至模塊和芯片至芯片連接的MLD和SFI-S。因為ITU和OIF的標準還在不斷發展,因此,設備生產商可以先開發早期版本的OTN-4波長轉換器、轉發器和再生器。圖8顯示了怎樣采用StratixIVGT和GX器件實現LANOTN承載100GWAN系統。

圖8 采用StratixIVFPGA實現LANOTN承載100GWAN系統

結論

Altera目前的40-nmFPGA系列產品結合其合作伙伴支撐系統,非常適合實現新出現的100GOTU4標準以及線路速率從2.5Gbps(OTU1)到10Gbps(OTU4)的傳統OTN解決方案。Altera?FPGA涵蓋了光傳送網的所有應用,例如MSPP、P-OTN和運營商級以太網傳送等。

- 第 1 頁:FPGA實現100G光傳送網的設計

- 第 2 頁:采用40G/100G以太網體系結構來支持OTN

本文導航

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [電子說] fpga的開發流程有哪些步驟?fpga和嵌入式系統的區別在哪里? 2023-10-24

- [電子說] 如何創建FPGA控制的機器人手臂? 2023-10-24

- [電子說] 如何創建FPGA控制的機器人手臂 2023-10-24

- [電子說] 用VHDL語言創建一個8位算術邏輯單元(ALU) 2023-10-24

- [電子說] 您的存儲器堆疊了嗎?—賽靈思推出16GB HBM FPGA 2023-10-24

- [電子說] 淺析FPGA設計的安全性 2023-10-24

- [PCB設計] PCB板第一次上電會發生什么事情? 2023-10-24

- [電子說] 基于Corundum架構的100G RDMA網卡設計 2023-10-24

( 發表人:小蘭 )