您正在設計最新的子系統,并且有人告訴您盡可能多地放置100 nF去耦電容,盡可能接近所有集成電路,就像我們在上一顆衛星上所做的那樣。作為一名設計工程師,很自然地質疑這種解耦的定性方法。它的目的是什么?為什么100 nF?其他價值怎么樣?多少個電容?有多接近芯片和方向?

您是否知道在某些情況下,您可以移除PCB上的許多去耦電容,而不會影響子系統的性能或可靠性?如何優化去耦,避免過度設計設計,減少BOM,并提供更便宜,更可靠的硬件,正確的第一次?

為什么要去耦?

配電網絡(PDN)的目的是為其必須提供的每個集成電路提供定義的穩壓電壓。然而,在DC-DC轉換器和其負載之間,PDN內有許多互連;例如跡線,焊盤,過孔,平面,封裝引線,鍵合線等,如下圖所示:

圖1提供FPGA的PDN及其互連的示例。

如果每個芯片的電流消耗恒定,由于各種互連的串聯電阻,這將導致PDN內的恒定IR壓降。然而,集成電路的瞬態需求在每個時鐘周期變化,并且PDN的阻抗包括電感和電容元件。通過復阻抗的快速變化的電流將產生稱為軌道下垂或軌道坍塌的電壓降,如果電容器無法供電,則可能導致紋波過大,調節器不穩定,時序裕度減小,電壓下降或功能故障它的負載與所需的電流。下垂會將噪聲注入電源和接地層,從而在PCB邊緣發出不必要的EMI,而去耦也可以減少這種干擾。

調節器對瞬態電流需求的響應要慢于它所提供的器件的運行速度。在PDN內旁路或去耦電容器的目的是通過存儲在下垂期間釋放的電荷來消除瞬態電壓降。去耦的作用是為每個集成電路提供這種電容,在很寬的頻率范圍內具有最小的寄生阻抗。整個環路電感決定了從PDN到負載的電荷傳輸速度,每個電容器都會引入固有的ESR和ESL,以及不需要的安裝,通孔和平面擴展電感。 PDN設計的目標是通過最小化電感來最大化電容的有效性,從而將阻抗保持在所需帶寬上的目標值以下。這將供電軌的任何變化限制在可接受的規定極限,例如, 5%的波紋。點擊航天工業希望利用需要低電壓,高電流電源軌的超深亞微米集成電路的性能優勢。這些芯片在更快的頻率下工作,并且當它們更頻繁地切換時,每個周期中消耗的能量也更頻繁地消耗。將所有這些結合起來意味著更高的電流將在更短的時間內發生變化,并且可以容忍的相對噪聲量將減少。

多少去耦?

在設計PDN時,目標應該是選擇最小數量的去耦電容,以確保阻抗在所需帶寬內保持低于目標值。

來自直流的低頻在10 kHz時,調節器控制著集成電路看到PDN的阻抗。從10到100 kHz,大容量電解電容和鉭電容提供低阻抗去耦路徑,之后PCB級去耦接管。

離散板級去耦的有效性受到很大影響其整體回路電感包括固有ESR和ESL,以及安裝,通孔和平面擴展電感。在更高的頻率下,PCB的電源和接地層的平行板電容接管以提供低阻抗路徑。原則上,分布式平面電容提供了提供高達GHz頻率的低電感的潛力;然而,由于芯片封裝PDN的串聯電感,PCB級去耦限制在幾百MHz。

通過利用相鄰電源和地平面之間的嵌入電容,即通過增加平面的相對面積通過減小它們的間隔和/或通過使用具有更高相對介電常數的電介質,可以將更寬帶寬上的平面間電容的有效性提高到可以去除許多物理的,離散的去耦電容器的水平。電介質厚度影響平面擴展電感,并且最小化這種間隔降低了電容器的整體安裝電感,使其能夠進一步遠離其負載。然而,在實踐中,ESA的ECSS-Q-ST-70-12C標準規定了最小間隙為100μm(3.9密耳),這限制了嵌入式解耦對ESA任務的有效性。

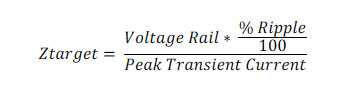

高于幾百MHz,芯片看到的阻抗由片內電容(柵極和電源接地金屬化)決定,而板級去耦將無法將其降低到封裝的固有PDN電感以下。 BR>對于要去耦的每個電源軌,可以通過根據器件數據手冊中規定的最大容許紋波以及瞬態電流計算目標阻抗來啟動PDN的設計:

對于許多組件,僅列出最大功耗,并且可以使用多種方法來推斷峰值瞬態需求,例如 0.5 * Imax 。一些FPGA供應商在地點和路線之后或者從功率預測電子表格中提供更多的定量估計。

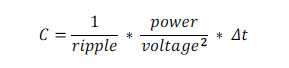

我們還可以通過假設去耦提供在某段時間內必須流動的所有電荷來估算所需的電容總量,Δt:

例如,如果ADC從3.3V電壓軌消耗2W且指定紋波為5%,并且穩壓器在不到10μs內無法響應電壓變化,那么我們需要提供37μF的去耦。低于此值,電容器上的電壓下降將超過允許的5%紋波。

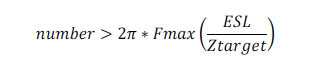

對于每個電壓軌,還可以估算并聯所需的最小電容數,以滿足目標阻抗直至最大頻率:

等式表明,為了減少電容器的數量,必須減少ESL。每個電容器的環路電感越低,在更高頻率下實現目標阻抗所需的電感越少。具有較低固有ESL的較小電容器是可用的,例如, AVX將在今年晚些時候提供符合空間要求的0402,并且應盡一切努力減少整體回路電感,即附件,通孔和平面擴展電感的幾何形狀。

設計人員通常只會增加電容器的數量希望通過并聯添加更多電容來降低環路電感。然而,當電容器緊密間隔時,由于通孔之間的互感,在平面和電容器焊盤之間看到的電感不會降低為1/N,這是標準做法。

-

電容

+關注

關注

100文章

6241瀏覽量

153607 -

PCB打樣

+關注

關注

17文章

2977瀏覽量

22408 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28496 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43804

發布評論請先 登錄

ADS5474模數轉換器的VCM和VREF引腳在什么情況下使用?

TAS5721有個Without MCLK的功能,這個在什么情況下可以沒有MCLK?

什么情況下OPA541容易損壞?

為什么電容在低電壓情況下會發熱

在什么情況下以移除PCB上的許多去耦電容

在什么情況下以移除PCB上的許多去耦電容

評論