隨著工藝的進步,邏輯集成電路的工作電壓越來越低,速度也越來越高。很多標準邏輯器件的接口驅動器都是對稱的上下拉結構,只要相應位置的電壓低于某個值或高于某個值,我們就可以得到確切的邏輯0或邏輯1狀態(tài)。但是,隨著電路工作頻率的提高,這種簡單的邏輯判斷方法有時候就行不通了,于是就有新的邏輯接口層出不窮地冒出來,這些新的接口通常都有一個很重要的特征:它們是對稱的,外電路也是對稱的,下面的內容算是這樣的一個例子。

DDR SDRAM是SDRAM的升級版,它可以在時鐘信號的上升沿和下降沿各進行一次數據傳輸,因而可以在相同的時鐘頻率下將數據吞吐速率提升一倍。隨著DDR存儲器的潛力被不斷挖掘,我們已經見到了DDR、DDR2、DDR3、DDR4和其它的一些特別版本,它們的工作電壓越來越低,時鐘速度也越來越快,但它們所采用的數據接口的邏輯卻沒有什么大的變化。實際上,這些存儲器的數據接口所采用的邏輯都是一種被稱為SSTL的邏輯,這個稱呼是“Stub Series Terminated Logic”的首字母縮寫。我實在不知道要如何用中文來準確地表達這個稱呼,因為我不知道定義者是如何定義Stub的意義的,雖然我可以憑自己的猜測進行估計,但我覺得最好還是不要這樣做。對此感興趣的讀者可以參考一個來自百度百科的翻譯,它把SSTL稱之為“短截線串聯(lián)端接邏輯”。

SSTL的第一個版本是在1996年發(fā)布的,它所針對的應用是工作頻率高于125MHz的存儲器,由于工作電壓為3.3V,這個版本被稱為SSTL-3。SSTL的后續(xù)版本有SSTL-2、SSTL-18和SSTL-15,它們分別針對工作電壓為2.5V、1.8V和1.5V的應用。

從驅動器的角度來看,SSTL的電路結構是這樣的:

驅動器的輸出是VOUT,經過串聯(lián)電阻RS和傳輸線以后到達接收器一側的電壓是VIN。很顯然,VOUT和VIN的值與驅動器的驅動能力有關,也和驅動器的供電電壓VDDQ 、串聯(lián)電阻RS 、終端匹配電阻RT和終端電壓VTT的值有關。

對于SSTL-3來說,VDDQ=3.3V,VTT的取值是VDDQ的0.45倍,它被設定為1.5V。其他版本的SSTL都將VTT設定為VDDQ的0.5倍。

接收器在判斷接收到的信號是高電平還是低電平的時候需要一個參考電壓VREF,VREF的值和VTT的值是相同的。只要VIN電壓高于VREF某個電壓值即可判定輸入為1,VIN電壓低于VREF某個電壓值即可判定輸入為0。由于高速傳輸的信號很容易發(fā)生畸變,也很容易受到干擾,所以VIN高于VREF或低于VREF的量在很小的情況下就需要接收器判斷出數據的真實值。在這里,數據0和1的電壓相對于VREF基本上是對稱的,與VTT之間的關系也是如此。

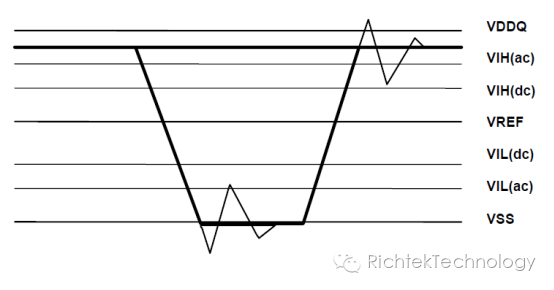

上圖顯示的是VIN的可能的波形的樣子。當VIN電壓高于VIH(dc)的時候,VIN的電壓所代表的就是數據1;當VIN電壓低于VIL(dc)的時候,VIN的電壓所代表的就是數據0。疊加在波形上的振蕩波形被稱為交流部分,它們屬于干擾,是我們不希望出現(xiàn)的東西,所以在標準中就規(guī)定了這些信號的幅度限制。很顯然,如果交流部分的幅度下探到VIH(dc)以下或上探到VIL(dc)以上,則數據1或0的狀態(tài)就受到了破壞,因而對它們的限制是很合理的。

由于VREF=VTT,在數據為1時就有電流從VIN處經電阻RT流入VTT,在數據為0時就有電流從VTT經電阻RT流入VIN處。

很顯然,電流從VTT流出將導致VTT電壓的降低,電流流入VTT則將導致其電壓的升高。為了保證VTT電壓的穩(wěn)定,為VTT供電的電源管理電路需要在VTT電壓降低時向VTT提供電荷(吐出電流),在VTT電壓升高時將VTT處的電荷吸走(吸入電流),實現(xiàn)這樣功能的電源器件被稱為DDR存儲器數據總線終端電壓調節(jié)器,這個稱呼實在是太啰嗦了,所以比較簡單的說法是DDR終端電壓調節(jié)器或DDR終端穩(wěn)壓器。我自己會比較喜歡DDR終端電壓調節(jié)器這個說法,我很難說清楚為什么是這樣,但我有一種感覺是來源于這種器件與普通的穩(wěn)壓器是有很大的區(qū)別的緣故。

DDR終端電壓調節(jié)器的電流吸入和吐出的能力需要有多高呢?這是可以進行估算的,估算的時候需要考慮很多因素:總線的寬度(同時傳輸的數據的位數),需要終端匹配的存儲器的數量(如果有多個存儲器模組,總線就會有多個分支,每個分支的終端都需要進行匹配處理),VDDQ和VREF的高低以及終端匹配電阻RT的大小,信號的實際幅度(VIN的電壓與VTT之間的壓差直接影響著電流的大小)。

關于RT的大小,這其實是與總線的阻抗有關的,其取值通常為50Ω,但另外一種配置就是25Ω,這將導致電流增加一倍的效果。

早期的PC在解決這個問題的時候都是采用大電流的Buck架構開關轉換器來完成DDR存儲器的終端匹配電源供應的,我猜想這是基于如下的考慮:當所有的數據線都處于0或是1的狀態(tài)時,VTT電源要吐出或是吸入的電流是巨大的;工作在PWM模式下的Buck既可以吐出電流,也可以吸入電流,它吸入的電流通過Boost的方式被送入Buck的輸入端,還可以起到回收能源的效果。

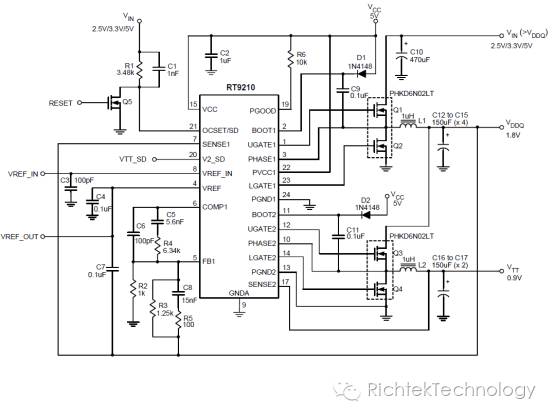

上圖截取自RT9210的規(guī)格書,這是立锜的一款老產品,其中就含有兩組Buck,可以分別為DDR存儲器提供VDDQ和VTT供應,DDR存儲器需要的VREF等電壓也一并提供,但是,這樣的產品卻不是今天DDR存儲器供電的常見選擇。

常見的選擇是這樣的:

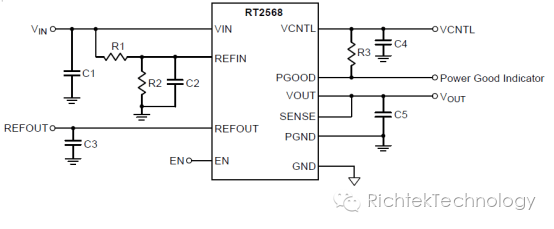

這是為VTT和VREF供電的電路圖,所選型號是RT2568,這是一款工業(yè)級的DDR終端電壓調節(jié)器,具有3A的電流吐納能力。其內部電路框圖是這樣的:

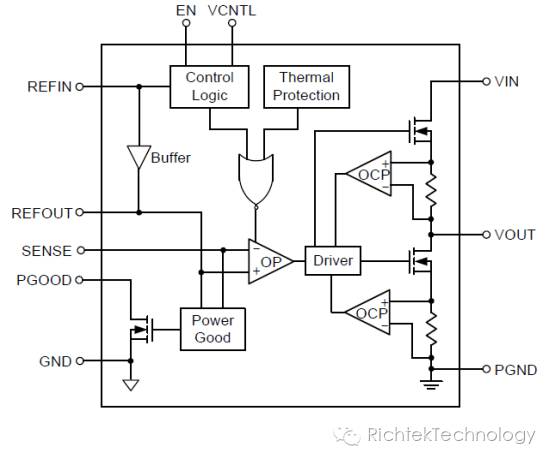

從中可以看到,從SENSE端檢測到的輸出電壓VOUT(也就是我們需要的VTT)被拿來與經過緩沖處理的REFIN即REFOUT進行比對,如果發(fā)現(xiàn)VOUT高了,輸出部分的下面那個MOSFET就會導通將VOUT端的電荷吸走以降低其電壓,反之則導通上面那個MOSFET讓電流從VIN處流入VOUT使輸出電壓上升,從而使輸出電壓VOUT穩(wěn)定在和REFIN相同的電壓上。

本來過去都是使用Buck來完成此功能的,現(xiàn)在大家都選擇使用這種線性的方式,這種轉換是如何完成的呢?要了解這一點,需要我們將目光投射到十幾年前的***。

1998年9月,立锜科技在***的新竹成立,來自各種不同專業(yè)的大約15個人一起成立了一家全新的IC設計公司,定位于專業(yè)的模擬IC設計方向,啟動資金為大家湊集起來的500萬元新臺幣。由于這個時期是PC代工業(yè)在***正紅火的時候,他們看上了PC應用中的電源管理需求,決心進入其中為大家服務并希望能藉此從中分到一杯羹。

在成立的當年(1998年),立锜的第一顆產品RT34063A就開發(fā)完成并投入量產。

第二年(1999年),立锜自制的測試機臺RTT正式啟用。同時,PC主機板的四合一PWM IC和ACPI 控制器也開發(fā)完成并投入生產。對于IC設計公司來說,測試機臺的投入在成本上是排在第二位的,所以,立锜自制測試機臺的做法對于降低成本、提升競爭力是很有幫助的。

第三年,也就是2000年,立锜遷入新的公司地址,并且通過了ISO2001的認證,用于USB端口的保護IC也上市了。與此同時,他們對DDR存儲器終端電壓調節(jié)器要采用Buck來完成的做法產生了懷疑,他們認為根本不需要那么大的電流吐納能力就可以滿足實際應用的需要,因為實際應用中出現(xiàn)數據總線上的數據同時為0或同時為1的機會是極少的。只要有0和1同時出現(xiàn),流過RT的電流就會有相互抵消的效果。即使同時為0或1的數據會偶然出現(xiàn),其延續(xù)時間也極短,由此造成的VTT電壓波動是很小的,而且很容易被電容的儲能能力彌補,于是乎一顆劃時代的產品就出現(xiàn)在了這個世界上,它的型號是RT9173。直至今日,RT9173仍在生產中,你還可以從立锜科技的官網上查看到它的規(guī)格書。

RT9173的出現(xiàn)對市場的影響是巨大的。與Buck相比,它實在是太簡單了,成本差異巨大,所以迅速獲得了市場的認可,成為立锜在最短時間內累計出貨量超過1億顆的產品。而在這個時候,我還沒有進入立锜,甚至還沒有進入IC這個行業(yè)。

在我進入立锜以后,有人對我說后來的立锜上市就是因為RT9173,因為它為立锜賺了太多的錢。我很難說這一傳說所說的是否是事實,因為其實在RT9173出現(xiàn)之前立锜就已經有了很多好產品,而在2003年上市以前我在深圳推給客戶的產品還有很多強大的東西,關心我們的微信號的老朋友們在我過去的文章中已經多多少少看到過一些,所以我覺得把所有的功勞都放在RT9173上是有點過頭的,但它的功勞肯定是大大的。

RT9173的設計是有專利的,它也是立锜的第一顆擁有專利的產品。但是,那時候的立锜還太過弱小,對于專利的理解也還不到位,所以,它的專利文件在寫法上太過具體,其覆蓋面積實在太小,保護自己的作用實在是不大,所以,后來的市場上就出現(xiàn)了很多和RT9173長得一模一樣的產品。我不知道那些大公司抄襲小公司的產品是從何時開始的,但這大概是算一例吧,這也是立锜第一次成為被模仿者,而這對立锜來說還僅僅是個開頭。

-

接收器

+關注

關注

15文章

2565瀏覽量

73611 -

數據接口

+關注

關注

1文章

83瀏覽量

18972 -

調節(jié)器

+關注

關注

5文章

876瀏覽量

47536

發(fā)布評論請先 登錄

LM317可調三端正電壓調節(jié)器英文手冊

如何測試LDO電壓調節(jié)器性能

LDO電壓調節(jié)器使用指南 LDO與降壓轉換器的區(qū)別

78L12正電壓調節(jié)器規(guī)格書

PGA309電壓輸出可編程傳感器調節(jié)器

利用寬輸入電壓降壓調節(jié)器創(chuàng)建分軌電源

關于DDR終端電壓調節(jié)器的性能分析和應用

關于DDR終端電壓調節(jié)器的性能分析和應用

評論