與電路優化相關的組件成本通常很少或沒有增加,但很少有工程師花時間和麻煩來優化他們的設計。很容易解釋這個明顯的悖論:優化設計需要相當大的努力。工程師必須設計符合規格的電路,但您可以增強指定或非指定的參數,例如抗噪聲,功耗和穩定性,而不會犧牲設計規范或電路簡單性。通常,選擇正確的元件值是電路優化的唯一要求。

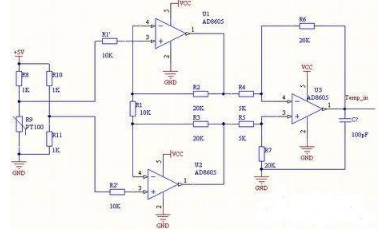

使用單晶體管線路接收器作為應用示例(圖1)。該示例指定輸入電壓電平并添加虛擬變量,負噪聲抑制(NNR)和正噪聲抑制(PNR),以進行優化。您可以將NNR添加到高電平輸入信號,以模擬將信號拉低的噪聲。您將PNR添加到低電平輸入信號。 V INH 和V INL 是高電平和低電平指定輸入信號,I DL 是二極管漏電流,I B 是基極電流,V BE 是基極 - 發射極電壓降。開啟和關閉方程分別如下。

圖2顯示了兩個方程(R 1 與R 2 )在同一圖表上。 PNR是公式1中的變量,NNR是公式2中的變量。噪聲抑制曲線在可能的解決方案中相交,并且存在許多解決方案。在這個例子中,我選擇2.2V的相同噪聲抑制有兩個原因。首先,沒有任何信息表明應該歪曲噪音。其次,2.2V是可獲得的最大等噪聲抑制。

2.2V噪聲抑制曲線上的任何電阻比都是一個解決方案,因為曲線幾乎是一致的。您可以通過選擇最高值的電阻來收集另一種優化程度;該解決方案可實現最低功耗。上升和下降時間不是問題,這個因素有助于提高抗噪性,因為我可以添加過濾器。 R 1 被分成兩個幾乎相等的電阻器,電容器從結到地連接,從而形成噪聲濾波器。時間證明這個電路是一個防彈界面。

優化需要一些思考,正確放置虛擬變量,計算和繪制消耗的設計時間。這一次是一個小小的犧牲,考慮到31年后,沒有人抱怨界面有問題。

在單頁專欄中難以理解數學,所以我將發送一份副本這份13分鐘的手寫設計審查報告給任何發送66美分加蓋郵票,自我解決的9X12英寸的人。德州儀器公司的信封,2685 CR 564,Bushnell,FL 33513。

-

電路設計

+關注

關注

6701文章

2530瀏覽量

213556 -

PCB打樣

+關注

關注

17文章

2977瀏覽量

22391 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28484 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43794

發布評論請先 登錄

請問有做PCB電路設計優化檢查嗎

基于PSPICE的電路優化設計

TLV3501過零比較器電路設計

TLV3501滯回比較器電路設計

如何優化您的電路設計

如何優化您的電路設計

評論