萊迪思半導體提供可編程邏輯器件和軟件設計工具。其ispVM系統是一個編程引擎,支持 IEEE-1532 標準,用于系統內配置。

同時編程多個邏輯設備

將邊界掃描測試應用于組裝電路板的相同ScanWorks系統現在也可以同時編程多個板載邏輯器件。這可以縮短編程時間并提高制造效率。實際上,ASSET的基準測試顯示編程時間可減少30%或更多。

此時,具有1532并發編程的ScanWorks已在通信設備供應商 Alcatel 。 ASSET的ScanWorks邊界掃描測試和ISP環境目前也被 Cisco,Lucent Technologies,Agilent Technologies,Hewlett-Packard,Ericsson,Intel,Raytheon,Rockwell Collins等公司使用。

“根據我們的經驗,我們可以看到ScanWorks與IEEE-1532的并發編程功能有可能節省大量時間,”阿爾卡特測試工程師Doug Way說。他還是開發IEEE-1532規范的IEEE工作組的成員。 “將IEEE-1532功能集成到ScanWorks中是無縫的,”Way補充道。 “因此,ScanWorks使IEEE-1532易于使用。”

在線測試

“工作組試圖解決以下問題邊界掃描社區的系統配置需求,以及 PLD (可編程邏輯器件)工具供應商和 ICT (在線測試)系統的供應商,“ ASSET技術營銷經理Dave Bonnett和IEEE-1532工作組副主席。 “基于行業標準,1532方法可以通過各種測試技術進行部署。”

Bonnett引用了一些例子,您可以在開發期間在ScanWorks工作站上使用1532,然后制造和測試工程師也可以在ScanWorks制造站上進入1532。 “此外,”Bonnett說,“技術人員可以在ScanWorks上的大批量生產中使用1532用于 Agilent 3070 ICT系統。”

IEEE-1532標準

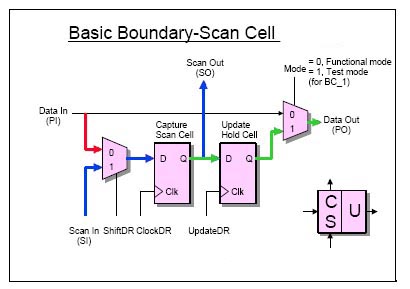

關于IEEE-1532標準的一個詞。它使用電路板上的JTAG基礎設施來訪問板載PLD和 FPGA (現場可編程門陣列),以將編程或配置數據加載到它們中。如果存在多個IEEE-1532可編程設備,則可以同時配置它們,從而大大減少了逐個編程每個設備所需的時間。

借助萊迪思的ispVM系統編程引擎,無論設備供應商如何,ScanWorks都能夠對任何符合1532標準的PLD或FPGA進行編程。

此外,ispVM系統引擎無縫集成到ScanWorks中,因此IEEE-1532的系統內配置功能與所有其他ScanWorks操作具有相同的外觀。此外,ispVM系統使用與其他ScanWorks操作相同的邊界掃描路徑描述,并且能夠將配置數據定位到系統層次結構中任何級別的PLD。

執行IEEE-1532編程操作,例如,您設置標準中定義的選項;這些保存為ScanWorks 操作。然后,此操作可應用于包含IEEE-1532可編程設備的電路板,同時在制造過程中應用其他ScanWorks測試和編程操作。

-

可編程邏輯器件

+關注

關注

5文章

145瀏覽量

30597 -

萊迪思半導體

+關注

關注

0文章

56瀏覽量

16579

發布評論請先 登錄

萊迪思半導體四季度財報發布,營收略高于市場預期

萊迪思推出全新Avant? 30和Avant? 50器件

可編程混合信號技術彌補邏輯IC的成本與密度空白

今日看點丨 UALink聯盟正式成立,與英偉達NVLink展開競爭;FPGA大廠萊迪思半導體宣布重組

德州儀器推出全新可編程邏輯產品系列

德州儀器 (TI) 全新可編程邏輯產品系列助力工程師在數分鐘內完成從概念到原型設計的整個過程

萊迪思半導體可提供可編程邏輯器件和軟件設計工具

萊迪思半導體可提供可編程邏輯器件和軟件設計工具

評論