一、資料輸入階段

1.在流程上接收到的資料是否齊全(包括:原理圖、*.brd文件、料單、PCB設(shè)計(jì)說明以及PCB設(shè)計(jì)或更改要求、標(biāo)準(zhǔn)化要求說明、工藝設(shè)計(jì)說明文件)

2.確認(rèn)PCB模板是最新的

3. 確認(rèn)模板的定位器件位置無誤

4.PCB設(shè)計(jì)說明以及PCB設(shè)計(jì)或更改要求、標(biāo)準(zhǔn)化要求說明是否明確

5.確認(rèn)外形圖上的禁止布放器件和布線區(qū)已在PCB模板上體現(xiàn)

6.比較外形圖,確認(rèn)PCB所標(biāo)注尺寸及公差無誤, 金屬化孔和非金屬化孔定義準(zhǔn)確

7.確認(rèn)PCB模板準(zhǔn)確無誤后最好鎖定該結(jié)構(gòu)文件,以免誤操作被移動(dòng)位置

二、布局后檢查階段

a.器件檢查

8, 確認(rèn)所有器件封裝是否與公司統(tǒng)一庫(kù)一致,是否已更新封裝庫(kù)(用viewlog檢查運(yùn)行結(jié)果)如果不一致,一定要Update Symbols

9, 母板與子板,單板與背板,確認(rèn)信號(hào)對(duì)應(yīng),位置對(duì)應(yīng),連接器方向及絲印標(biāo)識(shí)正確,且子板有防誤插措施,子板與母板上的器件不應(yīng)產(chǎn)生干涉

10, 元器件是否100% 放置

11, 打開器件TOP和BOTTOM層的place-bound, 查看重疊引起的DRC是否允許

12, Mark點(diǎn)是否足夠且必要

13, 較重的元器件,應(yīng)該布放在靠近PCB支撐點(diǎn)或支撐邊的地方,以減少PCB的翹曲

14, 與結(jié)構(gòu)相關(guān)的器件布好局后最好鎖住,防止誤操作移動(dòng)位置

15, 壓接插座周圍5mm范圍內(nèi),正面不允許有高度超過壓接插座高度的元件,背面不允許有元件或焊點(diǎn)

16, 確認(rèn)器件布局是否滿足工藝性要求(重點(diǎn)關(guān)注BGA、PLCC、貼片插座)

17, 金屬殼體的元器件,特別注意不要與其它元器件相碰,要留有足夠的空間位置

18, 接口相關(guān)的器件盡量靠近接口放置,背板總線驅(qū)動(dòng)器盡量靠近背板連接器放置

19, 波峰焊面的CHIP器件是否已經(jīng)轉(zhuǎn)換成波峰焊封裝,

20, 手工焊點(diǎn)是否超過50個(gè)

21, 在PCB上軸向插裝較高的元件,應(yīng)該考慮臥式安裝。留出臥放空間。并且考慮固定方式,如晶振的固定焊盤

22, 需要使用散熱片的器件,確認(rèn)與其它器件有足夠間距,并且注意散熱片范圍內(nèi)主要器件的高度

b.功能檢查

23, 數(shù)模混合板的數(shù)字電路和模擬電路器件布局時(shí)是否已經(jīng)分開,信號(hào)流是否合理

24, A/D轉(zhuǎn)換器跨模數(shù)分區(qū)放置。

25, 時(shí)鐘器件布局是否合理

26, 高速信號(hào)器件布局是否合理

27, 端接器件是否已合理放置(源端匹配串阻應(yīng)放在信號(hào)的驅(qū)動(dòng)端;中間匹配的串阻放在中間位置;終端匹配串阻應(yīng)放在信號(hào)的接收端)

28, IC器件的去耦電容數(shù)量及位置是否合理

29, 信號(hào)線以不同電平的平面作為參考平面,當(dāng)跨越平面分割區(qū)域時(shí),參考平面間的連接電容是否靠近信號(hào)的走線區(qū)域。

30, 保護(hù)電路的布局是否合理,是否利于分割

31, 單板電源的保險(xiǎn)絲是否放置在連接器附近,且前面沒有任何電路元件

32, 確認(rèn)強(qiáng)信號(hào)與弱信號(hào)(功率相差30dB)電路分開布設(shè)

33, 是否按照設(shè)計(jì)指南或參考成功經(jīng)驗(yàn)放置可能影響EMC實(shí)驗(yàn)的器件。如:面板的復(fù)位電路要稍靠近復(fù)位按鈕

c.發(fā)熱

34, 對(duì)熱敏感的元件(含液態(tài)介質(zhì)電容、晶振)盡量遠(yuǎn)離大功率的元器件、散熱器等熱源

35, 布局是否滿足熱設(shè)計(jì)要求,散熱通道(根據(jù)工藝設(shè)計(jì)文件來執(zhí)行)

d.電源

36, 是否IC電源距離IC過遠(yuǎn)

37, LDO及周圍電路布局是否合理

38, 模塊電源等周圍電路布局是否合理

39, 電源的整體布局是否合理

e.規(guī)則設(shè)置

40, 是否所有仿真約束都已經(jīng)正確加到Constraint Manager中

41, 是否正確設(shè)置物理和電氣規(guī)則(注意電源網(wǎng)絡(luò)和地網(wǎng)絡(luò)的約束設(shè)置)

42, Test Via、Test Pin的間距設(shè)置是否足夠

43, 疊層的厚度和方案是否滿足設(shè)計(jì)和加工要求

44, 所有有特性阻抗要求的差分線阻抗是否已經(jīng)經(jīng)過計(jì)算,并用規(guī)則控制

三、布線后檢查階段

f.數(shù)模

45, 數(shù)字電路和模擬電路的走線是否已分開,信號(hào)流是否合理

46, A/D、D/A以及類似的電路如果分割了地,那么電路之間的信號(hào)線是否從兩地之間的橋接點(diǎn)上走(差分線例外)?

47, 必須跨越分割電源之間間隙的信號(hào)線應(yīng)參考完整的地平面。

48, 如果采用地層設(shè)計(jì)分區(qū)不分割方式,要確保數(shù)字信號(hào)和模擬信號(hào)分區(qū)布線。

g.時(shí)鐘和高速部分

49, 高速信號(hào)線的阻抗各層是否保持一致

50, 高速差分信號(hào)線和類似信號(hào)線,是否等長(zhǎng)、對(duì)稱、就近平行地走線?

51, 確認(rèn)時(shí)鐘線盡量走在內(nèi)層

52, 確認(rèn)時(shí)鐘線、高速線、復(fù)位線及其它強(qiáng)輻射或敏感線路是否已盡量按3W原則布線

53, 時(shí)鐘、中斷、復(fù)位信號(hào)、百兆/千兆以太網(wǎng)、高速信號(hào)上是否沒有分叉的測(cè)試點(diǎn)?

54, LVDS等低電平信號(hào)與TTL/CMOS信號(hào)之間是否盡量滿足了10H(H為信號(hào)線距參考平面的高度)?

55, 時(shí)鐘線以及高速信號(hào)線是否避免穿越密集通孔過孔區(qū)域或器件引腳間走線?

56, 時(shí)鐘線是否已滿足(SI約束)要求(時(shí)鐘信號(hào)走線是否做到少打過孔、走線短、參考平面連續(xù),主要參考平面盡量是GND;若換層時(shí)變換了GND主參考平面層,在離過孔200mil范圍之內(nèi)是GND過孔) 若換層時(shí)變換不同電平的主參考平面,在離過孔200mil范圍之內(nèi)是否有去耦電容)?

57, 差分對(duì)、高速信號(hào)線、各類BUS是否已滿足(SI約束)要求

h.EMC與可靠性

58, 對(duì)于晶振,是否在其下布一層地?是否避免了信號(hào)線從器件管腳間穿越?對(duì)高速敏感器件,是否避免了信號(hào)線從器件管腳間穿越?

59, 單板信號(hào)走線上不能有銳角和直角(一般成 135 度角連續(xù)轉(zhuǎn)彎,射頻信號(hào)線最好采用圓弧形或經(jīng)過計(jì)算以后的切角銅箔)

60, 對(duì)于雙面板,檢查高速信號(hào)線是否與其回流地線緊挨在一起布線;對(duì)于多層板,檢查高速信號(hào)線是否盡量緊靠地平面走線

61, 對(duì)于相鄰的兩層信號(hào)走線,盡量垂直走線

62, 避免信號(hào)線從電源模塊、共模電感、變壓器、濾波器下穿越

63, 盡量避免高速信號(hào)在同一層上的長(zhǎng)距離平行走線

64, 板邊緣還有數(shù)字地、模擬地、保護(hù)地的分割邊緣是否有加屏蔽過孔?多個(gè)地平面是否用過孔相連?過孔距離是否小于最高頻率信號(hào)波長(zhǎng)的1/20?

65, 浪涌抑制器件對(duì)應(yīng)的信號(hào)走線是否在表層短且粗?

66, 確認(rèn)電源、地層無孤島、無過大開槽、無由于通孔隔離盤過大或密集過孔所造成的較長(zhǎng)的地平面裂縫、無細(xì)長(zhǎng)條和通道狹窄現(xiàn)象

67, 是否在信號(hào)線跨層比較多的地方,放置了地過孔(至少需要兩個(gè)地平面)

i.電源和地

68, 如果電源/地平面有分割,盡量避免分割開的參考平面上有高速信號(hào)的跨越。

69, 確認(rèn)電源、地能承載足夠的電流。過孔數(shù)量是否滿足承載要求,(估算方法:外層銅厚1oz時(shí)1A/mm線寬,內(nèi)層0.5A/mm線寬,短線電流加倍)

70, 對(duì)于有特殊要求的電源,是否滿足了壓降的要求

71, 為降低平面的邊緣輻射效應(yīng),在電源層與地層間要盡量滿足20H原則。(條件允許的話,電源層的縮進(jìn)得越多越好)。

72, 如果存在地分割,分割的地是否不構(gòu)成環(huán)路?

73, 相鄰層不同的電源平面是否避免了交疊放置?

74, 保護(hù)地、-48V地及GND的隔離是否大于2mm?

75, -48V地是否只是-48V的信號(hào)回流,沒有匯接到其他地?如果做不到請(qǐng)?jiān)趥渥谡f明原因。

76, 靠近帶連接器面板處是否布10~20mm的保護(hù)地,并用雙排交錯(cuò)孔將各層相連?

77, 電源線與其他信號(hào)線間距是否距離滿足安規(guī)要求?

j.禁布區(qū)

78, 金屬殼體器件和散熱器件下,不應(yīng)有可能引起短路的走線、銅皮和過孔

79, 安裝螺釘或墊圈的周圍不應(yīng)有可能引起短路的走線、銅皮和過孔

80, 設(shè)計(jì)要求中預(yù)留位置是否有走線

81, 非金屬化孔內(nèi)層離線路及銅箔間距應(yīng)大于0.5mm(20mil),外層0.3mm(12mil),單板起拔扳手軸孔內(nèi)層離線路及銅箔間距應(yīng)大于2mm(80mil)

82, 銅皮和線到板邊 推薦為大于2mm 最小為0.5mm

83, 內(nèi)層地層銅皮到板邊 1 ~ 2 mm, 最小為0.5mm

k.焊盤出線

84, 對(duì)于兩個(gè)焊盤安裝的CHIP元件(0805及其以下封裝),如電阻、電容,與其焊盤連接的印制線最好從焊盤中心位置對(duì)稱引出,且與焊盤連接的印制線必須具有一樣的寬度,對(duì)于線寬小于0.3mm(12mil)的引出線可以不考慮此條規(guī)定

85, 與較寬印制線連接的焊盤,中間最好通過一段窄的印制線過渡?(0805及其以下封裝)

86, 線路應(yīng)盡量從SOIC、PLCC、QFP、SOT等器件的焊盤的兩端引出

l.絲印

87, 器件位號(hào)是否遺漏,位置是否能正確標(biāo)識(shí)器件

88, 器件位號(hào)是否符合公司標(biāo)準(zhǔn)要求

89, 確認(rèn)器件的管腳排列順序, 第1腳標(biāo)志,器件的極性標(biāo)志,連接器的方向標(biāo)識(shí)的正確性

90, 母板與子板的插板方向標(biāo)識(shí)是否對(duì)應(yīng)

91, 背板是否正確標(biāo)識(shí)了槽位名、槽位號(hào)、端口名稱、護(hù)套方向

92, 確認(rèn)設(shè)計(jì)要求的絲印添加是否正確

93, 確認(rèn)已經(jīng)放置有防靜電和射頻板標(biāo)識(shí)(射頻板使用)

m.編碼/條碼

94, 確認(rèn)PCB編碼正確且符合公司規(guī)范

95, 確認(rèn)單板的PCB編碼位置和層面正確(應(yīng)該在A面左上方,絲印層)

96, 確認(rèn)背板的PCB編碼位置和層面正確(應(yīng)該在B右上方,外層銅箔面)

97, 確認(rèn)有條碼激光打印白色絲印標(biāo)示區(qū)

98, 確認(rèn)條碼框下面沒有連線和大于0.5mm導(dǎo)通孔

99, 確認(rèn)條碼白色絲印區(qū)外20mm范圍內(nèi)不能有高度超過25mm的元器件

n.過孔

100, 在回流焊面,過孔不能設(shè)計(jì)在焊盤上。(正常開窗的過孔與焊盤的間距應(yīng)大于0.5mm (20mil),綠油覆蓋的過孔與焊盤的間距應(yīng)大于0.1 mm (4mil),方法:將Same Net DRC打開,查DRC,然后關(guān)閉Same Net DRC)

101, 過孔的排列不宜太密,避免引起電源、地平面大范圍斷裂

102, 鉆孔的過孔孔徑最好不小于板厚的1/10

o.工藝

103, 器件布放率是否100%,布通率是否100%(沒有達(dá)到100%的需要在備注中說明)

104, Dangling線是否已經(jīng)調(diào)整到最少,對(duì)于保留的Dangling線已做到一一確認(rèn);

105, 工藝科反饋的工藝問題是否已仔細(xì)查對(duì)

p.大面積銅箔

106, 對(duì)于Top、bottom上的大面積銅箔,如無特殊的需要,應(yīng)用網(wǎng)格銅[單板用斜網(wǎng),背板用正交網(wǎng),線寬0.3mm (12 mil)、間距0.5mm (20mil)]

107, 大面積銅箔區(qū)的元件焊盤,應(yīng)設(shè)計(jì)成花焊盤,以免虛焊;有電流要求時(shí),則先考慮加寬花焊盤的筋,再考慮全連接

108, 大面積布銅時(shí),應(yīng)該盡量避免出現(xiàn)沒有網(wǎng)絡(luò)連接的死銅(孤島)

109, 大面積銅箔還需注意是否有非法連線,未報(bào)告的DRC

q.測(cè)試點(diǎn)

110, 各種電源、地的測(cè)試點(diǎn)是否足夠(每2A電流至少有一個(gè)測(cè)試點(diǎn))

111, 確認(rèn)沒有加測(cè)試點(diǎn)的網(wǎng)絡(luò)都是經(jīng)確認(rèn)可以進(jìn)行精簡(jiǎn)的

112, 確認(rèn)沒有在生產(chǎn)時(shí)不安裝的插件上設(shè)置測(cè)試點(diǎn)

113, Test Via、Test Pin是否已Fix(適用于測(cè)試針床不變的改板)

r.DRC

114, Test via 和Test pin 的Spacing Rule應(yīng)先設(shè)置成推薦的距離,檢查DRC,若仍有DRC存在,再用最小距離設(shè)置檢查DRC

115, 打開約束設(shè)置為打開狀態(tài),更新DRC,查看DRC中是否有不允許的錯(cuò)誤

116, 確認(rèn)DRC已經(jīng)調(diào)整到最少,對(duì)于不能消除DRC要一一確認(rèn);

s.光學(xué)定位點(diǎn)

117, 確認(rèn)有貼裝元件的PCB面已有光學(xué)定位符號(hào)

118, 確認(rèn)光學(xué)定位符號(hào)未壓線(絲印和銅箔走線)

119, 光學(xué)定位點(diǎn)背景需相同,確認(rèn)整板使用光學(xué)點(diǎn)其中心離邊≥5mm

120, 確認(rèn)整板的光學(xué)定位基準(zhǔn)符號(hào)已賦予坐標(biāo)值(建議將光學(xué)定位基準(zhǔn)符號(hào)以器件的形式放置),且是以毫米為單位的整數(shù)值。

121, 管腳中心距《0.5mm的IC,以及中心距小于0.8 mm(31 mil)的BGA器件,應(yīng)在元件對(duì)角線附近位置設(shè)置光學(xué)定位點(diǎn)

t.阻焊檢查

122, 確認(rèn)是否有特殊需求類型的焊盤都正確開窗(尤其注意硬件的設(shè)計(jì)要求)

123, BGA下的過孔是否處理成蓋油塞孔

124, 除測(cè)試過孔外的過孔是否已做開小窗或蓋油塞孔

125, 光學(xué)定位點(diǎn)的開窗是否避免了露銅和露線

126, 電源芯片、晶振等需銅皮散熱或接地屏蔽的器件,是否有銅皮并正確開窗。由焊錫固定的器件應(yīng)有綠油阻斷焊錫的大面積擴(kuò)散

四、出加工文件

u.鉆孔圖

127, Notes的PCB板厚、層數(shù)、絲印的顏色、翹曲度,以及其他技術(shù)說明是否正確

128, 疊板圖的層名、疊板順序、介質(zhì)厚度、銅箔厚度是否正確;是否要求作阻抗控制,描述是否準(zhǔn)確。疊板圖的層名與其光繪文件名是否一致

129, 將設(shè)置表中的Repeat code 關(guān)掉,鉆孔精度應(yīng)設(shè)置為2-5

130, 孔表和鉆孔文件是否最新 (改動(dòng)孔時(shí),必須重新生成)

131, 孔表中是否有異常的孔徑,壓接件的孔徑是否正確;孔徑公差是否標(biāo)注正確

132, 要塞孔的過孔是否單獨(dú)列出,并標(biāo)注“filled vias”

v.光繪

133, 光繪文件輸出盡量采用RS274X格式,且精度應(yīng)設(shè)置為5:5

134, art_aper.txt 是否已最新(274X可以不需要)

135, 輸出光繪文件的log文件中是否有異常報(bào)告

136, 負(fù)片層的邊緣及孤島確認(rèn)

137, 使用光繪檢查工具檢查光繪文件是否與PCB 相符(改板要使用比對(duì)工具進(jìn)行比對(duì))

五、文件齊套

138, PCB文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào).brd

139, 背板的襯板設(shè)計(jì)文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào)-CB[-T/B].brd

140, PCB加工文件:PCB編碼.zip(含各層的光繪文件、光圈表、鉆孔文件及ncdrill.log;拼板還需要有工藝提供的拼板文件*.dxf),背板還要附加襯板文件:PCB編碼-CB[-T/B].zip (含drill.art、*.drl、ncdrill.log)

141, 工藝設(shè)計(jì)文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào)-GY.doc

142, SMT坐標(biāo)文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào)-SMT.txt,(輸出坐標(biāo)文件時(shí),確認(rèn)選擇 Body center,只有在確認(rèn)所有SMD器件庫(kù)的原點(diǎn)是器件中心時(shí),才可選Symbol origin)

143, PCB板結(jié)構(gòu)文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào)-MCAD.zip(包含結(jié)構(gòu)工程師提供的.DXF與.EMN文件)

144, 測(cè)試文件:產(chǎn)品型號(hào)_規(guī)格_單板代號(hào)_版本號(hào)-TEST.ZIP(包含testprep.log 和 untest.lst或者*.drl測(cè)試點(diǎn)的坐標(biāo)文件)

145, 歸檔圖紙文件:產(chǎn)品型號(hào)規(guī)格-單板名稱-版本號(hào).pdf,(包括:封面、首頁(yè)、各層絲印、各層線路、鉆孔圖、背板含有襯板圖)

六、標(biāo)準(zhǔn)化

146, 確認(rèn)封面、首頁(yè)信息正確

147, 確認(rèn)圖紙序號(hào)(對(duì)應(yīng)PCB各層順序分配)正確的

148, 確認(rèn)圖紙框上PCB編碼是正確的

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

396文章

4790瀏覽量

89539 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43796

發(fā)布評(píng)論請(qǐng)先 登錄

原理圖和PCB設(shè)計(jì)中的常見錯(cuò)誤

高頻PCB設(shè)計(jì)中出現(xiàn)的干擾分析及對(duì)策

SMT貼片前必知!PCB設(shè)計(jì)審查全攻

多板 PCB 組裝中最常見的邏輯錯(cuò)誤

電子工程師的PCB設(shè)計(jì)經(jīng)驗(yàn)

電源 PCB 布局中的常見錯(cuò)誤及避免方式

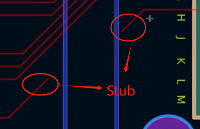

PCB設(shè)計(jì)中的Stub對(duì)信號(hào)傳輸?shù)挠绊?/a>

pcb板設(shè)計(jì)中的常見錯(cuò)誤

HDMI模塊的PCB設(shè)計(jì)

高速PCB設(shè)計(jì)指南

專業(yè)PCB設(shè)計(jì),高速PCB設(shè)計(jì),PCB設(shè)計(jì)外包, PCB Layout,PCB Design,PCB畫板公司,PCB設(shè)計(jì)公司,迅安通科技公司介紹

具有錯(cuò)誤觸發(fā)避免功能的過零檢測(cè)

PCB設(shè)計(jì)與PCB制板的緊密關(guān)系

PCB設(shè)計(jì)基本原則總結(jié),工程師必看

初學(xué)者必看:破解PCB設(shè)計(jì)常見錯(cuò)誤!

如何避免pcb設(shè)計(jì)出現(xiàn)錯(cuò)誤

如何避免pcb設(shè)計(jì)出現(xiàn)錯(cuò)誤

評(píng)論