多層板的接地層可以顯著提高電路的噪聲性能。對于雙面板,我們通常不能有地平面,我們希望有更多的噪音和排放。由于這個限制,我們更喜歡多層板,除非成本目標迫使我們使用雙層板。

即使我們沒有帶有雙層板的地平面,仍然是可用于改善電路性能的技術。本文介紹了接地網格技術,它允許我們為雙面電路板實現高效的接地電路。

地平面如何降低電路板噪聲?為了更好地理解“地網”技術的運行,它將幫助您首先了解PCB中地平面的功能。請查看我的文章,了解地面如何在需要之前減少電路板噪聲。

什么是網格化地平面?

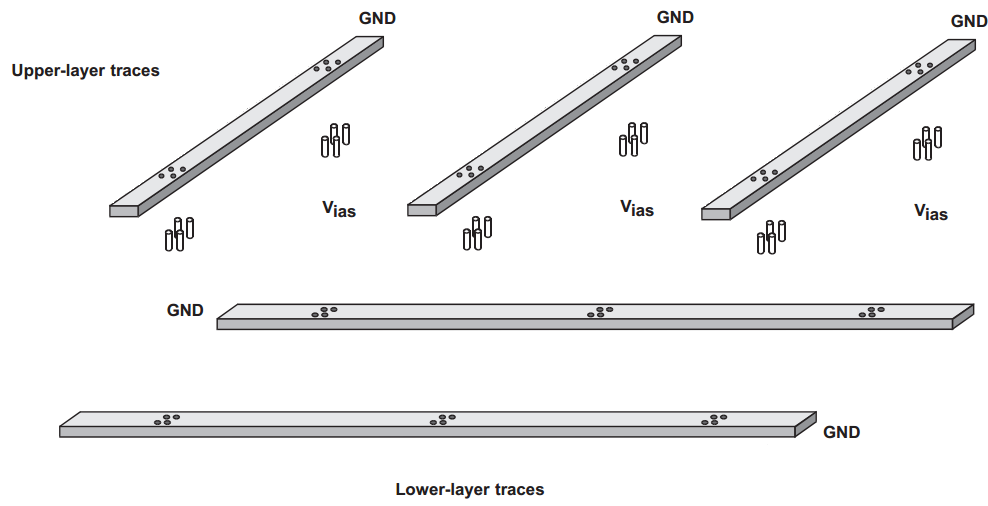

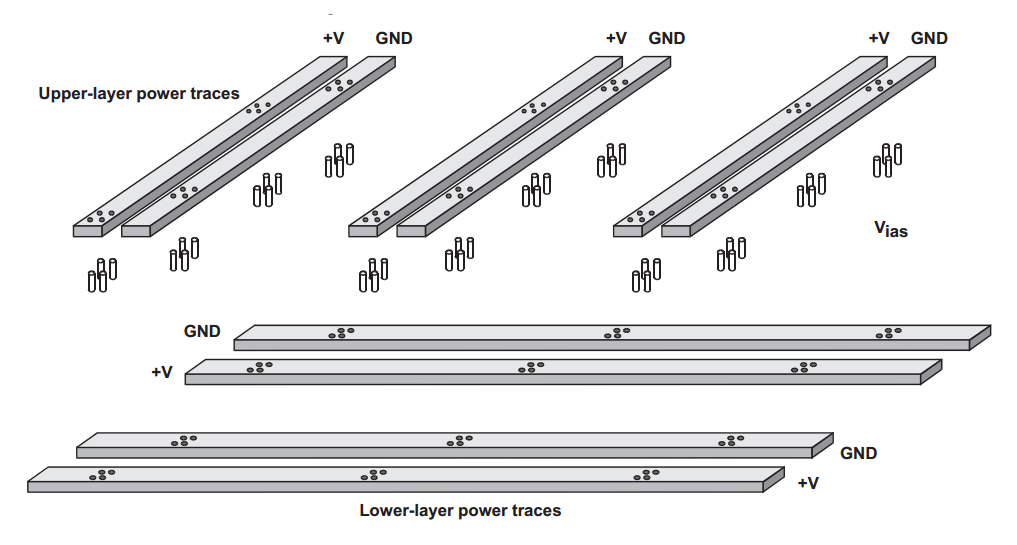

地面網格由PCB上的接地網絡創建。例如,如圖1所示,我們可以在電路板底層有一些水平接地走線,頂層有一些垂直接地走線。此外,在垂直和水平地面軌跡的交叉點處有過孔。

圖1。圖片由TI提供。

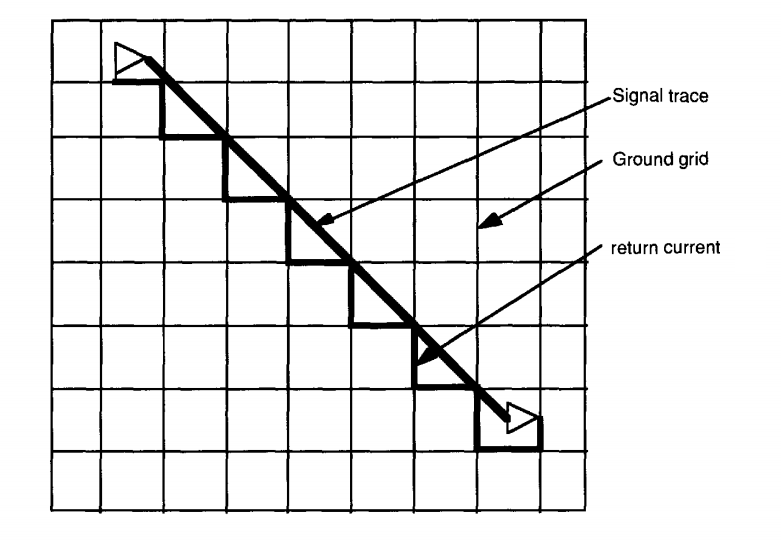

上述技術如何創建低電感地系統?圖1中的網格相當粗糙。圖2中顯示了更精細的接地網格(不區分底部和頂部接地跡線)。信號走線將左上角的柵極輸出連接到右下角的柵極輸入。

圖2。圖片由EMC和印刷電路板提供。

如您所見,可以通過地面網格提供的許多替代返回路徑關閉當前循環。雖然有許多并聯的返回路徑,但大部分電流將流過最靠近信號走線的路徑,以最小化路徑電感。圖中顯示了可能具有相對較小電感的可能返回路徑。

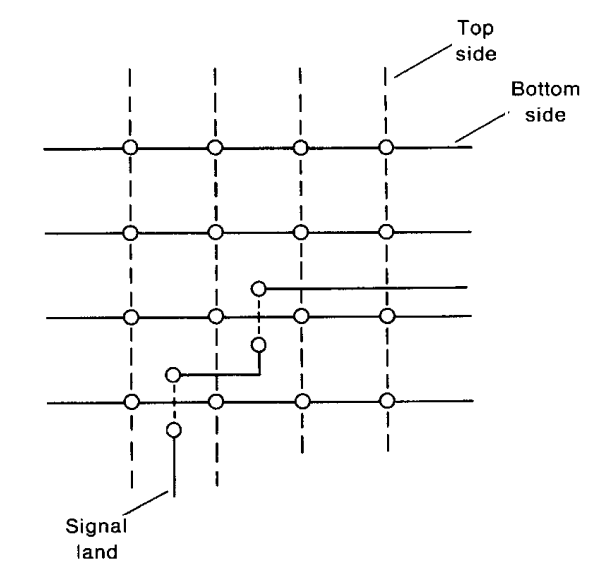

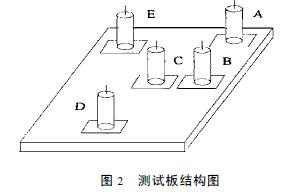

請注意,對于接地網格,您可能必須使用多個過孔來在PCB上布線信號走線。如圖3所示(圖2的概念圖中沒有顯示)。

圖3。圖片由電磁兼容性介紹提供。

因此,它更好使大多數頂層跡線垂直運行,大部分底層跡線水平延伸,以便需要更少的過孔。

它的效率如何?

檢查地面系統有效性的一種方法是測量電路板上各種IC之間的接地噪聲電壓。一項研究比較了使用接地網格的雙層電路板的IC的接地引腳與采用單點接地的類似設計的接地引腳之間的電壓差。該研究表明,接地網可以將IC的接地引腳之間的電壓差從1000 mV降低到100 mV(這是各種IC組合之間的最佳改進)。根據這項研究,當應用地面網格技術時,電路板輻射減少了約7 dB。有關此研究的更多詳細信息,請參閱Henry W. Ott的電磁兼容性工程的第10.5.3節。

為了顯著降低接地電路電感,應使用0.5英寸或更小的接地網格間距。通常,隨著工作頻率的增加,我們可能需要使用更精細的網格來提供更多的并行路徑并降低接地系統電感。接地網格技術與工作頻率高達10 MHz的電路兼容;在這個頻率之上應該使用地平面。

地面網格技術的其他版本

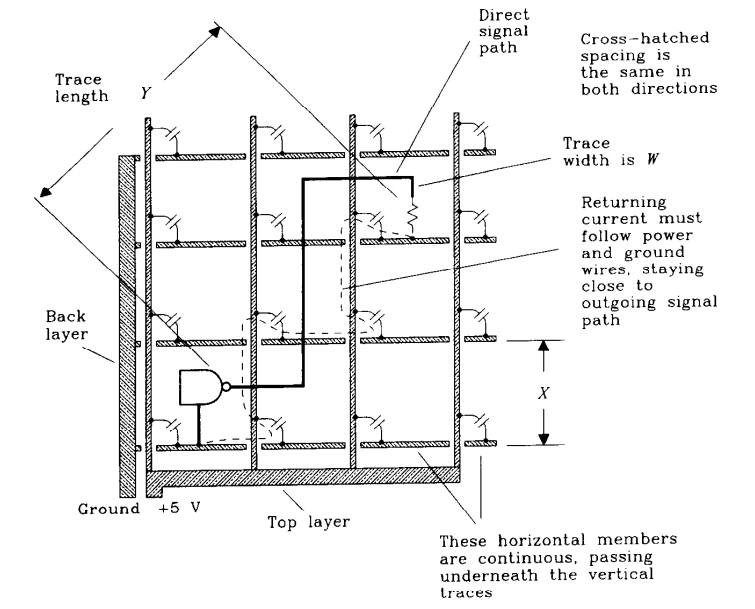

不同的書籍和應用筆記都提出了略有不同的版本地網技術。雖然圖1的地面網格僅出現在地面軌跡上,但霍華德·約翰遜和馬丁·格雷厄姆所著的“高速數字設計:黑魔法手冊”一書建議如圖4所示。

圖4。圖片由霍華德提供來自高速數字設計的Johnson和Martin Graham:黑魔法手冊。

在這種情況下,頂層的垂直接地線被電源線替換。水平構件連接到地面。請注意,這些接地走線位于電路板的底部并且是連續的;它們不會被頂層的電源線斷開。圖4的接地網格將起作用,因為交流回流電流可以沿著接地走線或電源走線同樣良好地流回其源極。由于過孔不能用于此方案,我們必須在垂直和水平走線的交叉點使用旁路電容。這些電容應具有高質量,以使電流容易流回其驅動柵極。

我們還可以在頂層和底層上都有接地和電源走線。如圖5所示。

圖5. 圖片由TI提供。

這將占用更多的電路板空間,但我們預計它會表現出更低的電感,因為現在返回電流可以流過接地走線和電源走線。流過電源走線的返回電流部分將使用旁路電容到達附近的接地走線,通過它可以流回驅動門。

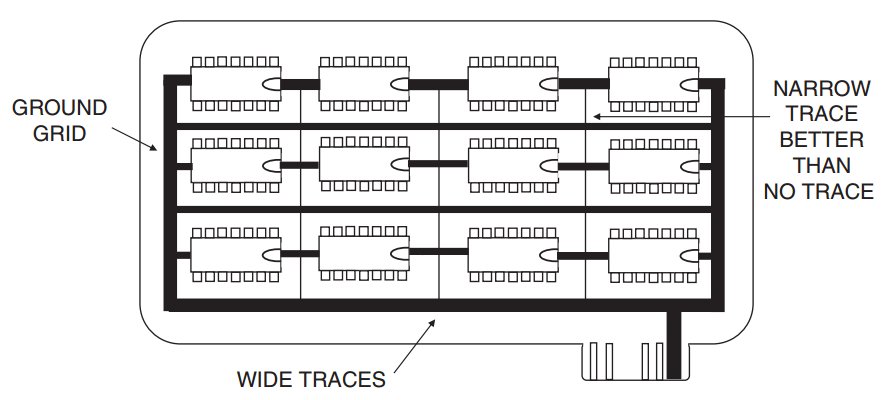

如果電路板空間有限,則不允許使用寬跡線,您可以使用窄跡線實現網格。如圖6所示。

圖6。圖片由電磁兼容工程提供。

寬走線可以提供更低的電阻,這對于低頻考慮非常重要;然而,即使是窄的跡線也可以為電網系統增加許多并行路徑并降低接地電感(高頻率)。

結論

接地路徑電感可通過幾種不同的機制增加電路板噪聲。多層板允許我們擁有可以顯著降低接地電感的堅固接地層。然而,對于雙面板,我們必須采用其他技術,例如接地網,來實現低電感接地系統。一項研究表明,地面電網可以將發射減少約7 dB,地電壓差異減少一個數量級。

-

pcb

+關注

關注

4362文章

23456瀏覽量

408132 -

電路板

+關注

關注

140文章

5116瀏覽量

102094

發布評論請先 登錄

地面如何在需要之前減少電路板噪聲

地面如何在需要之前減少電路板噪聲

評論