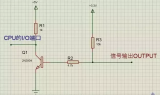

集電極開路輸出端或者MOS管漏極輸出端其性質都是一樣的,這種電路在數字電路中都要加上拉電阻。比如在單片機P0口其內部驅動電路是MOS構成的,其結構就是一個漏極開路電路,其內部沒有上拉電阻。當單片機I/O口輸出時,它會由程序根據控制要求來輸出高電平或低電平,假如這時P0口外部不加一個外加電阻,當需要一個高電平輸出時,由于是漏極開路而無法得到高電平,因此必須加上拉電阻才能得出所需的高低電平。這個電阻也是有要求的,不能太大也不能太小,在實際應用中P0口的上拉電阻一般為10K。如果電阻選大了其高低電平的速率會變低,功率也會變小。

下面我們再說說數字電路中的集電極開路電路,這種數字電路中一般都是用三極管構成的,它的工作狀態在截止和飽和導通二者之間迅速轉換。我們可以這樣假設,當三極管集電極不加上拉電阻時就沒有電流流入集電極,集電極就沒有信號,因此也就得不到我們所需要的電平信號。所以在數字電路中集電極開路的OC門是必須加上拉電阻的。另外說一句,這個上拉電阻也要選擇合適,不然的話會影響這個電路的驅動電流能力和功耗。

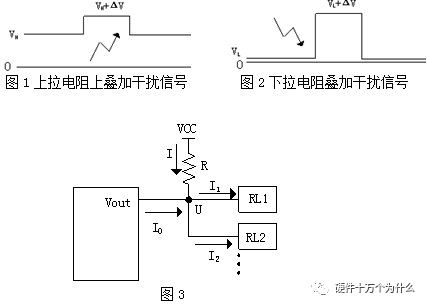

有上拉電阻就會有下拉電阻,它的作用也是為了穩定電平。

-

上拉電阻

+關注

關注

5文章

366瀏覽量

31084 -

集電極

+關注

關注

4文章

226瀏覽量

22529

發布評論請先 登錄

【經典】集電極開路,漏極開路,推挽,上拉電阻,弱上拉,三態...

集電極開路,漏極開路,推挽,上拉電阻

集電極開路_漏極開路_推挽_上拉電阻_弱上拉_三態門_準雙向口

集電極開路、漏極開路、上拉電阻、下拉電阻等接口相關基本概念

集電極加上拉電阻的作用

集電極加上拉電阻的作用

評論