Frederik Dostal

ADI公司

許多模擬電路需要一種時鐘信號,或者要求能在一定時間后執行某項任務。對于這樣的應用,有各種各樣適用的解決方案。對于簡單的時序任務,可以使用標準的555電路。使用555電路和適當的外部組件,可以執行許多不同的任務。

然而,使用相當廣泛的555定時器有一個缺點,就是設置不太精確。555定時器通過給外部電容充電和檢測電壓閾值來工作。這種電路很容易制作,但它的精度很大程度上取決于其電容的實際值。

晶體振蕩器適用于精度要求較高的應用。它們的精度可能很高,但它們有一個缺點:可靠性。參與電氣設備維修的人都知道,故障通常是由大型電解電容引起的。晶體振蕩器是引起故障的第二大原因。

第三種測量時間長度或生成時鐘信號的方法是使用一個簡單的小型微控制器。當然,可供選擇的器件數量繁多,且可以選擇各自不同的優化方法。但是,這些器件需要編程,用戶需要掌握一定的知識才能使用它;此外,由于其采用數字設計,在關鍵應用中使用時,必須非常小心謹慎。例如,如果微控制器發生故障,整個系統會出現問題。

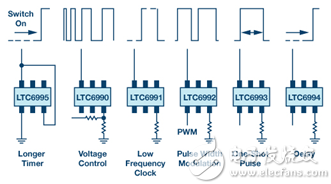

除了這三種基本的時鐘產生構建塊之外,還有其他不太為人所知的替代方案。ADI公司提供的TimerBlox模塊就是這樣一種替代方案。它們是基于硅的時序模塊,與微控制器不同,它們在運行中是完全模擬的,可以通過電阻進行調整。所以,它不需要軟件編程,功能也非常可靠。圖1對不同的TimerBlox模塊進行了概述,且介紹了它們各自的基本功能。使用這些基本構建模塊可以生成無數其他功能。

圖1.用于生成各種時序功能的TimerBlox電路。

與廣泛使用的555定時器電路相比,TimerBlox電路不依賴外部電容充電。所有的設置都在電阻中完成,因此其功能更精確。精度可達到1%至2%。晶體振蕩器的精度更高,約為100倍,但隨之而來的是各種缺點。

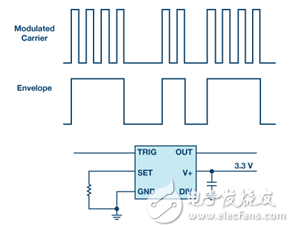

圖2.采用LTC6993 TimerBlox集成電路的包絡檢波器。

時序模塊的應用非常多樣化。ADI公司已經發布了許多示例電路。圖2顯示了一個包絡檢波器。幾個快速脈沖結合在一起形成一個較長的脈沖。LTC6993-2的外部組件對于這個應用來說是最少的。電路中的電容只是一個支持電源電壓的備用電容,對定時模塊的精度沒有影響。

其他有趣的應用還包括用于電源的多個開關穩壓器的相移同步,或將擴頻調制添加到具有同步輸入的開關穩壓器IC中。另一個典型的應用是部署指定的延遲,也就是定時器為特定的電路段提供延遲開啟的功能。

有許多不同的技術解決方案用于生成時鐘信號和執行各種基于時間的任務。每種方案各有其優缺點。例如TimerBlox模塊這樣的硅振蕩器,就因為使用可變電阻代替電容,所以具備易于使用、精度高、可靠性高等特點。

作者簡介

Frederik Dostal曾就讀于德國埃爾蘭根-紐倫堡大學微電子學專業。他于2001年開始工作,涉足電源管理業務,曾擔任多種應用工程師職位,并在亞利桑那州鳳凰城工作了四年,負責開關模式電源。Frederik于2009年加入ADI公司,擔任歐洲分公司的電源管理技術專家。聯系方式:frederik.dostal@analog.com。

發布評論請先 登錄

工業現場的CCLink模塊總線協議通訊:網關模塊的應用價值

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

FPGA時序約束之設置時鐘組

一文詳解Vivado時序約束

在linux使用HUMMINGGBIRD Debugger Kit V2連接目標板上e203提示出錯是怎么回事?

LM98640到底按照什么時序采集才能正確實現串轉并?

ADS8861時鐘配置,監測SCLK和DOUT波形,發現存在SCLK和DOUT同時動作的情況,該波形或者時序是否正確?

TAS5518c將0xD9寄存器改為0x48,沒有波形輸出是怎么回事?

DDR4時序參數介紹

鎖存器的基本輸出時序

時序邏輯會產生鎖存器嗎

DRAM內存操作與時序解析

正確的時序

正確的時序

評論