I2S接口概述

I2S或I2S(Inter-IC Sound或Integrated Interchip Sound)是由飛利浦公司(現(xiàn)NXP)在1986年制定的一種用于音頻IC或者設(shè)備之間傳輸數(shù)字PCM信息的一種接口標(biāo)準(zhǔn)。I2S常被使用在各種音源到音頻DAC中。由于I2S將信號以及時鐘分開傳送,它的jitter失真十分地小。I2S和I2C名字非常的像,但是切記,他們完全不是一個東西,甚至連時序都不太像,要說同I2S最像的還是SPI。I2S規(guī)范最終的修訂是在1996年。

I2S接口硬件定義

NXP公司的I2S是一套硬件+時序規(guī)范。I2S硬件上有3個主要信號:

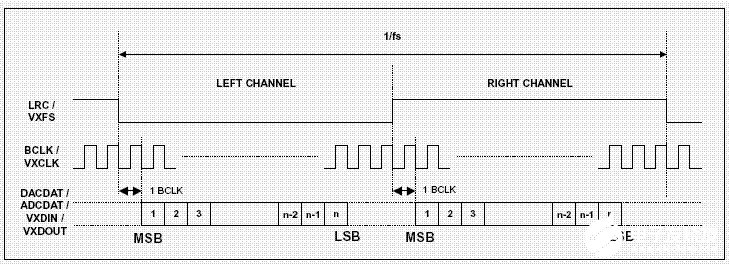

continuous serial clock,連續(xù)串行時鐘SCK,在一些資料中也就SCLK或者BCLK,即對應(yīng)數(shù)字音頻的每一位數(shù)據(jù),SCLK有1個脈沖。SCLK的頻率=2×采樣頻率×采樣位數(shù)。

word select,字選擇WS,又叫幀時鐘LRCK,用于切換左右聲道的數(shù)據(jù)。WS為“0”表示代表傳輸?shù)氖亲舐暤赖臄?shù)據(jù),為“1”則表示正在傳輸?shù)氖怯衣暤赖臄?shù)據(jù)。WS的頻率等于采樣頻率。

serial data,串行數(shù)據(jù)SD,又叫SDATA,是用二進(jìn)制補(bǔ)碼表示的音頻數(shù)據(jù)。

有時為了使系統(tǒng)間能夠更好地同步,還需要另外傳輸一個信號MCLK,稱為主時鐘,也叫系統(tǒng)時鐘(Sys Clock),是采樣頻率的256倍或384倍,這個信號在后面會單獨講到。

I2S接口時序與對齊

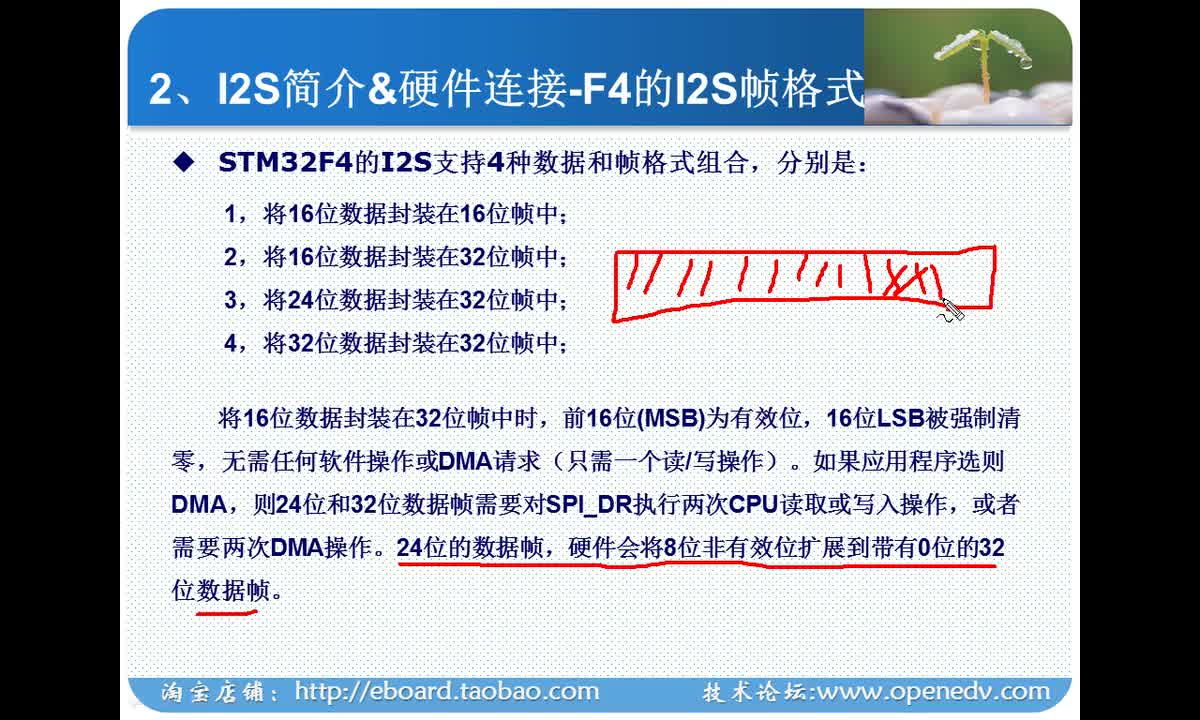

I2S接口有著統(tǒng)一的硬件定義,但是數(shù)據(jù)的傳輸格式又各有不同,我們把他們分成三類:

I2S格式

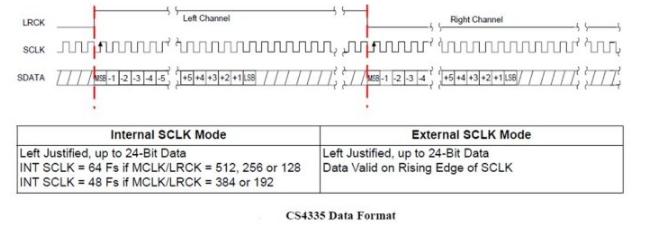

左對齊格式,left justified

右對齊格式,right justified,也叫EIAJ或者SONY格式

這三種傳輸格式,基本都是相同的,不同之處在于SD數(shù)據(jù)同WS信號的對齊位置。I2S格式的信號無論有多少位有效數(shù)據(jù),數(shù)據(jù)的最高位總是出現(xiàn)在WS變化(也就是一幀開始)后的第2個SCK脈沖處,見下面I2S格式圖:

i2s timing

故名思議,左對齊(left justified)、右對齊(right justified)指的是數(shù)據(jù)信號對齊的方式,左對齊的時候最高位數(shù)據(jù)在第一個時鐘就出現(xiàn),而右對齊的時候數(shù)據(jù)最低位在最后一個時鐘出現(xiàn)。這就是他們的本質(zhì)區(qū)別。左右對齊模式隨具體的芯片不同而不同,在使用的時候需要仔細(xì)閱讀芯片手冊。I2S允許接收端與發(fā)送端的有效位數(shù)可以不同。如果接收端能處理的有效位數(shù)少于發(fā)送端,可以放棄數(shù)據(jù)幀中多余的低位數(shù)據(jù);如果接收端能處理的有效位數(shù)多于發(fā)送端,可以自行補(bǔ)足剩余的位。這種同步機(jī)制使得數(shù)字音頻設(shè)備的互連更加方便,而且不會造成數(shù)據(jù)錯位。

I2S接口的Master和Slave模式以及其同DSP的連接方法

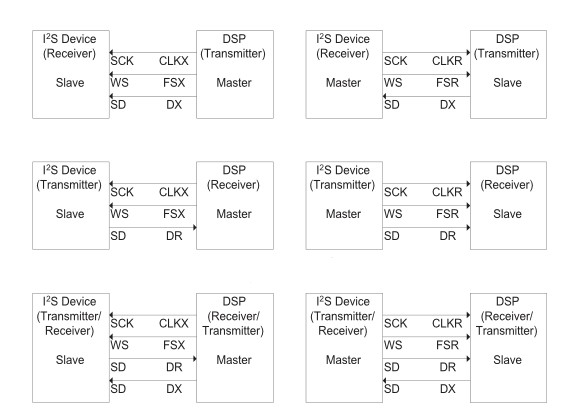

TI公司的DSP可用的I2S接口有McBSP以及McASP,兩個接口大同小異,下圖代表了不同模式下的DSP同I2S設(shè)備的連接關(guān)系:

TI DSP I2S connecting mode

圖中,箭頭代表了信號的傳輸方向,主模式(Master)以及從模式(Slave)的區(qū)別就在于時鐘信號是由哪一邊給出的。在使用的時候需要參考McASP以及McBSP的資料。在DSP上使用I2S主要分為以下幾個步驟:

器件選型,確定連接模式(Slave or Master)

設(shè)計原理圖,正確連接電器關(guān)系

McBSP或者M(jìn)cASP寄存器配置

從(往)FIFO中Put or Get 數(shù)據(jù)即可

I2S接口的MCLK作用

MCLK是Master clock的縮寫,在DAC內(nèi)部的delta-sigma調(diào)制器以及數(shù)字濾波器都需要用到這個時鐘,大部分的DAC可以使用內(nèi)部的振蕩器產(chǎn)生這個時鐘,在某些要求較高的場合,例如HIFI音響系統(tǒng)等,需要使用一個額外的高質(zhì)量的時鐘用以獲得最好的性能。這時候就需要用到MCLK信號了。切記,MCLK并不是必須的。可有可無,看設(shè)計要求。MCLK一般是Fs*256或者Fs*384。

-

dsp

+關(guān)注

關(guān)注

556文章

8158瀏覽量

357834 -

接口

+關(guān)注

關(guān)注

33文章

9005瀏覽量

153787 -

I2S

+關(guān)注

關(guān)注

1文章

73瀏覽量

42917

發(fā)布評論請先 登錄

音頻總線I2S協(xié)議:I2S收發(fā)模塊FPGA的仿真設(shè)計

請問PCM4204是I2S接口嗎?

利用MAXIICPLD實現(xiàn)SPI至I2S的接口

音頻接口I2S實驗

基于FPGA和AD1836的I2S接口設(shè)計

I2S接口工作原理_I2S接口介紹

幾種常見的I2S數(shù)據(jù)格式

I2S、TDM、PCM音頻總線

AN5086_如何使用標(biāo)準(zhǔn)SPI和Timer來模擬I2S接口

雅特力AT32 MCU SPI/I2S入門指南

AT32講堂048 | 雅特力AT32 MCU SPI/I2S入門指南

I2S接口概述和與DSP的連接方法

I2S接口概述和與DSP的連接方法

評論