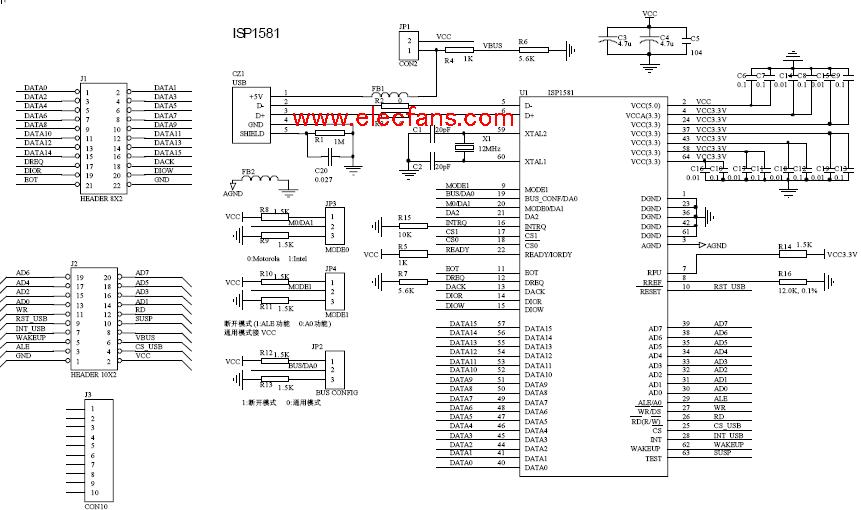

基于FPGA實現USB2.0接口通信, USB2.0 PHY芯片是Cypress68013, 68013內部集成8051 內核,USB2.0芯片讀寫需要對8051核進行固件配置。

一.FX2特性介紹

1.1、介紹

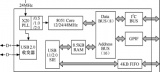

Cypress Semiconductor公司的EZ-USB FX2是世界上第一款集成USB2.0的微處理器,它集成了USB2.0收發器、SIE(串行接口引擎)、增強的8051微控制器和可編程的外圍接口。FX2這種獨創性結構可使數據傳輸率達到56Mbytes/s,即USB2.0允許的最大帶寬。在FX2中,智能SIE可以硬件處理許多USB1.1和USB2.0協議,從而減少了開發時間和確保了USB的兼容性。GPIF(General Programmable Interface)和主/從端點FIFO(8位或16位數據總線)為ATA、UTOPIA、EPP、PCMCIA和DSP等提供了簡單和無縫連接接口。

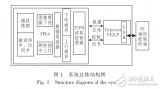

1.2、結構

CY7C68013結構圖如圖1所示。它有三種封裝形式:56SSOP,100TQFP和128TQFP。

1.3、特征

★ 內嵌480MBit/s的收發器,鎖相環PLL,串行接口引擎SIE——集成了整個USB 2.0協議的物理層。

★ 為適應USB 2.0的480MBit/s的速率,FIFO端點可配置成2,3,4個緩沖區。

★ 內嵌可工作在48MHz的增強型8051,它具有以下特征:

- 具有256Byte的寄存器空間,兩個串口,三個定時器,兩個數據指針。

- 四個機器周期(工作在48MHz下時為83.3ns)即組成一個指令周期。

- 特殊功能寄存器(包括I/O口控制寄存器)可高速訪問。

- 應用USB向量中斷,具有極短的ISR響應時間。

- 只用作USB事務管理,控制,不參與數據傳輸,較好地解決了USB高速模式的帶寬問題。

★ “軟配置”——USB固件可由USB總線下載,片上不需集成ROM。

★ 擁有四個FIFO接口,可工作在內部或外部時鐘下。端點和FIFO接口的應用使外部邏輯和USB總線可高速連接。

★ 內嵌通用可編程接口GPIF,它是一個狀態機,可充當主控制器,提供外部邏輯和USB總線的“無膠粘貼”。

★ 一種單片USB 2.0外設解決方案,不需要外部的協議物理層,FX2把所有的功能集成在一個芯片上。

二、Slave FIFO傳輸

2.1、概述

當有一個與FX2芯片相連的外部邏輯只需要利用FX2做為一個USB 2.0接口而實現與主機的高速通訊,而它本身又能夠提供滿足Slave FIFO要求的傳輸時序,可以做為Slave FIFO主控制器時,即可考慮用此傳輸方式。

Slave FIFO傳輸的示意圖如下:

在這種方式下,FX2內嵌的8051固件的功能只是配置Slave FIFO相關的寄存器以及控制FX2何時工作在Slave FIFO模式下。一旦8051固件將相關的寄存器配置完畢,且使自身工作在Slave FIFO模式下后,外部邏輯(如FPGA)即可按照Slave FIFO的傳輸時序,高速與主機進行通訊,而在通訊過程中不需要8051固件的參與。

2.2、硬件連接(標準)

在Slave FIFO方式下,外部邏輯與FX2的連接信號圖如下:

IFCLK:FX2輸出的時鐘,可做為通訊的同步時鐘;

FLAGA,FLAGB,FLAGC,FLAGD:FX2輸出的FIFO狀態信息,如滿,空等;

SLCS:FIFO的片選信號,外部邏輯控制,當SLCS輸出高時,不可進行數據傳輸;

SLOE:FIFO輸出使能,外部邏輯控制,當SLOE無效時,數據線不輸出有效數據;

SLRD:FIFO讀信號,外部邏輯控制,同步讀時,FIFO指針在SLRD有效時的每個IFCLK的上升沿遞增,異步讀時,FIFO讀指針在SLRD的每個有效—無效的跳變沿時遞增;

SLWR:FIFO寫信號,外部邏輯控制,同步寫時,在SLWR有效時的每個IFCLK的上升沿時數據被寫入,FIFO指針遞增,異步寫時,在SLWR的每個有效—無效的跳變沿時數據被寫入,FIFO寫指針遞增;

PKTEND:包結束信號,外部邏輯控制,在正常情況下,外部邏輯向FX2的FIFO中寫數,當寫入FIFO端點的字節數等于FX2固件設定的包大小時,數據將自動被打成一包進行傳輸,但有時外部邏輯可能需要傳輸一個字節數小于FX2固件設定的包大小的包,這時,它只需在寫入一定數目的字節后,聲明此信號,此時FX2硬件不管外部邏輯寫入了多少字節,都自動將之打成一包進行傳輸;

FD[15:0]:數據線;

FIFOADR[1:0]:選擇四個FIFO端點的地址線,外部邏輯控制。

2.3、 Slave FIFO的幾種傳輸方式

2.3.1 、同步Slave FIFO寫

同步Slave FIFO寫的標準連接圖如下:

同步Slave FIFO寫的標準時序如下:

IDLE:當寫事件發生時,進狀態1;

狀態1:使FIFOADR[1:0]指向IN FIFO,進狀態2;

狀態2:如FIFO滿,在本狀態等待,否則進狀態3;

狀態3:驅動數據到數據線上,使SLWR有效,持續一個IFCLK周期,進狀態4;

狀態4:如需傳輸更多的數,進狀態2,否則進狀態IDLE。

狀態跳轉示意圖如下:

幾種情況的時序圖示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效):

圖示FIFO中本來沒有數據,外部邏輯寫入第一個數據時的情況。

圖示假定FX2設定包大小為512字節,外部邏輯向FIFO端點中寫入的數據達512字節時的情況。此時FX2硬件自動將已寫入的512字節打成一包準備進行傳輸,這個動作就和在普通傳輸中,FX2固件向FIFO端點中寫入512字節后,把512這個數寫入EPxBC中一樣,只不過這個過程是由硬件自動完成的。在這里可以看出“FX2固件不參與數據傳輸過程”的含義了。外部邏輯只須按上面的時序圖所示的時序向FIFO端點中一個一個字節(或字)地寫數,寫到一定數量,FX2硬件自動將數據打包傳輸,這一切均不需固件的參與,由此實現高速數據傳輸。

圖示的是FIFO端點被寫滿時的情況。

2.3.2 、同步Slave FIFO讀:

同步Slave FIFO讀的標準連接圖如下:

同步Slave FIFO讀的標準時序如下:

IDLE:當讀事件發生時,進狀態1;

狀態1:使FIFOADR[1:0]指向OUT FIFO,進狀態2;

狀態2:使SLOE有效,如FIFO空,在本狀態等待,否則進狀態3;

狀態3:從數據線上讀數,使SLRD有效,持續一個IFCLK周期,以遞增FIFO讀指針,進狀態4;

狀態4:如需傳輸更多的數,進狀態2,否則進狀態IDLE。

狀態跳轉示意圖如下:

幾種情況的時序圖示意如下(FULL,EMPTY,SLRD,SLOE均假定低有效):

圖示正常情況時的時序。

圖示FIFO被讀空時的情況。

幾種情況的時序圖示意如下(FULL,EMPTY,SLWR,PKTEND均假定低有效):

圖示FIFO中本來沒有數據,外部邏輯寫入第一個數據時的情況。

三、測試USB接口:

對于USB接口的測試,本次實驗控制開發板上面的USB接口實現與PC機的通信。

用usb2.0線連接pc與開發板usb接口,先下載s3_dram.bit程序,在沒有掉電的情況下,打開相應的EZ-USB軟件(ez-usb為usb2.0接口PC端驅動,安裝文件在 “CY7C68013開發相關工具” 目錄下)。

在使用前,接上USB2.0接口到PC端,PC端設備管理器可以識別到USB設備,如果沒有識別到USB設備,需要手動安裝驅動,驅動文件為ezusbw2k.inf(測試目錄下)的文件,手動選擇inf所在目錄。

啟動畫面如下圖:

上圖表示連接可以進行下面測試,通過EZ_USB軟件下載相應固件s3_dpram.bit程序,slavefifo.hex文件在“下載bit”目錄下點擊Download,

雙擊打開相應讀寫的usb接口VC程序(如下圖)

看到寫的測試現象,流過的數據速率。

應用平臺 :紅色颶風NANO2

責任編輯:gt

-

FPGA

+關注

關注

1640文章

21888瀏覽量

610951 -

usb

+關注

關注

60文章

8053瀏覽量

269062 -

開發板

+關注

關注

25文章

5338瀏覽量

100403

發布評論請先 登錄

相關推薦

源碼系列:基于 FPGA 的 USB2.0 設計

NANO2開發板實例之 USB2.0接口通信回環

NANO2開發板實例之__FPGA實現UDP數據收發數據

NANO2開發應用之 如何使用xilinx下載工具下載bit,固化FPGA

USB2.0 接口控制演示實驗

USB2.0接口IP核的開發與設計

基于FPGA的USB2.0控制器設計

USB2.0接口選型時要注意的問題

基于FPGA NANO2開發板實現USB2.0接口通信的設計方案

基于FPGA NANO2開發板實現USB2.0接口通信的設計方案

評論