(文章來源:驅動之家)

根據外媒AdoredTV提供的消息,AMD代號為米蘭的下一代Zen 3構架將會做一些核心級別的改進,目標是讓Zen 3構架的IPC性能相比目前的Zen 2再度提升10~15%。

Zen3構架仍將采用CPU Die與I/O Die分離的Chiplets設計方案,但是最大的不同就是單個CCX將會擁有8個核心,而現在的銳龍處理器單個CCX是4個核心,2個CCX組成一個CCD。或許很多同學不能理解這樣的變化能帶來哪些改進!

此前單個CCD雖然是8個核心32M L3緩存,但是分成了2個CCX,單個CCX是4個核心16MB緩存,不同的CCX之間L3緩存是不能共用的,也就是說每個核心最多只能調用16MB L3緩存。如果一個應用程序只能支持4個或者更少核心的話,那么另外一個CCX的16MB L3緩存可能就會被閑置了。

Zen 3構架將單個CCX擴大到了8核,內置32MB L3緩存,也就是說不論在任何情況下,任何一個核心都可以調用全部的32M L3緩存,新的Zen3構架不再會浪費任何L3緩存。因此在一些對單核性能要求較高的應用中,這種設計方案將會極大增強處理器的運算效率。

Zen2構架IPC提升18%的秘訣之一就是L3緩存容量翻倍,Zen 3構架則是將每個核心能夠利用的緩存容量再次翻倍。還有一點就是Zen 3的L3緩存設計并不需要增加額外的晶體管,即便是在制程工藝不變的情況下,也能帶來額外的IPC性能提升。

PS:小編現在對于Zen 3構架的改進也是非常開心,此前的Zen1/2的設計方案并不能完全利用L3緩存,這一缺憾在Zen 3時代將不復存在!另外,下下代的Zen 4構架也有一些消息!

Zen 4構架的銳龍5000系列處理器將會使用全新的CPU針腳設計,也就是說現有的主板鐵定是不能兼容了(Zen 3構架的銳龍4000系列處理器仍有可能采用AM4插座)。在制程工藝方面將會是5nm,在指令集方面將會擴展到完整的AVX 512。

另外Zen 4構架會將L2緩存容量翻倍,也就是單個核心將會配備1MB L2緩存。

(責任編輯:fqj)

-

amd

+關注

關注

25文章

5539瀏覽量

135565 -

Zen處理器

+關注

關注

1文章

29瀏覽量

8773

發布評論請先 登錄

相關推薦

三級配電箱:用電保障的關鍵

MediaTek發布旗艦級天璣8400處理器

艾為電子榮獲ISO56005《創新與知識產權管理能力》三級證書

一級、二級和三級配電箱的區別

使用OPA2695搭建的三級運放,輸出的幅頻特性上面有出現周期性的上跳,為什么?

用三級運放做放大信號,第二級用vca821做可控增益放大,輸出波形變了,為什么?

用LMH6552實現的三級放大功能,實物出來之后就不出效果,為什么?

AMD將推出Zen5架構CPU,效能比Zen4快40%

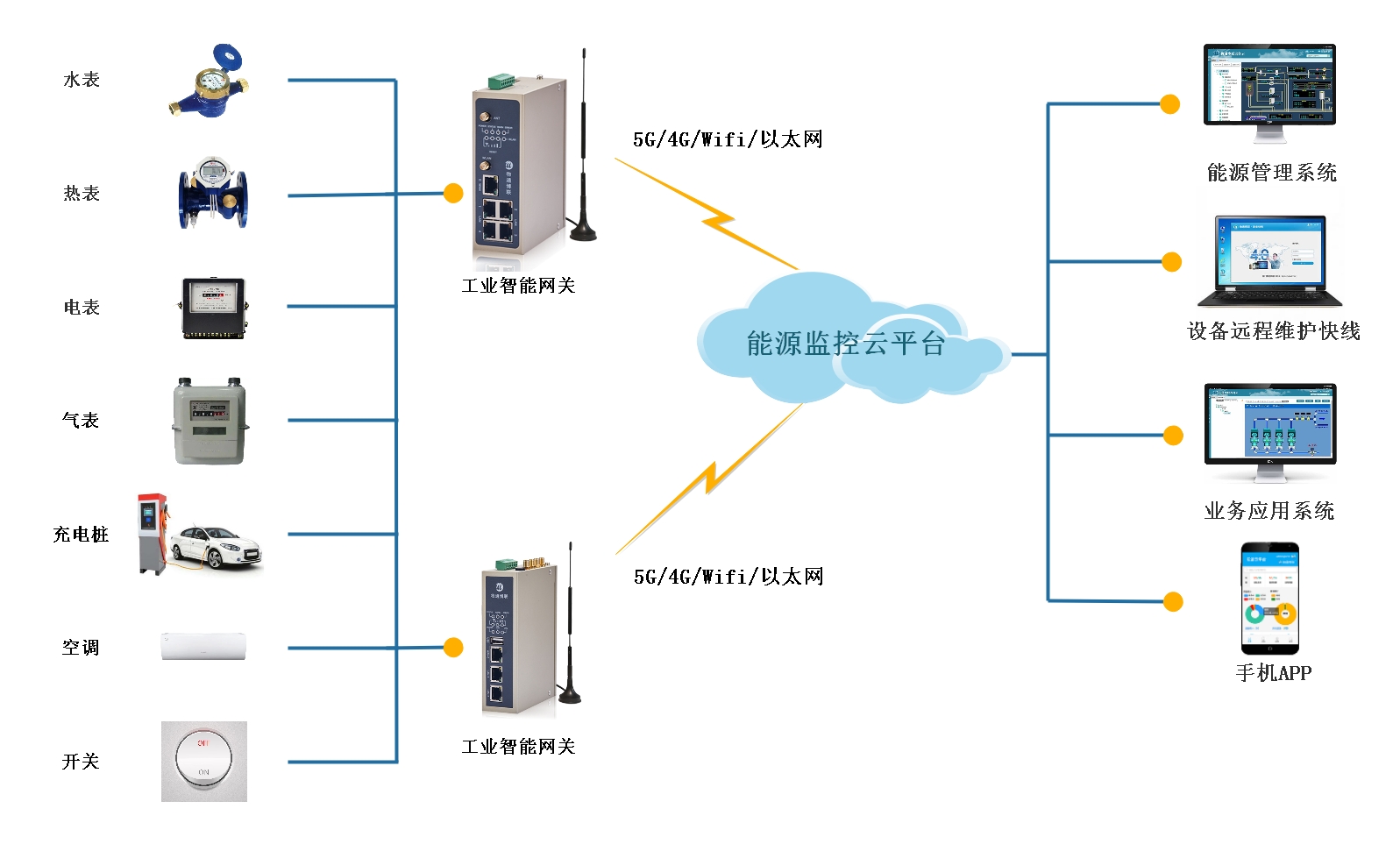

能耗監測三級計量物聯網系統解決方案

Zen 3構架迎來大改,三級緩存容量翻倍性能提升

Zen 3構架迎來大改,三級緩存容量翻倍性能提升

評論