標題:allegro軟件的絕對傳輸延遲是什么,絕對傳輸延遲應該怎么設置呢?

我們在用allegro進行PCB設計完成以后,都需要對一組傳輸的總線進行時序等長,在做時序等長的時候,分為絕對傳輸延遲與相對傳輸延遲。絕對傳輸延遲,顧名思義,信號傳輸在PCB設計中都是有一個走線的長度,我們通過設置這個信號線傳輸的最大值與最小值,來實現等長的方法,就稱之為絕對傳輸延遲。一般情況下如果信號是從一個點傳輸到另一個點,中間沒有任何的串阻、串容,這個絕對傳輸延遲的方法還是非常有效而卻直觀的。具體在PCB中設置絕對傳輸延遲的方法如下所示:

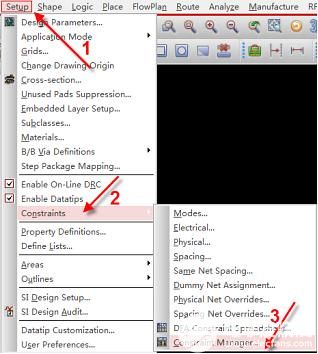

第一步,打開規則管理器,執行菜單命令Setup-Constraints,在下拉菜單中選擇Constraint Manager,如圖5-90所示,進入到規則管理器中;

刪除

(選填) 圖片描述

圖5-90 規則管理器示意圖

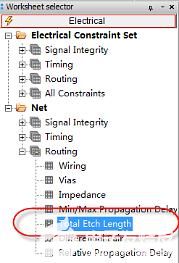

第二步,進入規則管理器以后,在CM左側的目錄欄中選擇Net,在Routing中選擇Total Etch Length,如圖5-91所示,設置信號的線的總長度;

刪除

(選填) 圖片描述

圖5-91 設置絕對長度示意圖

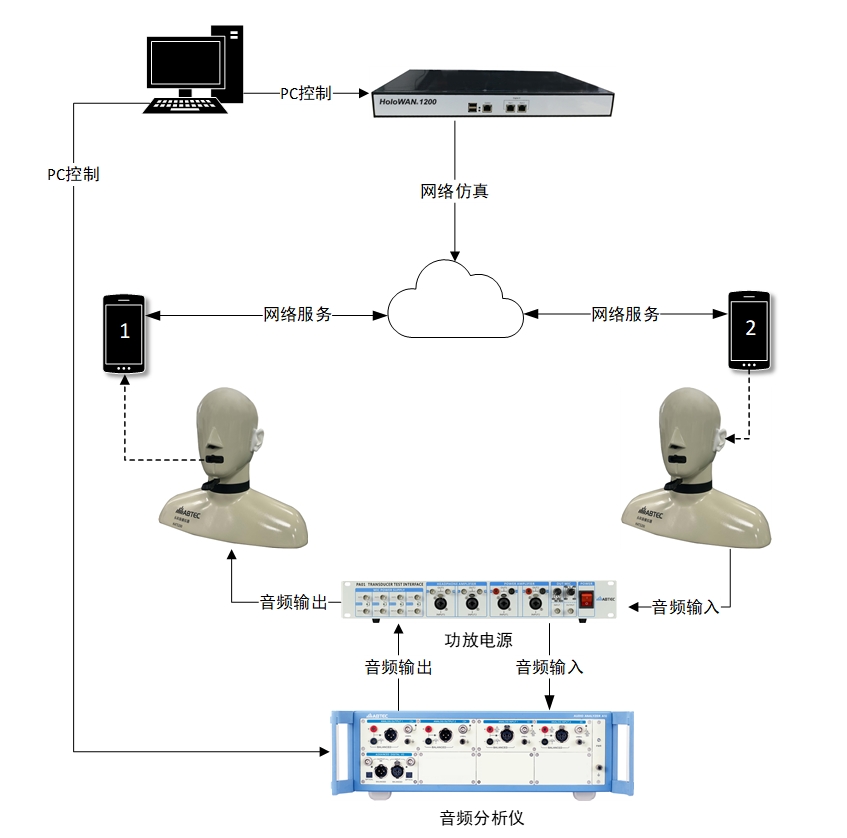

第三步,進入到右邊欄,對需要做等長的信號線,創建好Bus,在Total Etch Length中輸入最小值、最大值即可,如圖5-92所示,每一組的信號線都會跟這個對比產生相對應的誤差,按這個誤差做等長即可;

刪除

(選填) 圖片描述

圖5-92 設置絕對長度最大值最小值示意圖

第四步,回到PCB界面,如果需要做等長的信號線沒有滿足最小值或者最大值的要求,都會報相對應的DRC錯誤,用于提醒工程師做等長設計。

上述,就是在Allegro軟件中,如何設置絕對傳輸延遲的方法解析。

-

pcb

+關注

關注

4362文章

23458瀏覽量

408287 -

PCB設計

+關注

關注

396文章

4792瀏覽量

89777 -

allegro

+關注

關注

42文章

713瀏覽量

147214 -

信號線

+關注

關注

2文章

181瀏覽量

21898 -

可制造性設計

+關注

關注

10文章

2065瀏覽量

16029 -

華秋DFM

+關注

關注

20文章

3503瀏覽量

5358

發布評論請先 登錄

模擬量4-20ma單向對傳模塊:4G雙向傳輸,無線通訊免布線

4G模擬量雙向對傳模塊:不限距離傳輸,實時同步

LLSM——基于RK3588的低延遲低帶寬流媒體傳輸模塊

allegro軟件的絕對傳輸延遲是什么,絕對傳輸延遲應該怎么設置呢?

allegro軟件的絕對傳輸延遲是什么,絕對傳輸延遲應該怎么設置呢?

評論