今年舉辦的國(guó)際固態(tài)電路峰會(huì)(ISSCC)上,處理器部分開(kāi)始于AMD的兩個(gè)演講,然后是三星和聯(lián)發(fā)科演示他們的最新5 G智能手機(jī)芯片,還包括一個(gè)來(lái)自CEA技術(shù)的概念設(shè)計(jì)的研究項(xiàng)目、TI的汽車SoC和IBM 的最新Z系列主機(jī)處理器。

ISSCC是半導(dǎo)體行業(yè)歷史最悠久的技術(shù)會(huì)議之一,每年二月在美國(guó)舊金山舉行。這次會(huì)議匯集了學(xué)術(shù)界和產(chǎn)業(yè)界人士,討論芯片電路設(shè)計(jì)的最新挑戰(zhàn)。該會(huì)議主要是一個(gè)電路設(shè)計(jì)會(huì)議,每個(gè)廠商都專注于他們的處理器中獨(dú)特電路設(shè)計(jì)的一個(gè)或多個(gè)特定方面。

今年的會(huì)議涵蓋了一系列深入主題,包括鎖相環(huán)、低功耗電路、內(nèi)存、SerDes、DSP和處理器設(shè)計(jì)。處理器部分出現(xiàn)了領(lǐng)先的供應(yīng)商,也有來(lái)自研究機(jī)構(gòu)和學(xué)術(shù)界的項(xiàng)目。會(huì)議內(nèi)容覆蓋了密集的芯片設(shè)計(jì)細(xì)節(jié),下面介紹了處理器環(huán)節(jié)中有趣細(xì)節(jié)的突出部分。

AMD Zen2和EPYC芯片

兩個(gè)AMD的會(huì)議相互吻合,討論了最新的EPYC服務(wù)器處理器使用的Zen 2 CPU核心的設(shè)計(jì),并討論了EPYC芯片架構(gòu),允許AMD在一個(gè)基板上提供64個(gè)CPU核心,而不需要大量的芯片。

AMD Zen 2演示描述了使用TSMC的7nm工藝制造第一個(gè)x86處理器的挑戰(zhàn)。EPYC服務(wù)器處理器的設(shè)計(jì)目標(biāo)是在同一個(gè)插槽上增加一倍的CPU內(nèi)核,同時(shí)不超過(guò)插槽的功率峰值。此外,在SPECint 2006基準(zhǔn)測(cè)試上,每個(gè)CPU核心都被設(shè)計(jì)為每周期提供15%的指令性能提升。Zen 2中的許多架構(gòu)更改在前面已經(jīng)討論過(guò)了。在ISSCC的演講中,AMD著重討論了電路設(shè)計(jì)的挑戰(zhàn)。

AMD的設(shè)計(jì)非常模塊化。基本模塊是CCX(CPUComplex),包含4個(gè)CPU核心,L2和L3緩存,使用Infinity總線技術(shù)實(shí)現(xiàn)Fabric系統(tǒng)互連。通過(guò)4核模塊,AMD可以將設(shè)計(jì)從筆記本(4-8核)擴(kuò)展到服務(wù)器(64核)。盡管添加了更多的L3緩存,CCX模塊從上一代的44 mm2縮減到了Zen 2的31.3 mm2。

7nm工藝需要添加更多的金屬層,因此金屬層布局布線規(guī)則發(fā)生了變化,設(shè)計(jì)從10.5個(gè)track變?yōu)?個(gè)track。更低的track帶來(lái)了挑戰(zhàn)(更低的高度和更低的驅(qū)動(dòng)強(qiáng)度),但漏電變少,減少了9%的周期電容,同時(shí)硅面積也更小。

AMD使用了多種設(shè)計(jì)技術(shù),如時(shí)鐘整形,并有五種不同的觸發(fā)器設(shè)計(jì),這對(duì)電路時(shí)序來(lái)說(shuō)十分關(guān)鍵。為了獲得更好的性能,設(shè)計(jì)者還將更多的功耗預(yù)算轉(zhuǎn)移到組合邏輯上,減少了3%。通過(guò)這些和其他電路優(yōu)化,AMD可以將時(shí)鐘速度提高到4.7 GHz,并在與原始Zen core相當(dāng)?shù)臅r(shí)鐘速度下降低工作電壓。

第二個(gè)AMD的介紹描述了基于Zen 2的服務(wù)器產(chǎn)品的多種chiplet策略。AMD的主要優(yōu)勢(shì)之一是,只要三種die即可以創(chuàng)建產(chǎn)品以支持多個(gè)市場(chǎng)。

AMD的目標(biāo)是在每個(gè)插槽上提供更多的性能,第二代EPYC處理器將CPU核數(shù)增加了一倍。這使得AMD的業(yè)績(jī)每2.5年翻一番(SPECint2006),新的EPYC處理器還改善了內(nèi)存延遲。使用chiplet讓AMD的服務(wù)器芯片成為可能,因?yàn)槭褂脝纹酒遣豢尚校彩遣唤?jīng)濟(jì)的,在64核下用單片芯片會(huì)有諸多限制。

AMD還通過(guò)使用更小的chiplet優(yōu)化了成本結(jié)構(gòu),提高了良率。AMD使用昂貴的7納米工藝實(shí)現(xiàn)核心緩存芯片(CCD),并將DRAM和PCIe邏輯轉(zhuǎn)移到GlobalFoundries的12納米I/O芯片上。每個(gè)CCD由兩個(gè)CCX模塊和四個(gè)Zen 2核心以及L2和L3緩存組成,其中86%的CCX專用于CPU和L3緩存。每個(gè)CCD仍然是一個(gè)小型SoC,包括電源管理、Infinity系統(tǒng)互連、時(shí)鐘等。

有了所有這些要求,實(shí)現(xiàn)上就有了許多挑戰(zhàn)。由于內(nèi)存控制器現(xiàn)在位于單獨(dú)芯片上,要用于所有CCX模塊,新的EPYC處理器在平均內(nèi)存訪問(wèn)延遲上有所改進(jìn),但是最佳情況下的延遲仍然需要離開(kāi)CCD來(lái)訪問(wèn)內(nèi)存。因此,AMD的設(shè)計(jì)重點(diǎn)在于減少Infinity Fabricz總線延遲,最佳情況下的延遲只比預(yù)期長(zhǎng)4納秒。

由于AMD承諾保持EPYC封裝尺寸和pin腳不變,因此需要一個(gè)緊密的硅/封裝協(xié)同設(shè)計(jì),因?yàn)閺牡谝淮鶨PYC到第二代EPYC芯片數(shù)量從4個(gè)增加到9個(gè)。內(nèi)部布線非常緊湊,需要在內(nèi)部CCD芯片下的信號(hào)到達(dá)距離集中式I/O芯片更遠(yuǎn)的CCD芯片。

ISSCC的許多其他演講都是關(guān)于當(dāng)處理器處于高負(fù)載時(shí)補(bǔ)償內(nèi)部壓降的電路。AMD有一個(gè)電流分流(額外電流)以對(duì)抗壓降,也可以拉伸時(shí)鐘。相同的LDO設(shè)計(jì)允許單個(gè)核心線性調(diào)節(jié),通過(guò)調(diào)整每個(gè)核心的電壓來(lái)實(shí)現(xiàn)節(jié)能。

概念驗(yàn)證處理器有96個(gè)核和一個(gè)有源插入器

會(huì)議中的一個(gè)非生產(chǎn)芯片是一個(gè)96核的處理器,也使用了chiplets策略,但是當(dāng)AMD使用一個(gè)專用I/O芯片的多芯片模塊時(shí),這個(gè)芯片使用了一個(gè)有源硅插入器,將I/O邏輯放入插入器。

該設(shè)計(jì)使用6個(gè)chiplet,從96個(gè)核中獲得220個(gè)GOPS。它由CEA-Leti設(shè)計(jì),ST Micro制造。這里的想法是要證明這一概念使用兩種die設(shè)計(jì):chiplet和有源插入器。雖然本設(shè)計(jì)使用同構(gòu)芯片,但未來(lái)的設(shè)計(jì)可以使用異構(gòu)處理元素。與AMD EPYC設(shè)計(jì)一樣,CEA的目標(biāo)是添加更多的處理元素,單個(gè)die不足以交付所需的處理。其中一種應(yīng)用可能是汽車自動(dòng)駕駛,這將需要數(shù)百個(gè)GOPS。

使用有源插入器,可以去除許多在老的流程節(jié)點(diǎn)中運(yùn)行的功能,包括電源管理、內(nèi)存接口和I/O。在這個(gè)特殊的設(shè)計(jì)中,CEA使用了一個(gè)2D網(wǎng)格的分布式互連。有源插入器上的互連混合使用了短距離的無(wú)源通道和長(zhǎng)時(shí)間的有源通道。本設(shè)計(jì)還采用了一種新穎的異步QDI邏輯與芯片上的異步網(wǎng)絡(luò)進(jìn)行通信。

這款處理器上的chiplet采用FDSOI 28nm LPLV制造,有源插層采用了65 nm工藝。雖然這種芯片使用的是較老的工藝節(jié)點(diǎn),但其目標(biāo)是展示如何構(gòu)建和制造它。芯片測(cè)試使用傳統(tǒng)的已知良好的技術(shù),但有源插入器只在所有元素組裝后做了測(cè)試。如果完全投入生產(chǎn),通過(guò)使用更高級(jí)的流程節(jié)點(diǎn),生產(chǎn)流程可能會(huì)有所不同。

責(zé)任編輯:pj

-

半導(dǎo)體行業(yè)

+關(guān)注

關(guān)注

10文章

403瀏覽量

41136 -

服務(wù)器處理器

+關(guān)注

關(guān)注

0文章

13瀏覽量

12356

發(fā)布評(píng)論請(qǐng)先 登錄

國(guó)民技術(shù)能否開(kāi)展一個(gè)M7處理器的試用活動(dòng)。

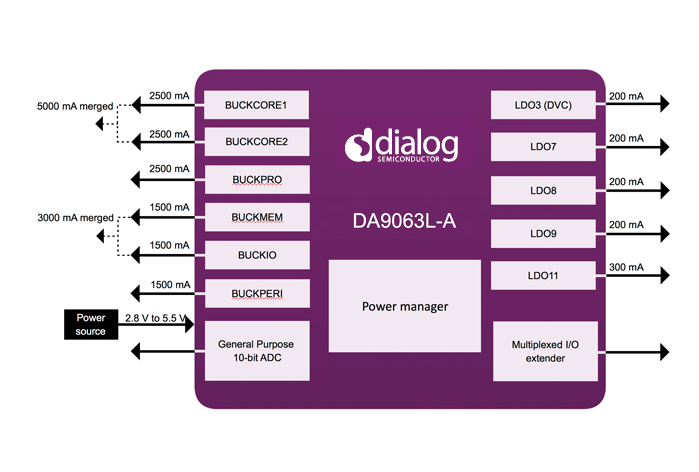

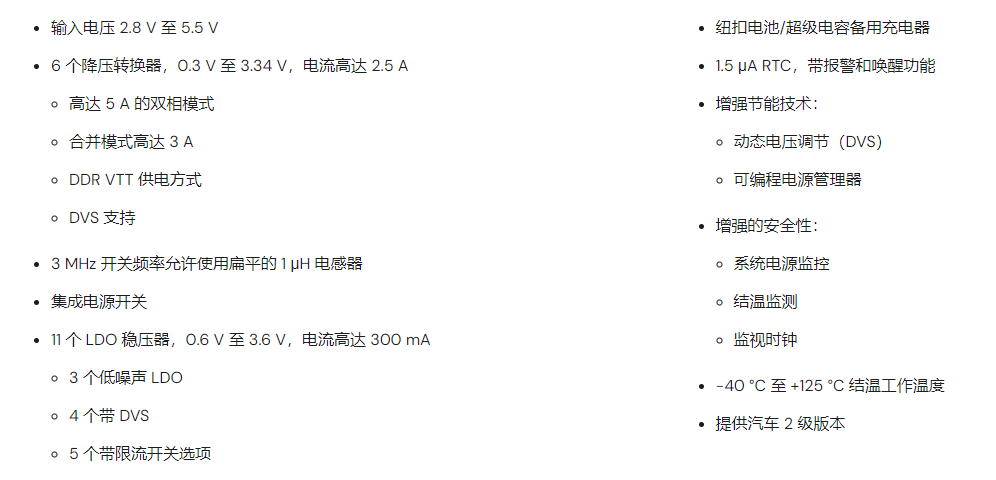

適用于單核、雙核和四核應(yīng)用處理器的PMIC DA9063L-A數(shù)據(jù)手冊(cè)

用于四核應(yīng)用處理器的可編程DA9063 PMIC數(shù)據(jù)手冊(cè)

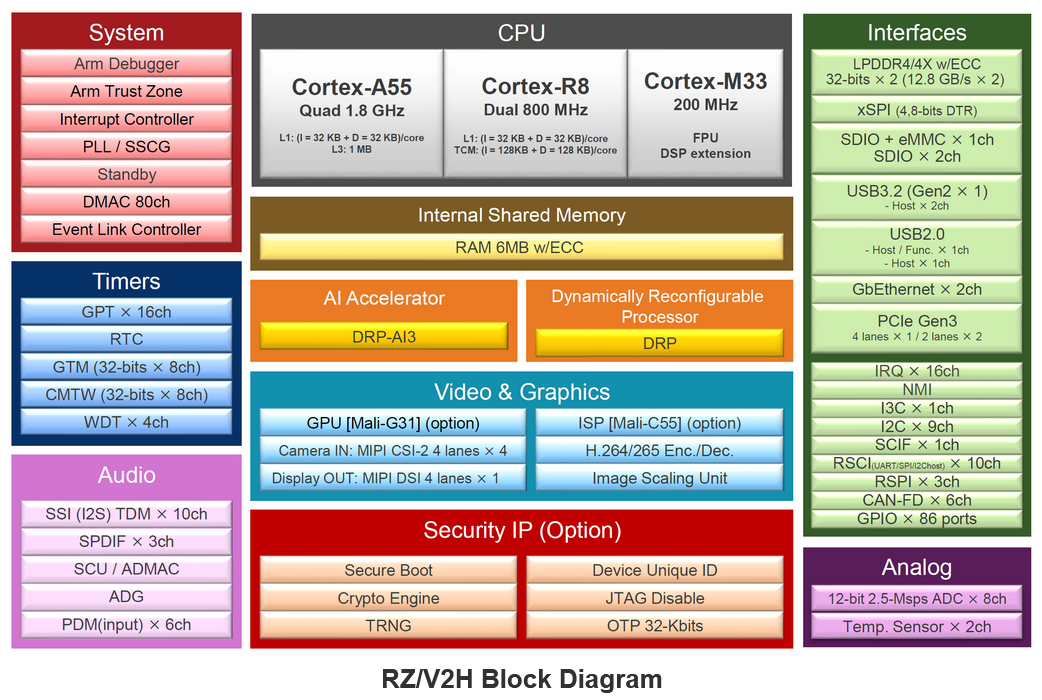

AI MPU# 瑞薩RZ/V2H 四核視覺(jué) ,采用 DRP-AI3 加速器和高性能實(shí)時(shí)處理器

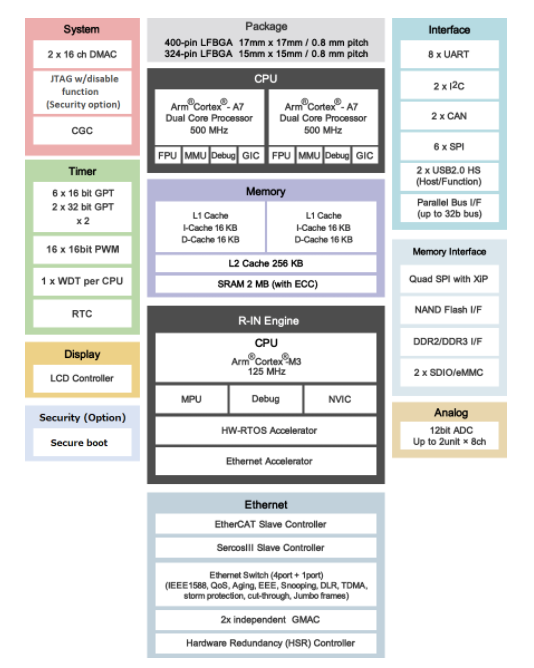

具有5個(gè)以太網(wǎng)端口和工業(yè)網(wǎng)絡(luò)主設(shè)備冗余協(xié)議的RZ/N1D微處理器數(shù)據(jù)手冊(cè)

量子處理器的作用_量子處理器的優(yōu)缺點(diǎn)

盛顯科技:異形拼接處理器和傳統(tǒng)拼接處理器有什么區(qū)別?

RK3566高性能低功耗四核應(yīng)用處理器數(shù)據(jù)手冊(cè)

MicroBlaze V軟核處理器的功能特性

微處理機(jī)和微處理器的區(qū)別

對(duì)稱多處理器和非對(duì)稱多處理器的區(qū)別

微處理器的指令集和指令系統(tǒng)有什么不同

今日看點(diǎn)丨高通驍龍 X Plus 8 核處理器發(fā)布;2025 款比亞迪漢將于明日上市

圖像處理器與計(jì)算機(jī)視覺(jué)有什么關(guān)系和區(qū)別

OMAP5910雙核處理器數(shù)據(jù)表

概念驗(yàn)證處理器為什么有96個(gè)核和一個(gè)有源插入器?

概念驗(yàn)證處理器為什么有96個(gè)核和一個(gè)有源插入器?

評(píng)論