從上世紀 60 到 90 年代末,制程工藝命名是根據芯片中柵極長度命名。

長期以來,柵極長度(晶體管柵極的長度)和半間距(芯片上兩個相同特征之間的距離的一半)與過程節點名稱相匹配,但最后一次以柵極長度命名是 1997 年。間距數繼續與節點名匹配,但從實際意義上不再與之相關。

如果我們能夠達到幾何比例縮放要求使節點名稱和實際尺寸大小保持同步,那么六年前我們芯片制程就會是 1nm 以下。我們用來表示每個新節點的數字只是公司選擇的數字。早在 2010 年,ITRS(稍后將對此進行詳細介紹)將在每個節點上轉儲的技術稱為“等效擴展”。

市場如何改變了制程?

當芯片制程接近納米級的極限時,公司可能會開始使用埃米而不是納米,或可能會簡單地使用小數點進行標注。早期,制程以微米而不是 nm(例如,以 0.18 微米或 0.13 微米,而不是 180nm 或 130nm)為單位的標注制程尺寸更為普遍。

無論從資本還是技術投入的角度出發,半導體制程都無疑是一個深投入、慢產出的領域。一項新技術,從論文階段發展到大規模商用,平均需耗費 10-15 年時間。

幾十年前,半導體行業認識到,如果針對節點引入通用的路線圖,并規范這些節點所使用的通用特征尺寸,這將有助于解決新節點推入市場時的規模和協同性問題。多年來,ITRS(國際半導體技術路線圖)都負責發布行業總路線圖,周期長達 15 年之久,為半導體市場設定了總體目標。

2013-2014 年間,ITRS 發布了 ITRS 2.0 版本,但很快意識到覆蓋范圍不足的問題。為了給大學、財團和行業研究人員提供更為完善的藍圖參考,以激發各個技術領域的創新,ITRS 又成立了一個新的組織,稱為 IRDS(設備和系統的國際路線圖),其職責范圍更大,技術覆蓋面也更廣。

覆蓋面和重點轉移反映整個芯片制造行業正在發生的變革。停止將柵極長度或半節距與節點大小綁定的原因是,它們不是在縮小規模就是在縮小規模的路上。作為替代方案,芯片公司集成了各種新技術和制造方法,從而跟進節點控制的腳步。

在 40 / 45nm 節點處,要與后者統一,GlobalFoundries 和臺積電等推出浸沒式光刻技術。在 32nm 節點處,引入雙重曝光技術。在 28nm 節點處,引入后柵極技術。此外,FinFET 是由 Intel 在 22nm 節點處引入的技術,而其他公司則是在 14 / 16nm 處開始使用該技術。

不同的芯片公司有時會在不同的時間節點導入新工藝技術。當 AMD 和臺積電在 40 / 45nm 節點處采用浸沒式光刻技術時,英特爾并沒有作出同樣的選擇,直到 32nm 工藝節點時,它才開始選用浸沒式光刻技術,并選擇首推雙重曝光技術。

接著,GlobalFoundries 和臺積電在 32 / 28nm 節點處開始更多地采用雙重曝光技術。在 28nm 節點處,臺積電采用的是后柵極技術,而三星和 GlobalFoundries 則采用的是前柵極技術。

但是,隨著進展變得越來越慢,公司對于營銷的依賴在加大,于是出現了許多公司自己命名的“節點”,擾亂了大家的視線。比如像三星,也開始在 90、65、45nm 節點后開始以自身技術的迭代來命名新的節點。

每個制程節點都會有升級的空間,但已經不是按照摩爾定律來了。

現在盡管節點名稱不與任何特征尺寸相關聯,并且某些特征尺寸已停止擴展,但半導體制造商仍在尋找改善關鍵指標的方法,這也是真正的工藝改進。

但是,由于現在技術很難獲得更多的優勢,并且需要更長的開發時間,因此芯片公司正在嘗試更多的改進方法。例如,三星正在部署比以前更多的芯片制程名稱,這就是市場營銷。

為什么人們聲稱 Intel 10nm 和 TSMC / Samsung 7nm 是等效的?

英特爾 10nm 制造參數非常接近臺積電和三星用于 7nm 制程的值。下圖來自 WikiChip,展示了英特爾 10nm 節點的已知特征尺寸,和臺積電、三星 7nm 節點的已知特征尺寸對比情況。

14nm ?/ 10nm?列顯示了每個公司從其上一個節點開始將特定功能擴展的程度。英特爾和三星的金屬最小間距比臺積電更嚴格,但臺積電的高密度 SRAM 單元比英特爾小,這可能反映了臺灣代工廠的不同客戶的需求。同時,三星的手機甚至比臺積電的手機還要小。

總體而言,英特爾的 10nm 工藝達到的許多關鍵指標,臺積電和三星都將其稱為 7nm。

針對特定的設計目標,單顆芯片的特征尺寸可能仍將偏離這些既有數據。制造商提供的這些數字是給定節點上的典型預期實現方式,不一定與某些特定芯片完全匹配。

有人質疑英特爾 10nm +工藝(用于 Ice Lake)參數(針對 Cannon Lake 發布)。其預期規格可能略有變化,但往上推,當年 14nm+也是從 14nm 演變過來的。英特爾已經表示,仍將針對 10nm 的 2.7 倍減小(相對于 14nm)作為目標,因此將暫緩任何有關下一步 10nm +演進可能有不同的猜測。

責任編輯:tzh

-

芯片

+關注

關注

460文章

52529瀏覽量

441363 -

半導體

+關注

關注

335文章

28938瀏覽量

238452 -

晶體

+關注

關注

2文章

1391瀏覽量

36375

發布評論請先 登錄

如何集成第三方支付API到電商網站

天合跟蹤獲得DNV第三方風洞測試審查報告

小鵬汽車出席東盟-中國-海合會三方經濟論壇

京東App上線國內打車服務,目前為第三方接入

日產、本田、三菱終止三方合作計劃

i.MX8M Yocto工程更新第三方軟件包

電信SD-WAN對比三方跨境線路方面有何優勢?

EE-303:將VisualDSP線程安全庫與第三方RTOS配合使用

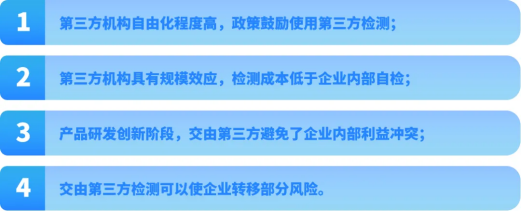

第三方檢測機構該如何提升核心競爭力?

億緯鋰能與武漢大學、德布勒森大學簽署三方合作諒解備忘錄

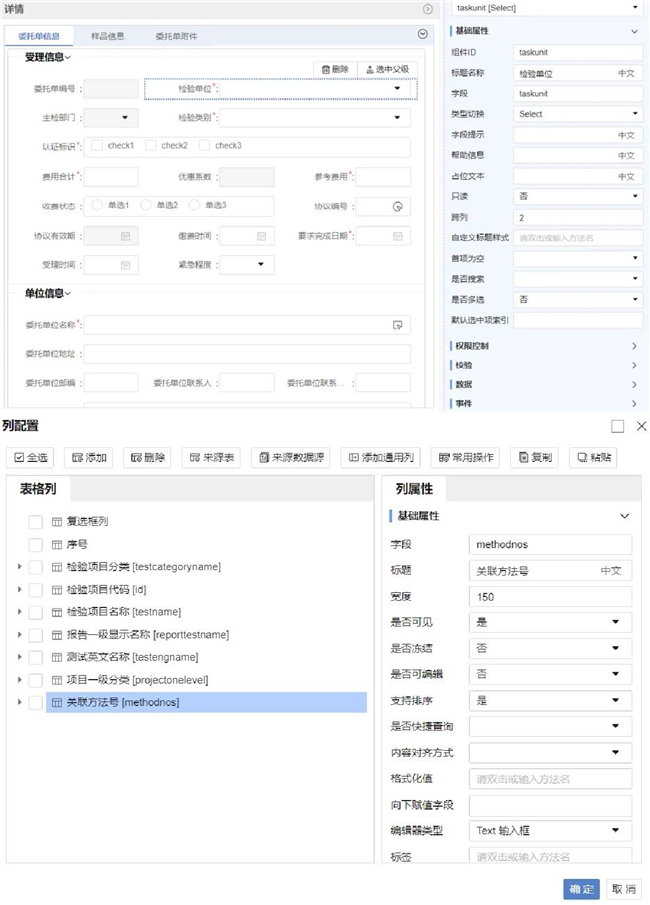

三維天地低代碼開發平臺助力第三方質檢行業數據可視化

對三方制程工藝節點等方面進行的探索

對三方制程工藝節點等方面進行的探索

評論