隨著集成電路的不斷發(fā)展,可編程邏輯器件FPGA因其功能強大,設(shè)計靈活,開發(fā)周期短等特點,得到越來越廣泛的應(yīng)用。于是片上可編程系統(tǒng)(System On Programmable Chip,SOPC)的設(shè)計方法也越來越受到重視。SOPC將微處理器、存儲器、定時器、通用I/O接口等系統(tǒng)設(shè)計必需的功能模塊以及用戶設(shè)計的有特定功能的模塊集成到一片可編程邏輯器件上,構(gòu)建一個具備軟,硬件在系統(tǒng)可編程功能的可編程片上系統(tǒng)。這種非常靈活的電路設(shè)計方式使得對整個電路系統(tǒng)的裁減、擴充、升級變的很容易。這樣可以縮短電路設(shè)計的開發(fā)周期,節(jié)省開發(fā)成本。MicroBlaze作為Xilinx公司開發(fā)的32位哈佛結(jié)構(gòu)RISC型軟核處理器,適用于其所有現(xiàn)產(chǎn)的FPGA器件。采用這種“微處理器+可編程邏輯”的SOPC系統(tǒng)架構(gòu),用戶可方便的在系統(tǒng)中加入各種IP核,實現(xiàn)具有特定功能的,易配置、易擴展、易繼承的片上系統(tǒng)。

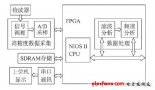

文中提出一種基于SOPC技術(shù)的多路數(shù)據(jù)采集與存儲系統(tǒng)的設(shè)計方法,利用硬件描述語言設(shè)計用戶IP核,實現(xiàn)硬件控制數(shù)據(jù)采集和存儲的功能。加上Xilinx公司一些必要的標準IP核可以生成嵌入式系統(tǒng)。這種可以方便地把用戶自定義的邏輯加入到系統(tǒng)中的設(shè)計,體現(xiàn)了用SOPC設(shè)計嵌入式系統(tǒng)的靈活性。

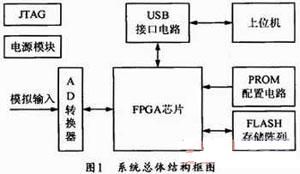

1 系統(tǒng)總體結(jié)構(gòu)

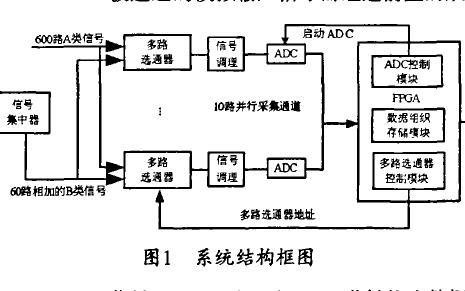

整個系統(tǒng)由xilinx公司的spartan3E高性能、低成本的90nm FPGA和一些外圍電路組成。主要有AD轉(zhuǎn)換器、FLASH存儲器、系統(tǒng)PROM配置電路和電源模塊等,其系統(tǒng)總體結(jié)構(gòu)如圖1所示。

系統(tǒng)核心采用嵌入式技術(shù),在一片芯片上實現(xiàn),它包含Xilinx公司的一些標準總線IP核如中斷控制器,通用輸入輸出端口等模塊和帶有PLB總線接口的用戶自定義的數(shù)據(jù)采集與存儲IP核。其中用戶自定義的IP核是用VHDL語言設(shè)計的,它包含AD控制邏輯、FLASH控制邏輯、DMA傳輸控制邏輯和FIFO緩存模塊等。

整個系統(tǒng)設(shè)計可以分為硬件設(shè)計和軟件設(shè)計兩個部分。利用SOPC技術(shù)結(jié)合VHDL硬件描述語言,在芯片內(nèi)部設(shè)計硬件控制系統(tǒng);利用EDK(嵌入式開發(fā)套件)為特定硬件配置自動生成的軟件包結(jié)合C語言,設(shè)計基于Microblaze處理器的軟件控制程序。

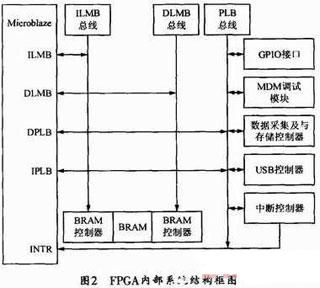

2 系統(tǒng)結(jié)構(gòu)

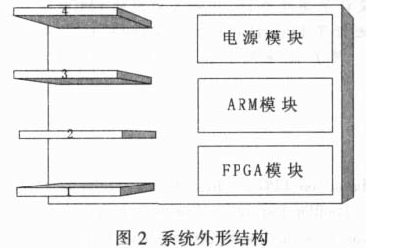

FPGA的硬件設(shè)計先確定要用的外部接口,然后進行IP核設(shè)計,將IP核的邏輯功能映射到FPGA芯片上。其系統(tǒng)結(jié)構(gòu)框圖如圖2所示。

2.1 AD轉(zhuǎn)換芯片

AD轉(zhuǎn)換器采用MAXIM公司的MAXIM1308芯片,它是12位模數(shù)轉(zhuǎn)換器(ADC)提供8個獨立輸入通道,獨立的采樣保持(T/H)電路為每個通道提供同時采樣,提供+5V輸入范圍,20MHz、12位雙向并行數(shù)據(jù)總線用來提供轉(zhuǎn)換結(jié)果,并可接受數(shù)字輸入來單獨配置每一通道的開啟和關(guān)閉。

2.2 FLASH存儲器

FLASH存儲器芯片采用8片三星公司的K9XXG08UXA系列的NAND Flash存儲器,該存儲器是按頁進行讀寫按塊擦除,通過I/O管腳分時復(fù)用發(fā)送命令/地址/數(shù)據(jù)。每片的存儲容量為512MB。存儲過程使用流水線方式對數(shù)據(jù)進行存儲。

2.3 FPGA配置電路

Xilinx公司的FPGA器件是基于SRAM的內(nèi)部結(jié)構(gòu),掉電后FPGA的內(nèi)部邏輯丟失,因此外部需要一個配置芯片在每次上電時可以將配置數(shù)據(jù)加載到FPGA器件的內(nèi)部SRAM中。配置芯片采用的是XCF04系列PROM串行配置芯片。當(dāng)系統(tǒng)上電時,芯片以主動配置方式來實現(xiàn)系統(tǒng)中FPGA的硬件配置。通過高速的串行接口,整個芯片的配置工作可以在很短的時間內(nèi)完成。

2.4 系統(tǒng)電源模塊

電源模塊的設(shè)計不僅需要為器件提供各種高性能的功率輸出,還要包括選擇合適的旁路、去耦電容,以濾除各種干擾信號,保證系統(tǒng)的穩(wěn)定工作。Xilinx公司Spartan-3E XC3S500E FPGA需要三種電壓供電才能正常工作:VCCAUX:1.2V±5%,VCCAUX:2.5V±5%,VCCO:3.3V±5%。利用TI公司TPS75003芯片加上必要的外圍電路作為該系統(tǒng)的完整的電源解決方案。

2.5 USB接口芯片

USB芯片使用由FTDI公司推出的FT245R,該芯片主要完成USB串行總線和8位并行FIFO接口之間的相互協(xié)議轉(zhuǎn)換。整個USB通信協(xié)議全部由芯片自動完成,無須考慮底層固件的編程。該芯片可以使用內(nèi)部集成的時鐘電路進行工作,也可以使用外部晶振,本系統(tǒng)中使用外部晶振。完全兼容USB2.0協(xié)議。它有256字節(jié)的接收緩沖區(qū)和128個發(fā)送緩沖區(qū),可以進行數(shù)據(jù)的大吞吐量操作。通過8位并行數(shù)據(jù)口D[0:7]和4位讀寫狀態(tài)/控制口RXF、TXE、RD、WR就可實現(xiàn)與微控制器的數(shù)據(jù)交換。

3 FPGA系統(tǒng)硬件設(shè)計

Xilinx公司EDK(嵌入式開發(fā)套件)的XPS(平臺工作室)的系統(tǒng)組建面板以展開式的樹和表形式顯示所有硬件平臺IP實例,因此用戶可以方便地查看自己的嵌入式設(shè)計。在此面板中可以對IP元素、端口、屬性以及參數(shù)進行配置。

3.1 用戶IP核設(shè)計

使用XPS進行基于MicroBlaze的用戶IP核的開發(fā),該套件集成了硬件平臺產(chǎn)生器、軟件平臺產(chǎn)生器、仿真模型生成器、軟件編譯器和軟件調(diào)試工具等。

為實現(xiàn)系統(tǒng)功能,需自定義一個IP核實現(xiàn)數(shù)據(jù)的采集與存儲:該IP核包括五部分,分別為PLB總線接口模塊、數(shù)據(jù)采集模塊、數(shù)據(jù)緩存模塊、數(shù)據(jù)存儲模塊FLASH讀寫控制邏輯。

(1)數(shù)據(jù)采集模塊:利用FPGA邏輯資源實現(xiàn)A/D采集電路的控制邏輯。在功能上,該AD控制邏輯相當(dāng)于一個主控制器。該控制過程無需處理器參與。另外AD控制邏輯與AD數(shù)據(jù)接口的分離,使得高速采集與發(fā)送數(shù)據(jù)成為可能。它連接兩片12位的8通道MAXIM1308轉(zhuǎn)換器,可實現(xiàn)多通道的數(shù)據(jù)采集。

(2)數(shù)據(jù)緩存模塊:在FPGA內(nèi)部設(shè)計FIFO將AD轉(zhuǎn)換后的數(shù)據(jù)暫時存放其中。FIFO是Xilinx以FPGA片上Blockram為資源生成,F(xiàn)IFO模塊的主要功能是數(shù)據(jù)緩沖,實現(xiàn)速率匹配。該異步FIFO模塊在FIFO讀、寫控制模塊的控制之下進行異步讀寫,F(xiàn)IFO的讀時鐘受數(shù)據(jù)存儲模塊控制,寫時鐘受數(shù)據(jù)采集模塊的控制。FPGA內(nèi)部設(shè)計了兩片12位的FIFO與上述兩片AD轉(zhuǎn)換器相對應(yīng)。

(3)數(shù)據(jù)存儲模塊:對本系統(tǒng)使用VHDL語言專門設(shè)一個DMA控制器來連接FIFO緩存和外部FLASH存儲陣列。當(dāng)FIFO緩存容量達到一定的值時可以啟動DMA控制器建立一個高速的通道以提供連續(xù)的數(shù)據(jù)傳輸,存儲到FPGA外部FLASH存儲器陣列。這個通道使得只要FIFO緩存中的數(shù)據(jù)達到一定的值時便能迅速地存儲到外部FLASH中,主設(shè)備不必為了確定從端口是否能夠發(fā)送或接收數(shù)據(jù)而不斷地訪問從外設(shè)的狀態(tài)寄存器。這使得系統(tǒng)的整體效率有了較大的提高,同時避免了自定義外設(shè)FIFO中的數(shù)據(jù)上溢或下溢。并且該過程只需要Microblaze處理器很少的干預(yù)即可完成,極大地節(jié)省了CPU資源。

(4)FLASH讀寫控制邏輯:主要實現(xiàn)K9XXG08UXA系列的NAND Flash存儲器的讀寫時序,完成對FLASH的操作。

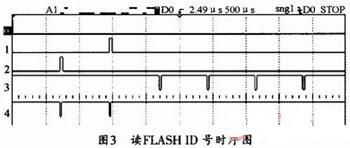

在SOPC硬件系統(tǒng)設(shè)計過程中用戶IP核的設(shè)計是關(guān)鍵,它的設(shè)計是否成功決定著整個系統(tǒng)設(shè)計是否可行。在用戶IP核設(shè)計過程中AD控制器、FLASH控制器、DMA控制器的設(shè)計都比較成功的,圖3是對用戶IP核設(shè)計的部分驗證:示波器捕獲的讀FLASH存儲器ID號時序圖,且實驗證明讀出來的FLASH存儲器的ID號是正確的。其中通道0—4分別代表FLASH的CE(片選)、ALE(地址鎖存)、CLE(命令鎖存)、RE(讀)、WE(寫)信號。

3.2 設(shè)計生成FPGA硬件系統(tǒng)

在XPS嵌入式開發(fā)環(huán)境中將用戶IP核和標準總線核添加到系統(tǒng)中并將它們互相按規(guī)則連接起來。XPS提供了一個交互式的開發(fā)環(huán)境,允許用戶對硬件平臺各個方面進行設(shè)置。其中,XPS在高層對硬件平臺描述進行維護,此高層形式即為微處理器硬件規(guī)范(MHS)文件。MHS文件作為一個可以編輯的文本文件,是表示用戶嵌入式系統(tǒng)硬件部分的主要源文件。XPS將MHS文件綜合到硬件描述語言網(wǎng)表中,用于FPGA的布局布線形成FPGA系統(tǒng)的硬件結(jié)構(gòu),該過程即是生成硬件比特流的階段,形成后綴名為.bit的文件。

4 結(jié)束語

本文介紹了基于SOPC的多通道數(shù)據(jù)采集系統(tǒng)設(shè)計,可以對多種關(guān)心的環(huán)境參數(shù)進行采集并研究其特性。利用MicroBlaze微處理器搭建數(shù)據(jù)此采集與存儲的嵌入式可編程片上系統(tǒng),可以由單個芯片完成整個系統(tǒng)的主要邏輯功能。便于系統(tǒng)實現(xiàn)小型化,集成化。這種靈活的設(shè)計方式可隨意擴展系統(tǒng)功能。在此基礎(chǔ)上嵌入操作系統(tǒng),可以進一步開發(fā)功能更強大的實時數(shù)據(jù)采集設(shè)備。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615358 -

芯片

+關(guān)注

關(guān)注

459文章

52306瀏覽量

437757 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

40文章

7038瀏覽量

115952

發(fā)布評論請先 登錄

LabVIEW編程語言實現(xiàn)振動信號的多通道數(shù)據(jù)采集

如何利用FPGA和VHDL語言實現(xiàn)PCM碼的解調(diào)?

基于PC的多通道自帶緩存數(shù)據(jù)采集系統(tǒng)的設(shè)計與實現(xiàn)

基于CVI的多通道數(shù)據(jù)采集系統(tǒng)

基于FPGA的多通道同步數(shù)據(jù)采集存儲系統(tǒng)

SOPC基礎(chǔ)上的數(shù)據(jù)采集系統(tǒng)設(shè)計

基于SOPC的數(shù)據(jù)采集與處理系統(tǒng)設(shè)計

基于SOPC技術(shù)的數(shù)據(jù)采集系統(tǒng)設(shè)計

如何使用FPGA進行超多通道高速數(shù)據(jù)采集系統(tǒng)的構(gòu)成和設(shè)計過程資料概述

如何使用FPGA進行多通道同步數(shù)據(jù)采集系統(tǒng)的設(shè)計

使用LabVIEW實現(xiàn)多通道數(shù)據(jù)采集系統(tǒng)的資料概述

利用SOPC技術(shù)結(jié)合VHDL語言實現(xiàn)多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計

利用SOPC技術(shù)結(jié)合VHDL語言實現(xiàn)多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計

評論