本文可以了解什么?

DDR-DDR4內存模塊的差異以及對比;

邏輯BANK的概念與定義;

芯片的位寬的解釋。

下圖是DDR3的PHY IP Core的定義規范。

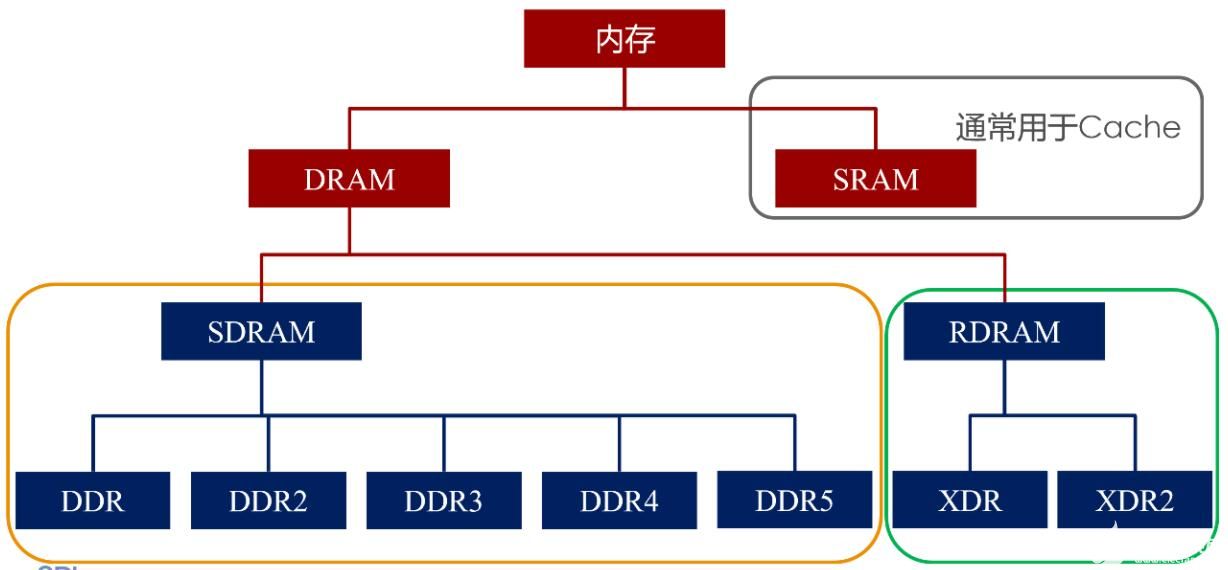

DDR-DDR4的物理結構差異

首先,我們來對比一下DDR, DDR2, DDR3 SDRAM, and DDR4 SDRAM物理結構上的差別,如下圖所示。

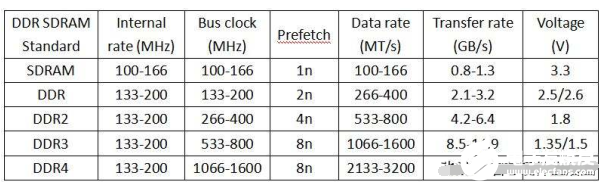

下表是SDRAM-DDR4前后的電壓,時鐘,速率的對比詳圖。

SDRAM, DDR1, DDR2, DDR3以及DDR4對比表

邏輯BANK與芯片位寬

我們平時看到的SDRAM都是以模組形式出現,即便是手機或者pad中的內存單元,一般一會是好幾顆,為什么要做成這種形式呢?要解釋這個問題,首先要接觸到兩個概念:物理Bank與芯片位寬。

1、邏輯Bank

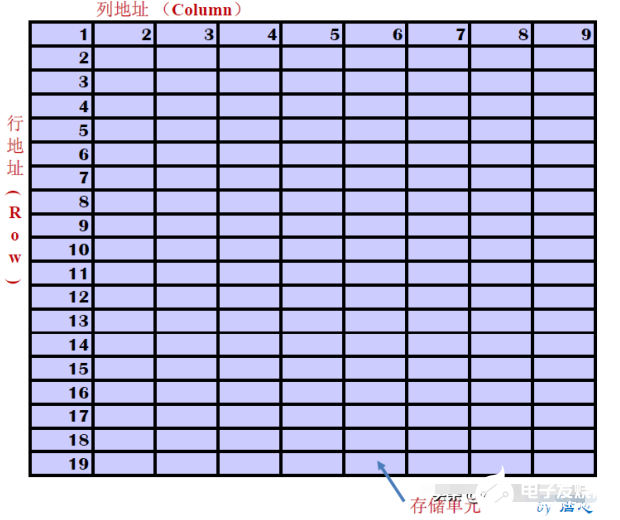

簡單地說,SDRAM的內部是一個存儲陣列。由于采用管道式存儲(如同排隊買票),就很難做到隨機訪問了。

陣列就如同表格一樣,將數據“填”進去,你可以它想象成一張表格。和表格的檢索原理一樣,先指定一個行(Row),再指定一個列(Column),我們就可以準確定位所需要的單元格,這就是內存芯片尋址的基本原理。對于內存來說,這個單元格可稱為存儲單元,那么這個表格(存儲陣列)我們就稱之為邏輯Bank(Logical Bank)。

由于SDRAM的工作原理限制,單一的邏輯Bank將會造成非常嚴重的尋址沖突,大幅降低內存效率,因此由于技術、成本等各方面原因,不可能一顆芯片只做一個全容量的邏輯Bank。所以架構師在SDRAM內部分割成多個L-Bank,在DDR2的標準中,邏輯Bank的數量是8個。

這樣一來,在進行尋址時就要先確定是哪個邏輯Bank,然后再在這個選定的邏輯Bank中選擇相應的行與列定位內存單元進行尋址。可見對內存的訪問,一次只能是一個邏輯Bank工作,而每次交換的數據就是邏輯Bank存儲陣列中一個“存儲單元”的容量。

2、芯片位寬

傳統內存系統為了保證CPU的正常工作,必須一次傳輸完CPU在一個傳輸周期內所需要的數據。而CPU在一個傳輸周期能接受的數據容量就是CPU數據總線的位寬,單位是bit(位)。當時控制內存與CPU之間數據交換的芯片也因此將內存總線的數據位寬等同于CPU數據總線的位寬,內存的位寬需要與CPU對應,才能正常運行。

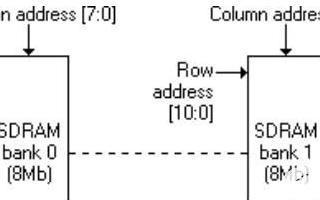

SDRAM內存系統必須要組成一個物理Bank的位寬,才能使CPU正常工作,那么這個物理Bank位寬怎么得到呢?這就涉及到了內存芯片的結構。

每個內存芯片也有自己的位寬,即每個傳輸周期能提供的數據量。理論上,完全可以做出一個位寬為64bit的芯片來滿足物理Bank的需要,但這對技術的要求很高,在成本和實用性方面也都處于劣勢。所以芯片的位寬一般都較小。對于臺式機市場所用的SDRAM芯片位寬最高也就是16bit,常見的則是8bit。這樣,為了組成物理Bank所需的位寬,就需要多顆芯片并聯工作。對于16bit芯片,需要4顆(4×16bit=64bit)。對于8bit芯片,則就需要8顆了。

這樣大概可以說清楚芯片位寬、芯片數量與物理Bank的關系。物理Bank其實就是一組內存芯片的集合,這個集合的容量不限,但這個集合的總位寬必須與CPU數據位寬相符。

責編AJX

-

芯片

+關注

關注

459文章

52203瀏覽量

436433 -

RAM

+關注

關注

8文章

1391瀏覽量

116829 -

內存

+關注

關注

8文章

3109瀏覽量

75003

發布評論請先 登錄

DDR SDRAM與SDRAM的區別

SDRAM內存基礎知識

SDRAM內存基礎指南

什么是SDRAM內存

什么是DDR SDRAM內存

對比靜態SDRAM和動態SDRAM,它們的區別是什么

SDRAM與DDR之間的主要差異是什么

DDR SDRAM和SDRAM功能及結構差異

詳談SDRAM內存模組與差異對比

詳談SDRAM內存模組與差異對比

評論