賽靈思 PCI Express IP 隨附以下集成調(diào)試功能。

- JTAG 調(diào)試器

- 啟用 In-System IBERT

- 第三代模式解擾器

“JTAG 調(diào)試器 (JTAG Debugger)”可提供以下信息來幫助調(diào)試 PCI Express 鏈接訓(xùn)練問題:

LTSSM 狀態(tài)的圖形化視圖

基于 GUI 的接收器檢測(cè)狀態(tài)(對(duì)應(yīng)已配置的每個(gè)通道)

PHY RST 狀態(tài)機(jī)的狀態(tài)

In-system IBERT 可提供 PCIe 鏈接眼圖。“JTAG Debugger”和“In-system IBERT”功能結(jié)合在一起即可提供即時(shí)信息,用于判斷鏈接訓(xùn)練問題的可能原因。在本篇博文中,我們將講解如何使用這些功能。本篇博文基于賽靈思 VCU118 開發(fā)板隨附的 UltraScale+ 器件。

“第三代模式解擾器 (Gen3 Mode Descrambler)”選項(xiàng)可提供發(fā)生擾碼的 PIPE 數(shù)據(jù)的解碼接口。它允許用戶查看 PCIe 鏈接上的數(shù)據(jù)包。如需了解有關(guān)該功能以及數(shù)據(jù)包解碼方法的詳細(xì)信息,請(qǐng)參閱博文。

https://forums.xilinx.com/t5/Design-and-Debug-Techniques-Blog/Demystifyi...

IP 配置 GUI 包含“添加調(diào)試選項(xiàng) (Add. Debug Options)”選項(xiàng)卡。請(qǐng)選中“啟用 JTAG 調(diào)試器 (Enable JTAG Debugger)”。

在GUI 中配置其它 IP 參數(shù)后,生成 IP 并打開示例設(shè)計(jì)。

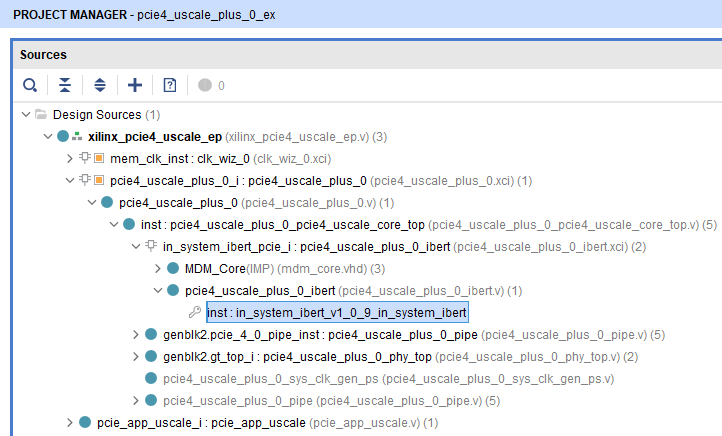

請(qǐng)確保在設(shè)計(jì)示例的“Design Sources”層級(jí)中包含調(diào)試封裝模塊,如下所示:

請(qǐng)選擇正確的比特文件和 .ltx 文件,以生成比特流并對(duì)器件進(jìn)行編程。

根據(jù)所使用的 Vivado 工具版本,您可能會(huì)看到如下錯(cuò)誤。

如果看到以上錯(cuò)誤消息,請(qǐng)?jiān)?Vivado Tcl Console 中運(yùn)行以下命令。

set_param xicom.use_bitstream_version_check false

對(duì)器件重新進(jìn)行編程。

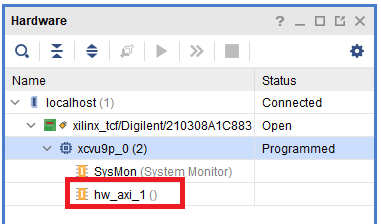

成功完成目標(biāo)器件編程后,應(yīng)在硬件窗口中顯示 AXI 核“hw_axi_1”。

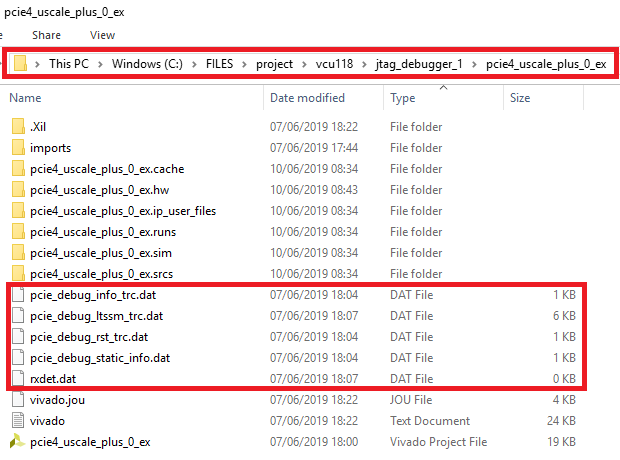

在工程目錄中如下所示位置下,您將找到 4 個(gè) .tcl 文件。

“test_rd.tcl”文件可讀取 BRAM 中存儲(chǔ)的調(diào)試數(shù)據(jù),并輸出 *.dat 文件,如下所示。其它 Tcl 文件可讀取這些 *.dat 文件,以分別繪制 LTSSM、PHY RST 狀態(tài)機(jī)和“接收器檢測(cè) (Receiver Detect)”的圖形化視圖。

draw_ltssm.tcl、draw_reset.tcl 和 draw_rxdet.tcl 腳本將使用 ActiveTcl 來執(zhí)行。

如果您嘗試在 Vivado Tcl Console 中執(zhí)行這些腳本,那么 Vivado 工具將出錯(cuò)并退出。

下圖顯示了通過“draw_ltssm.tcl”腳本生成的 LTSSM 圖示:

?綠色 - 采集窗口期間轉(zhuǎn)換的狀態(tài)

?橙色 - 最終狀態(tài)

?紅色箭頭 - 最終轉(zhuǎn)換狀態(tài)

?箭頭旁的數(shù)字 - 表示兩個(gè)狀態(tài)之間發(fā)生的轉(zhuǎn)換次數(shù)

上圖來自于某個(gè)有效的案例場(chǎng)景,其中鏈接訓(xùn)練正確無誤并達(dá)成穩(wěn)定的“L0”狀態(tài)。當(dāng)鏈接訓(xùn)練失敗時(shí),“Detect”氣泡可能為橙色,表明 IP 無法檢測(cè)到接收器。同樣,您可能看到某一箭頭旁的數(shù)字較大,表明可能存在不穩(wěn)定的鏈接。

下圖顯示了使用“draw_reset.tcl”腳本生成的 PHY RST 狀態(tài)機(jī)。

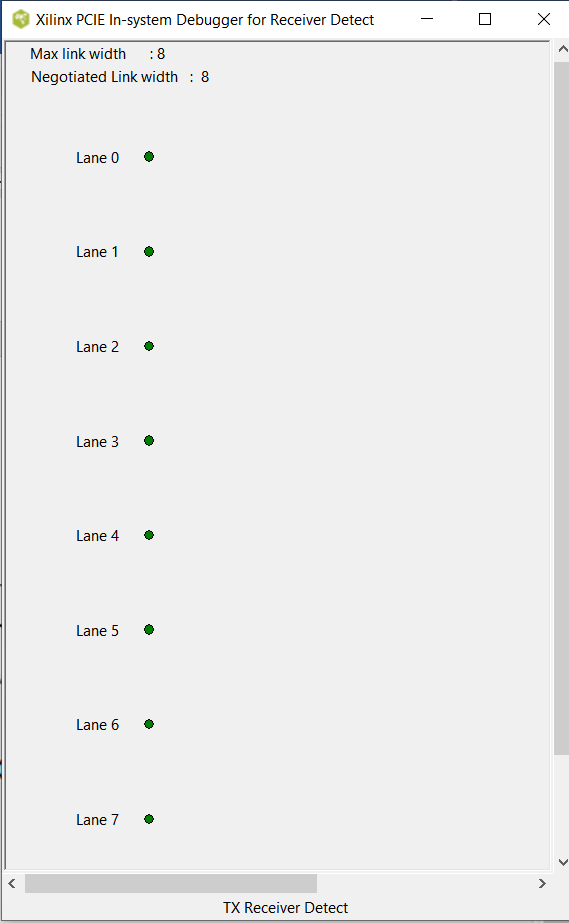

下圖顯示了使用“draw_rxdet.tcl”腳本生成的“Receiver Detect”狀態(tài):

如上所示,綠色點(diǎn)表明對(duì)應(yīng)通道內(nèi)成功完成接收器檢測(cè)。GUI 還可提供有關(guān)協(xié)商的鏈接寬度的信息。

要采集 PCIe 鏈接眼圖,請(qǐng)?jiān)?IP 配置 GUI 的“Add. Debug Options”選項(xiàng)卡中選擇“啟用 In-System IBERT (Enable In-System IBERT)”選項(xiàng)。

與使用“JTAG Debugger”選項(xiàng)時(shí)相似,生成 IP 并打開示例設(shè)計(jì)。

確保在示例設(shè)計(jì)的“Design Sources”層級(jí)中可以看到“System IBERT”模塊。

生成比特流并用比特文件和 .ltx 文件進(jìn)行編程。

以獲取有關(guān) IBERT 掃描必需配置的詳細(xì)信息。下圖顯示了通過“In-System IBERT”功能生成的眼圖。

以上掃描中的眼圖來自于正常運(yùn)行的 PCIe 鏈接。在無效鏈接中,您可能會(huì)看到藍(lán)色區(qū)域極小,表明鏈接中可能存在信號(hào)完整性問題。

如果您在使用調(diào)試功能生成的圖示和眼圖中看到問題,請(qǐng)參閱以下答復(fù)記錄,其中提供了有關(guān)如何調(diào)試 PCIe 鏈接問題的信息。使用調(diào)試功能所獲取的結(jié)果將有助于縮小問題可能原因的范圍,從而簡(jiǎn)化調(diào)試過程。

編輯:hfy

-

接收器

+關(guān)注

關(guān)注

15文章

2563瀏覽量

73542 -

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132173 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1438瀏覽量

96524 -

開發(fā)板

+關(guān)注

關(guān)注

25文章

5589瀏覽量

103128 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

493瀏覽量

28120

發(fā)布評(píng)論請(qǐng)先 登錄

AMD Spartan UltraScale+ FPGA 開始量產(chǎn)出貨

【新品】遠(yuǎn)距離圖傳數(shù)傳模塊開發(fā)板、藍(lán)牙模塊開發(fā)板、無線模塊開發(fā)板

正點(diǎn)原子AU15開發(fā)板資料發(fā)布!板載40G QSFP、PCIe3.0x8和FMC LPC等接口,性能強(qiáng)悍!

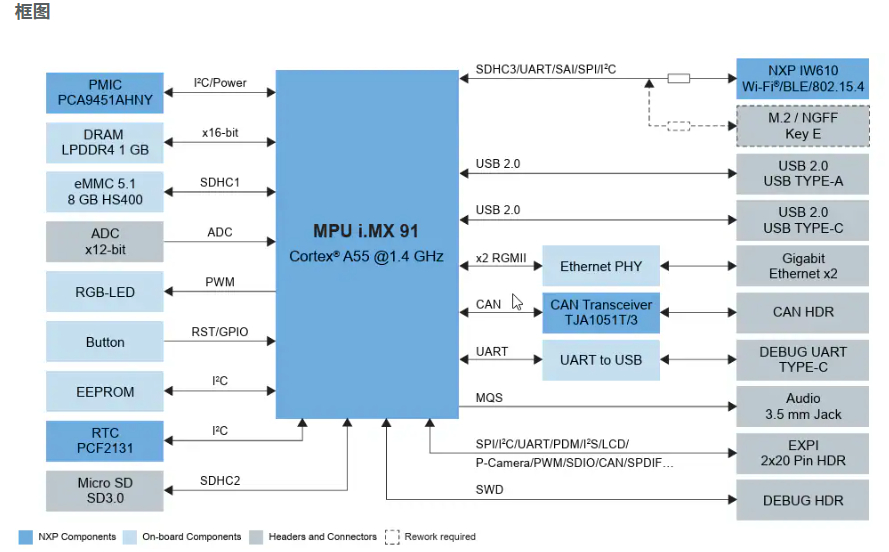

NXP i.MX 91開發(fā)板#支持快速創(chuàng)建基于Linux?的邊緣器件

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

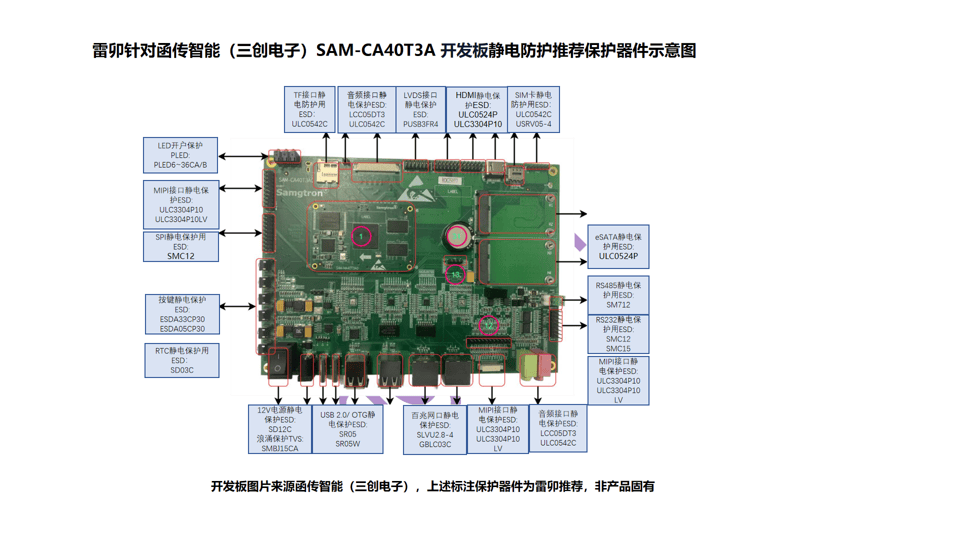

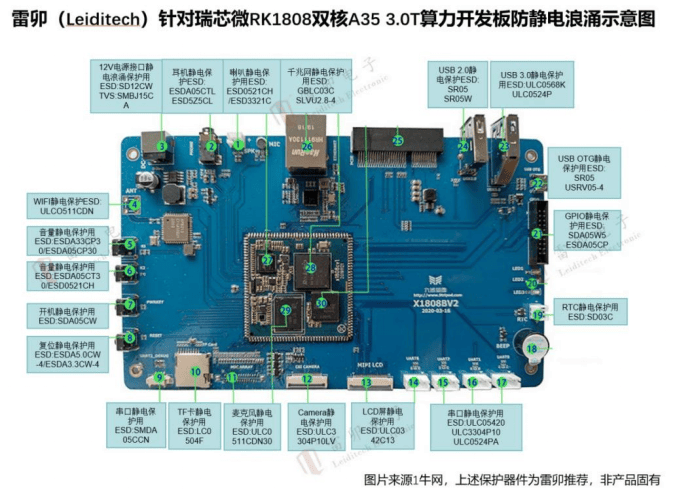

雷卯收集網(wǎng)絡(luò)通信開發(fā)板

雷卯收集增強(qiáng)現(xiàn)實(shí)AR開發(fā)板

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

Zynq UltraScale+ MPSoC數(shù)據(jù)手冊(cè)

ADS54J64EVM開發(fā)板可以配套使用哪些Xilinx FPGA開發(fā)板呢?

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評(píng)估套件

正點(diǎn)原子fpga開發(fā)板不同型號(hào)

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

賽思快訊 | 發(fā)展新質(zhì)生產(chǎn)力問道賽思?賽思如何下好“創(chuàng)新棋”?

基于賽靈思VCU118開發(fā)板隨附的 UltraScale+ 器件

基于賽靈思VCU118開發(fā)板隨附的 UltraScale+ 器件

評(píng)論