一、擾碼的作用

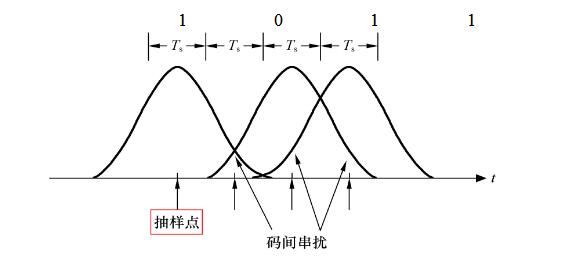

對數字信號的比特進行隨機處理,減少連0和連1的出現,從而減少碼間干擾和抖動,方便接收端的時鐘提取;同時又擴展了基帶信號頻譜,起到加密的效果。為了保證在任何情況下進入傳輸信道的數據碼流中“0”與“1”的概率都能基本相等,傳輸系統會用一個偽隨機序列對輸入的傳送碼流進行擾亂處理,將二進制數字信息做“隨機化”處理。

二、擾碼的原理

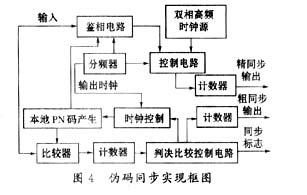

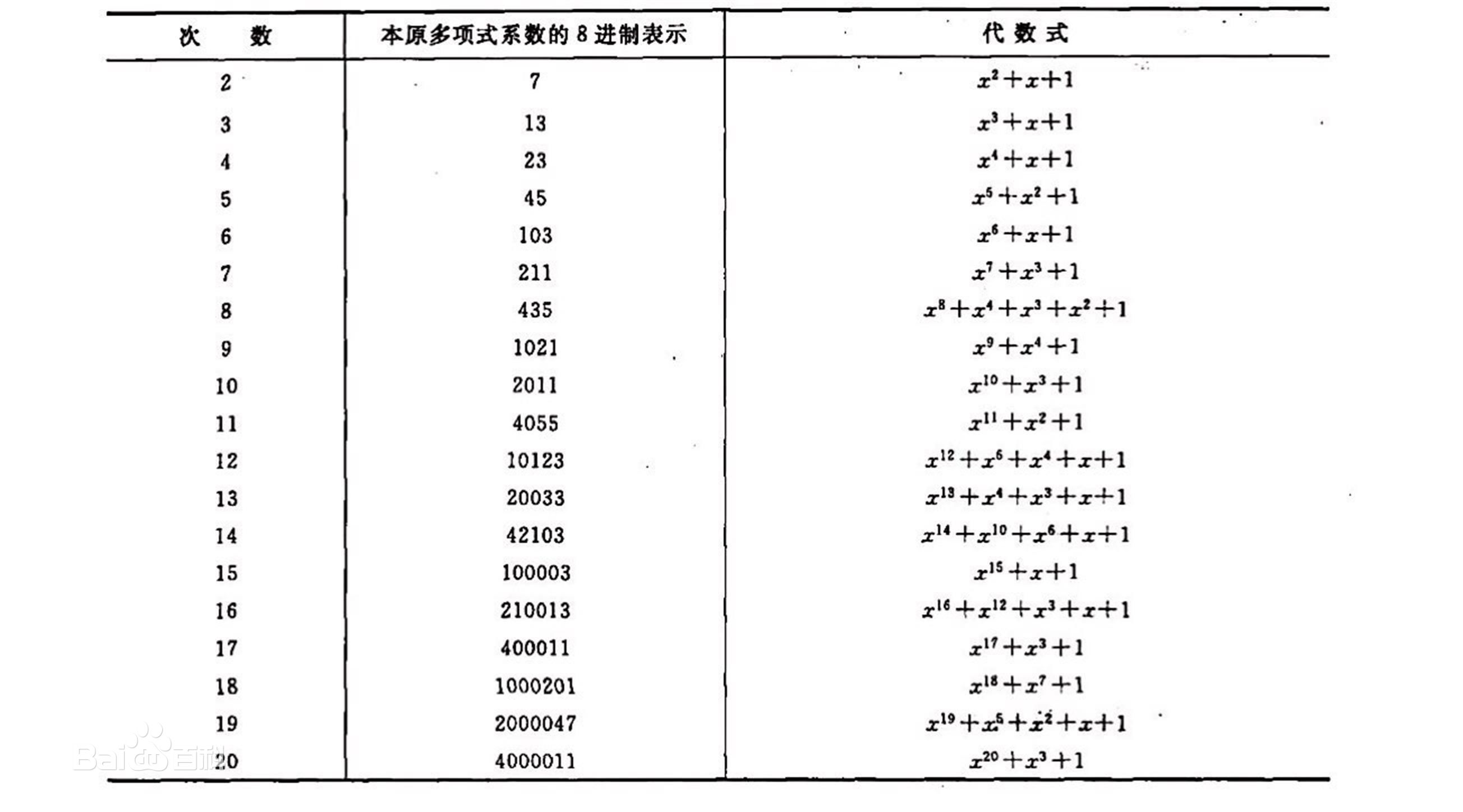

偽隨機序列是由一個標準的偽隨機序列發生器生成的,其中“0”與“1”出現的概率接近50%。用偽隨機序列對輸入的傳送碼流進行擾亂后,無論原始傳送碼流是何種分布,擾亂后的數據碼流中“0”與“1”的出現概率都接近50%。擾亂雖然改變了原始傳送碼流,但這種擾亂是有規律的,可以在接收端解除。將待發送的信息序列與發端產生的m序列進行模二加(擾碼),擾碼序列通過傳輸信道傳送到接收端,接收端接收到擾碼序列,使用同樣的m序列進行模二加,即可恢復原來的信息。

三、擾碼實現方法

1. 數學模型

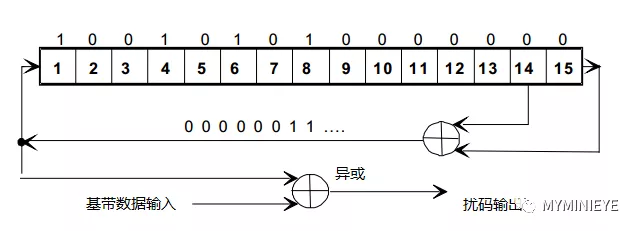

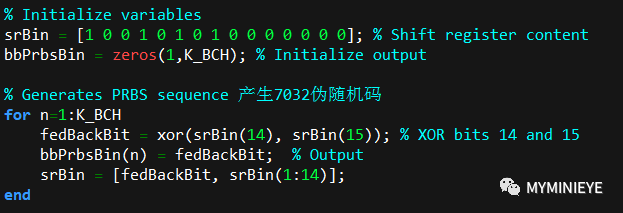

擾碼模塊對每個數據塊進行隨機化處理,隨機化序列和數據塊同步,每個數據塊都要重新初始化隨機序列,隨機化從數據塊的 MSB 位開始處理,K_BCH 位結束(K_BCH為定義的數據輸入長度)。擾碼序列的生成多項式為1+X14+X15,初始序列為100101010000000,擾碼實現結構如下:

3. FPGA實現

在FPGA內實現擾碼過程的,并不復雜,主要是信號的控制,這里使用AXI總線的結構,定義模塊的輸入輸出接口如下

|

名稱 |

方向 |

有效狀態 |

描述 |

|

clk |

in |

- |

時鐘,上升沿有效 |

|

rstn |

in |

low |

同步復位 |

|

s_data_tvalid |

in |

high |

輸入數據有效信號 |

|

s_data_tdata[0:0] |

in |

- |

數據輸入 |

|

s_data_tready |

out |

high |

準備接收數據使能 |

|

s_data_tlast |

in |

high |

表示輸入最后1bit數據 |

|

m_data_tvalid |

out |

high |

數據輸出有效信號 |

|

m_data_tdata[0:0] |

out |

- |

數據輸出 |

|

m_data_tready |

in |

high |

下一模塊接收準備使能 |

|

m_data_tlast |

out |

high |

表示輸出最后1bit數據 |

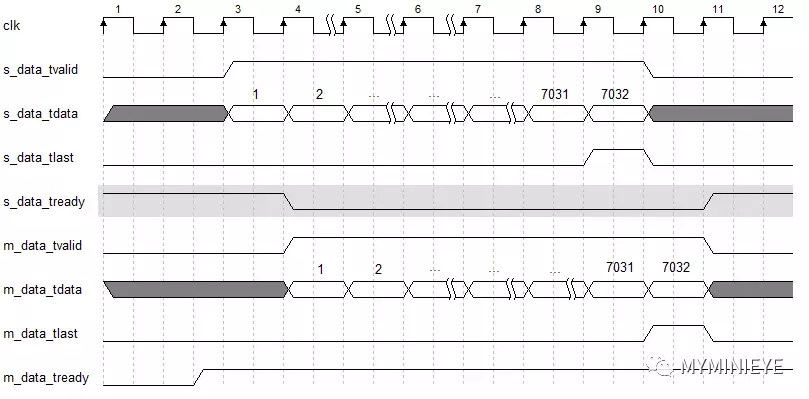

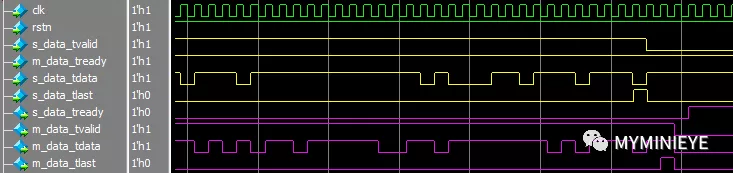

該模塊主要處理基于數據塊的操作,每個數據完成一次擾碼操作,并且每一幀的初始擾碼移位寄存器均要初始化。應滿足的時序如下

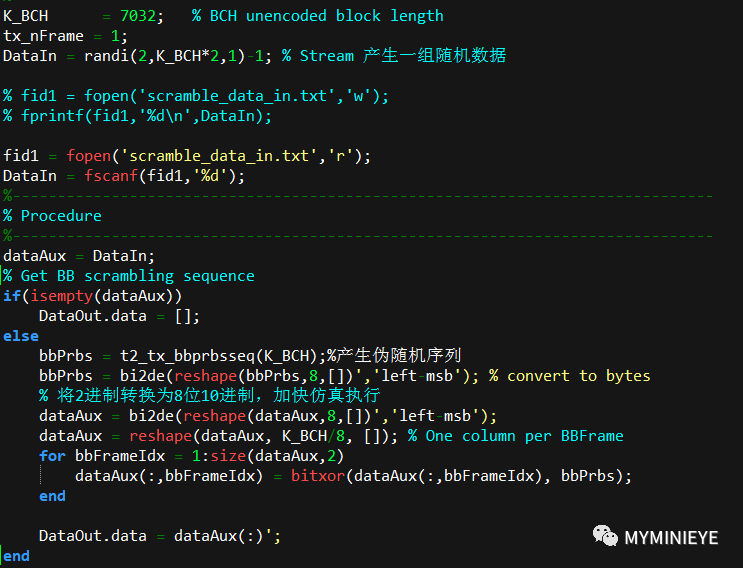

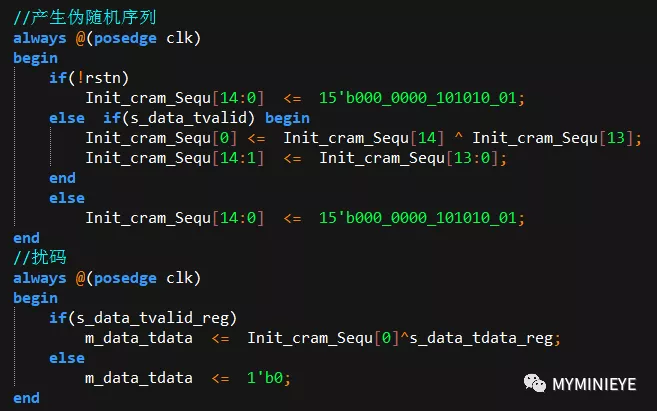

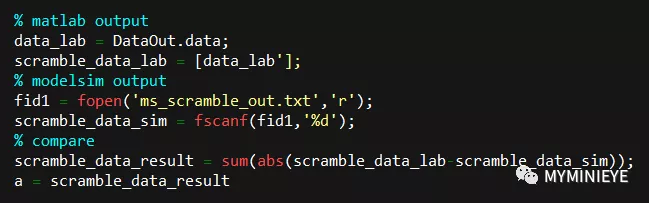

完成的功能為偽隨機序列的產生和數據擾碼兩個過程,如下

編輯:hfy

-

FPGA

+關注

關注

1644文章

21989瀏覽量

615219 -

無線通信

+關注

關注

58文章

4721瀏覽量

144937 -

數字信號

+關注

關注

2文章

994瀏覽量

48183 -

仿真波形圖

+關注

關注

1文章

5瀏覽量

3250

發布評論請先 登錄

擾碼器的并行化問題

通信中擾碼器與并行擾碼器設計

[Mill]FPGA無線通信課程連載——擾碼的原理及實現

基于FPGA的偽碼測距電路的設計與實現?

LS碼及其FPGA的實現

如何消除碼間串擾_怎么避免碼間串擾

擾碼器(一)擾碼器綜述及設計思路

擾碼器(二)串行擾碼器綜述及設計思路

如何在FPGA內實現擾碼過程

如何在FPGA內實現擾碼過程

評論