在FPGA中我們寫的最大的邏輯是什么?相信對大部分朋友來說應該是計數器,從最初板卡的測試時我們會閃爍LED,到復雜的AXI總線中產生地址或者last等信號,都會用到計數器,使用計數器那必然會用到進位鏈。

可能很多剛開始接觸FPGA的同學沒聽過進位鏈,也就是Carry Chain,我們這里再回顧一下。FPGA的三個主要資源為:

1. 最低邏輯單元

可配置邏輯單元(CLB)

存儲單元

運算單元(DSP48)

2. 一流的I / O資源

3. 布線資源

其中,CLB在FPGA中最豐富,在7系列的FPGA中,一個CLB中有兩個Slice,Slice中包含4個LUT6、3個數據選擇器MUX,兩個獨立進位鏈(Carry4,Ultrascale是CARRY8)和8個主軸。

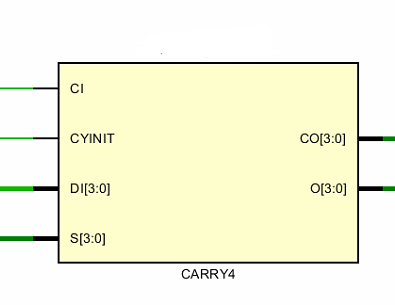

首先,我們來看下Carry Chain的結構原理,其輸入輸出接口如下:

其中,

CI是上一個CARRY4的進位輸出,位寬為1;

CYINT是進位的初始化值,位寬為1;

DI是數據的輸入(兩個加數的任意一個),位寬為4;

SI是兩個加數的異或,位寬為4;

O是加法結果輸出,位寬為4;

CO是進位輸出,位寬為4;(為什么進位輸出是4bit?后面有解釋)

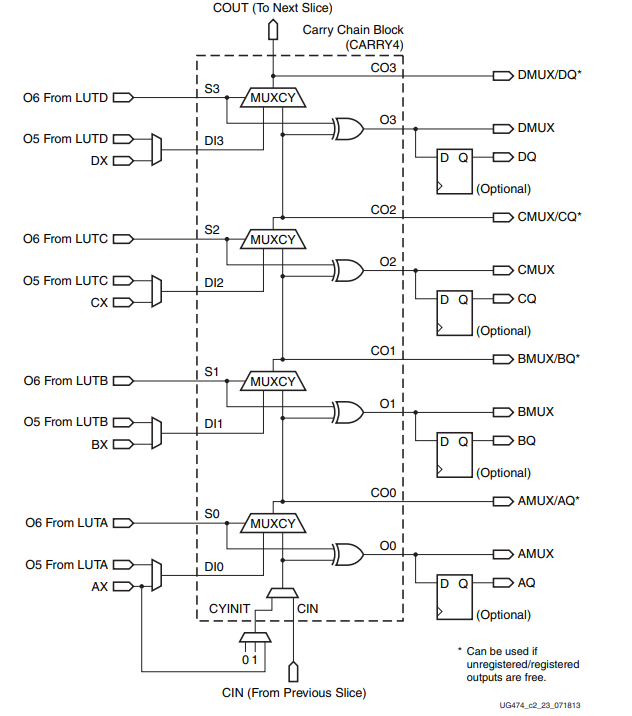

Carry4的內部結構如下圖所示:

這里我們要先解釋一下FPGA中利用卡里鏈(Carry Chain)實現加法的原理,比如兩個加數分別為a = 4'b1000和b=4'b1100,其結果應該是8+12=20。

a = 4'b1000; b = 4'b1100; S = a ^ b = 4'b0100; D = b = 4'b1100; //D取a也可以 CIN = 0; //沒有上一級的進位輸入 CYINIT = 0; //初始值為0 // 下面為CARRY4的計算過程,具體的算法跟上圖中過程一樣 S0 = 0; //S的第0位 O0 = S0 ^ 0 = 0 ^ 0 = 0; CO0 = DI0 = 0; //上圖中的MUXCY,S0為0時,選擇1,也就是DI0,S0為1是選擇2 S1 = 0; O1 = S1 ^ CO0 = 0 ^ 0 = 0; CO1 = DI1 = 0; S2 = 1; O2 = S2 ^ CO1 = 0 ^ 1 = 1; CO2 = CO1 = 0; S3 = 0; O3 = S3 ^ CO2 = 0 ^ 0 = 0; CO3 = DI3 = 1;

加法最終的輸出結果為:{CO3,O3,O2,O1,O0} = 5'b10100 =20。進位輸出在CARRY4的內部也使用到了,因此有4個位的進位輸出CO,但輸出給下一級的只是CO [3]。

再來看完下面的例子就更清晰了。Example的代碼如下:

module top(

input clk,

input [7:0] din_a,

input [7:0] din_b,

output reg[7:0] dout

);

always @ ( posedge clk )

begin

dout <= din_a + din_b;

end

endmodule

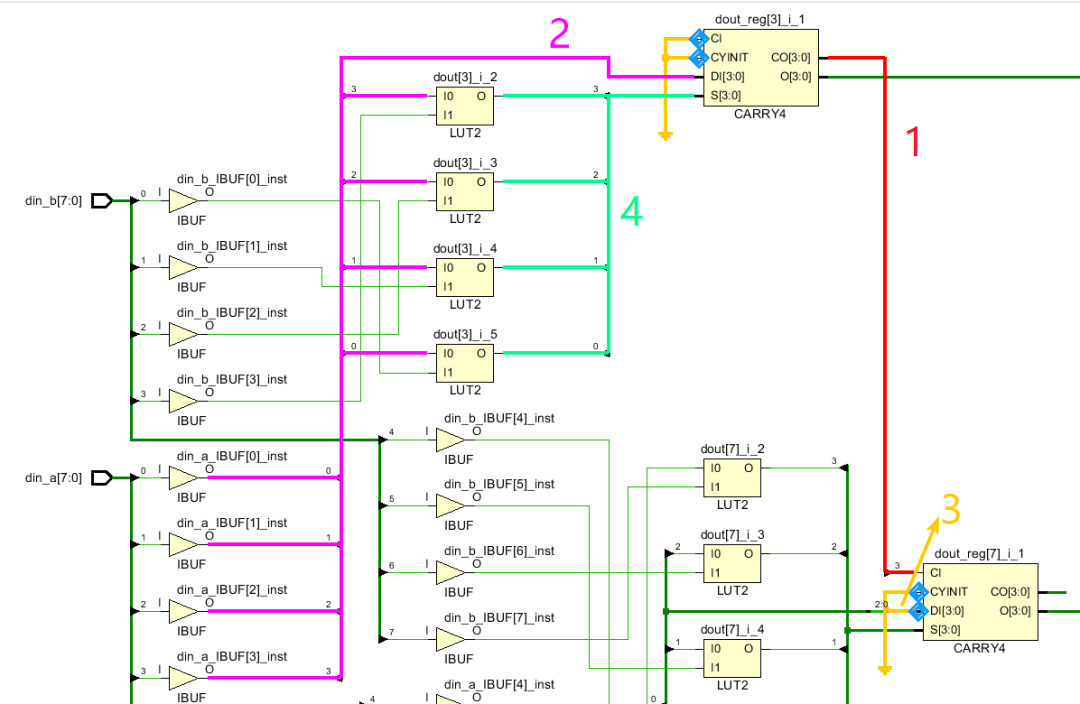

綜合之后的電路如下:

在本程序中,加數為din_a和din_b,圖中

1 表示CARRY4的進位輸出到下一級的進入輸入;

2 表示輸入的一個加數din_a(換成din_b也是可以的);

3 表示第二級輸入的DI端口,因為第二級CARRY是通過第一級的進位輸出進行累加,因此該接口為0;

4 表示輸入兩個加數的異或結果。

可以拋光,當進行兩個兩個bit的數據進行加法操作時,會使用兩個CARRY4級聯,那如果是對48位的數據進行相加,那就會用到12個的CARRY4的級聯,這樣(此處需要注意的是,在Vivado的設置下,如果進行的是12bit以下的數據加1'b1的操作,那么Vivado綜合的結果并不會使用CARYY4,或者使用LUT來實現加法器)。

那如何解決這種問題呢?我們可以把加法操作進行拆解,比如拆解成3個16bit的計數器,那這樣就會只有4個CARRY4的級聯,時序情況就好了很多。

對比程序如下:

module top(

input clk,

input [47:0] din1,

input [47:0] din2,

output reg[47:0] dout1,

output [47:0] dout2

);

always @ ( posedge clk )

begin

dout1 <= din1 + 1'b1;

end

genvar i;

generate

for(i = 0;i < 3;i=i+1) begin:LOOP

wire carry_co;

reg [15:0] carry_o=0;

wire ci;

if(i==0) begin

always @ ( posedge clk )

begin

carry_o <= din2[i*16+:16] + 1'b1;

end

end //if

else begin

always @ (posedge clk) begin

if(LOOP[i-1].carry_co == 1)

carry_o <= carry_o + 1'b1;

end

end //else

assign LOOP[i].carry_co = (LOOP[i].carry_o==16'hffff)?1'b1:1'b0;

assign dout2[i*16+:16] = LOOP[i].carry_o;

end //for

endgenerate

endmodule

:綜合后的schematic后可以發現,在dout2的輸出中,每4個CARRY4后都會有一級的觸發,這樣時序就會好很多,但造成的代價是LUT會增加。

編輯:hfy

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618480 -

計數器

+關注

關注

32文章

2291瀏覽量

96418

發布評論請先 登錄

聚徽深度解析國內工控平板電腦的工業級抗干擾技術如何實現?

GPU架構深度解析

解鎖未來汽車電子技術:軟件定義車輛與區域架構深度解析

FPGA時序約束之設置時鐘組

風華電容命名方法深度解析

FPGA加速深度學習模型的案例

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

深度解析FPGA時序的進位鏈

深度解析FPGA時序的進位鏈

評論