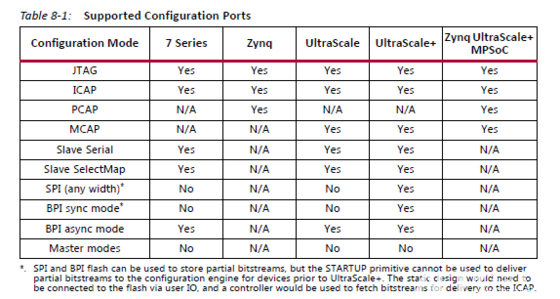

本博文主要是對基于PCIE(mcap)的部分可重構實現的步驟做一個簡單的演示,如有錯誤之處,歡迎批評指正。值得說明的是,基于PCIE的部分可重構需在ultrascale系列及ultrascale+芯片才能實現,具體哪些系列能實現哪種配置方式如下圖所示:

圖1

本質上來說,無論是JTAG還是ICAP或者MCAP以及其它FPGA的配置方式,目的都是配置FPGA的邏輯。MCAP是通過PCIE來實現對FPGA的燒寫,最終結果和使用JTAG進行FPGA燒寫沒有區別,而使用PCIE對FPGA燒寫有更好的靈活性,在某些需求場合是必不可缺的,譬如在數據加速的部署,FPGA加速板卡是位于服務器端,在服務上線之后修改FPGA業務邏輯的話如果使用JTAG燒寫,一方面操作十分不便,可行性極低,另一方面,重新燒寫FPGA會導致原FPGA的PCIE設備從服務器中刪除,需要重新啟動服務器枚舉設備(目前本人沒有找到可以進入系統后重新枚舉設備的方法),對于已經上線的服務器,在每次切換FPGA業務邏輯后重啟服務器是無法接受的,因此,使用PCIE對FPGA的部分重配置就十分必要,部分重配置能夠在保持FPGA靜態邏輯(PCIE部分和其他非業務邏輯)正常工作的情況下動態修改某個區域的邏輯(業務邏輯)。使用這種技術能夠不重啟服務器情況下快速切換業務邏輯。

本文的實現基于Xilinx的VCU1525加速板卡實現,VCU1525的FPGA是一顆ultrascale+的VU9P,由上圖可以知道UltraScale+系列的FPGA支持MCAP配置模式。下面由一個簡單的例程實現MCAP部分重配置。

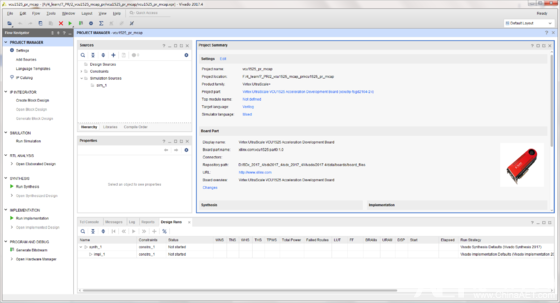

1.新建一個空白工程。

圖2

2.因為使用MCAP的配置方式,而MCAP集成于PCIE硬核中,因此需要例化一個PCIE相關的IP,這里使用XDMA進行本次例程(裸PCIE硬核也可以),該例程沒有XDMA進行數據DMA搬運的相關內容,僅僅是借用XDMA中的MCAP功能,本人目前也有一個比較痛苦的地方,就是XDMA的上位機驅動怎么和MCAP的驅動整合在一起,不懂上位機驅動開發表示很迷茫,有大佬懂這個可以探討下。

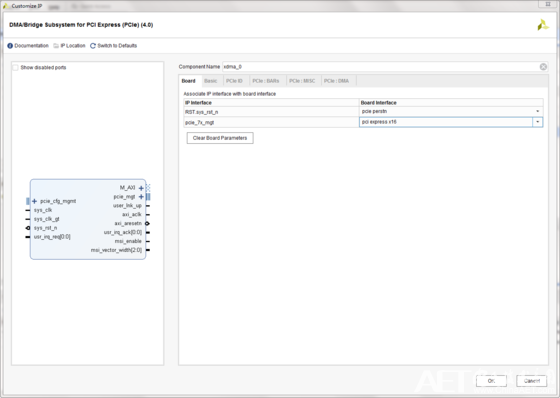

3.在Board選項中(在建立工程時選擇Xilinx官方板卡才有這個選項)選擇如下。

圖3

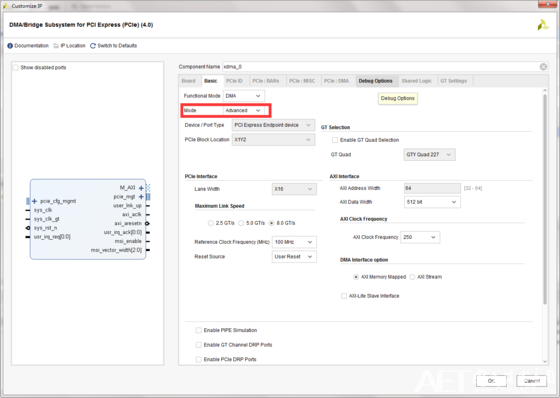

4.在Basic選項中,把圖中紅色框中的Mode設置成Advanced。

圖4

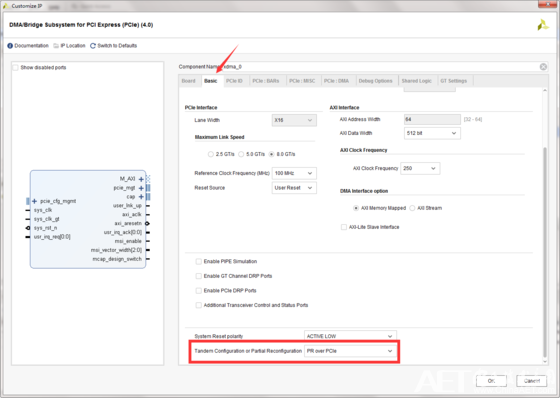

5.在Basic選項中,在最底部的Tandem Configuration or Partial Reconfiguration中選擇PR over PCIE。

圖5

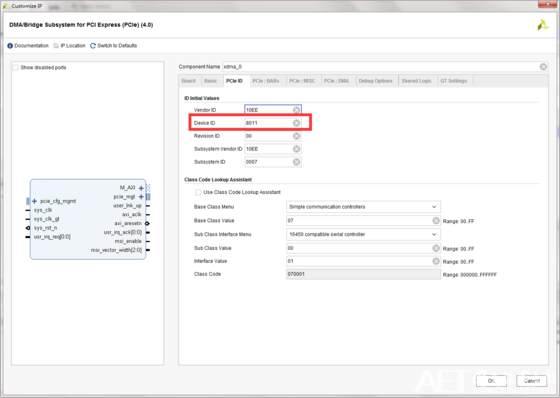

6.在Pcie ID選項的Device ID中設置成8011(因為Xilinx提供的驅動支持8011,8038,506F)

圖6

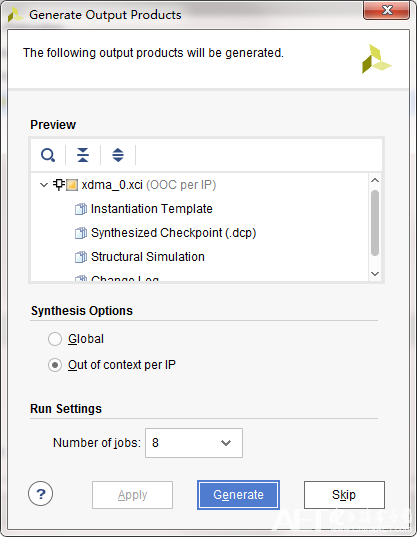

7.其它按照默認選項,生成該IP。

圖7

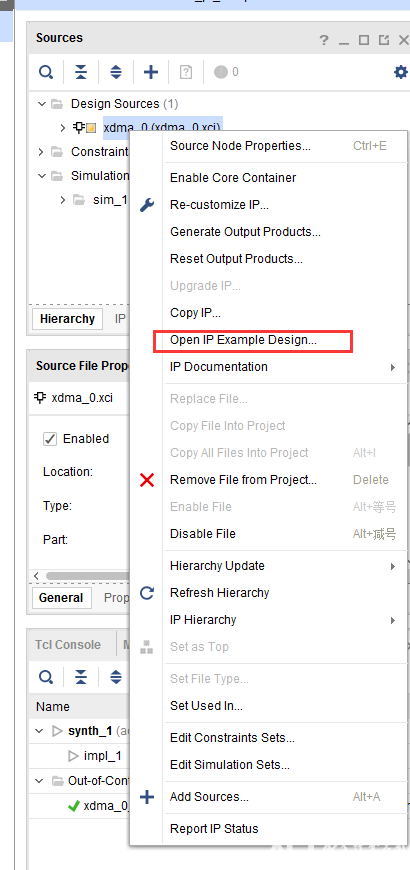

8.考慮到測試和實現的方便,使用XDMA的Example Design來修改例程,在XDMA綜合完成之后(記得選擇OOC),打開該IP的Example Design,在該工程上面做修改。

圖8

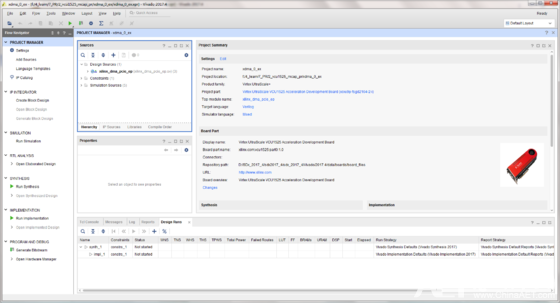

9.Example Design如下圖。

圖9

10.首先我們先修改XDC文件和工程頂層,主要是LED的管腳和電平約束。在這個例子中,我們將要實現使用兩個可重構模塊,一個模塊用于控制VCU1525的LED燈亮,一個模塊用于控制VCU1525的LED燈滅,用這個簡單的例子來說明PR的實現步驟。

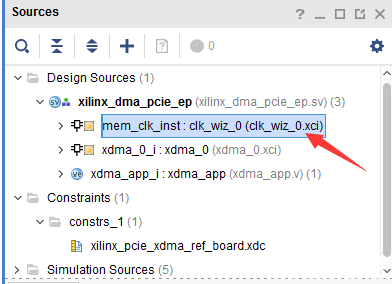

11.修改工程中的時鐘生成IP,此步驟不是必要,主要是指定輸入時鐘管腳,如果不是官方板子,在XDC里面約束即可。

圖10

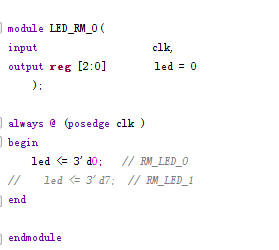

12.新建兩個模塊,分別是LED_RM_0和LED_RM_1。其中LED_RM_0用于控制LED滅,LED_RM_1用于控制LED亮。兩個模塊的邏輯很簡單,只是做演示作用。代碼邏輯如下。

圖11

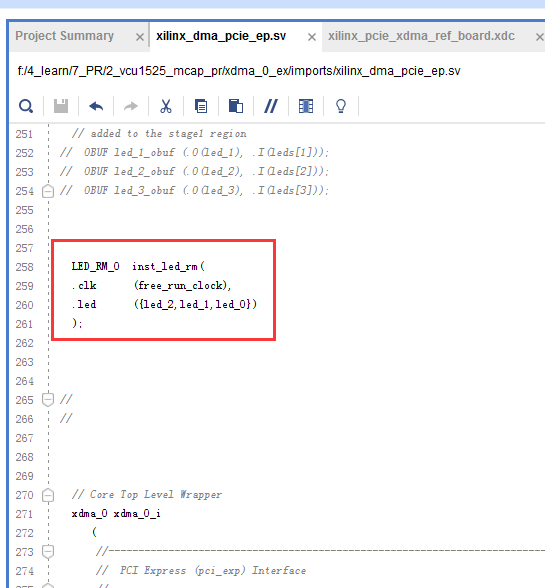

13.在工程頂層例化其中一個RM模塊。

圖12

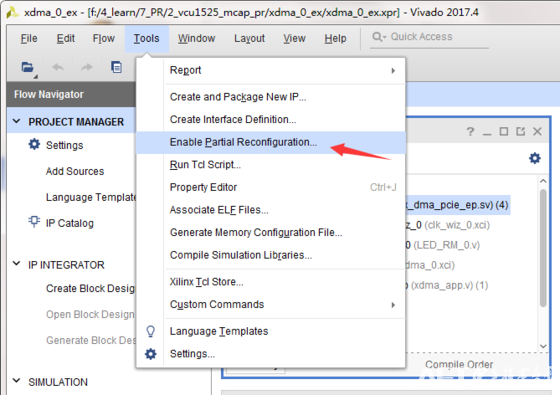

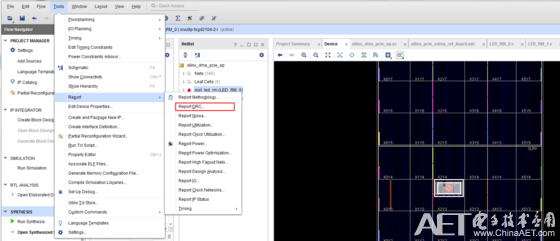

14.完成上述步驟之后,選擇Tools->Enable Partial Reconfiguration...選項,將工程轉換成支持PR類型的工程,在后續彈出的方框中選擇Convert。

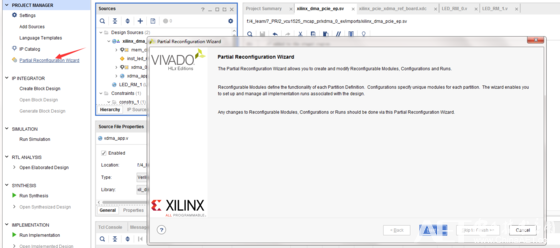

圖13

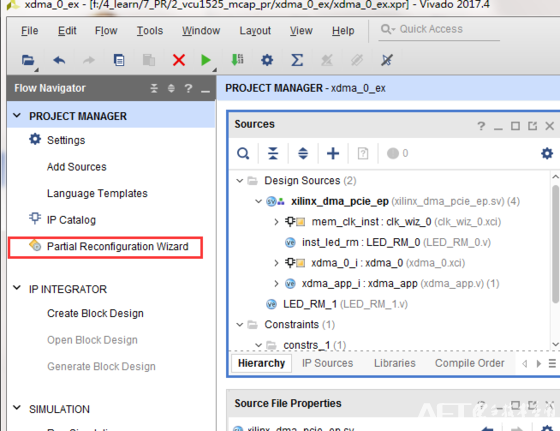

15.此時工程已經轉換完成,對比轉換之前,在Flow Navigator的PROJECT MANAGER會多出Partial Reconfiguration Wizard選項。

圖14

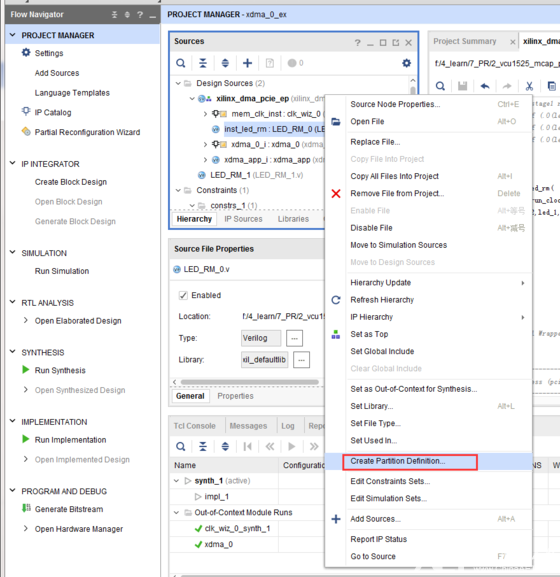

16.設置我們要進行部分重構的邏輯,即LED_RM_x模塊,如下圖所示,右鍵LED_RM_0,選擇Create Partition Definition...

圖15

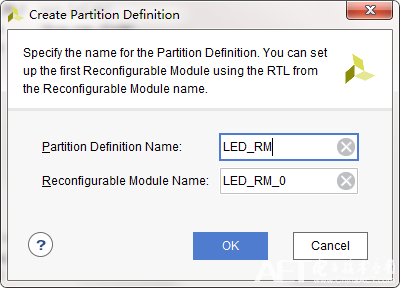

17.在彈出的窗口中指定一個分區的名字,這里設置為LED_RM,點擊OK。

圖16

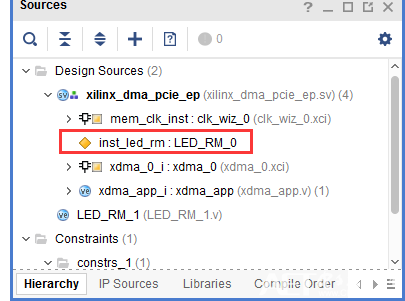

18.完成上一步之后,LED_RM_0模塊變成了一個黃色的棱形標志,如下圖所示。

圖17

19.打開Partial Reconfiguration wizard

圖18

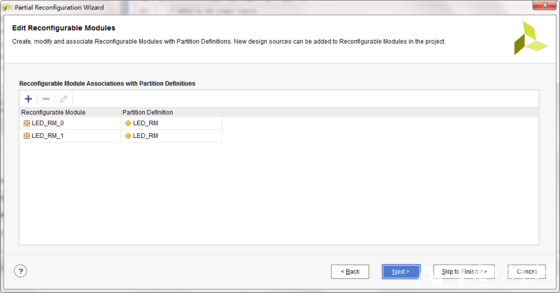

20.在Edit Reconfiguration Modules界面中,點擊“+”符號,把LED_RM_1添加進來,表明有兩個重配置模塊,添加完成后如下圖所示,屬于LED_RM分區定義列表里面有LED_RM_0和LED_RM_1兩個重配置模塊。

圖19

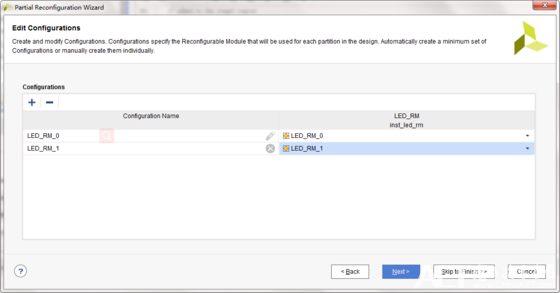

21.在Editing Configurations界面中,選擇automatically create configurations,并修改Configuration Name,如下圖所示。

圖20

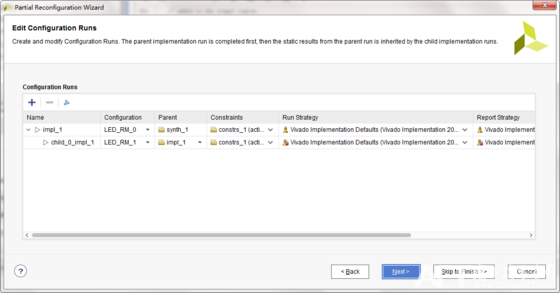

22.在Edit Configuration Runs界面中,選擇automatically create configurations。

圖21

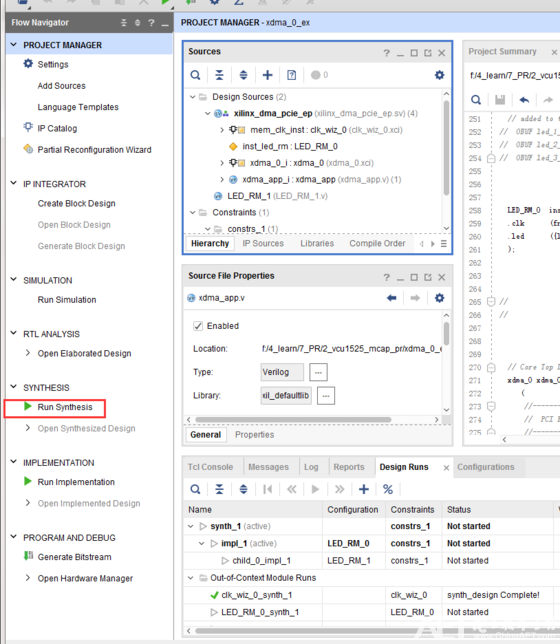

23.最后,點擊Finish,部分重配置的向導設置完成,然后點擊Run Synthesis綜合設計。

圖22

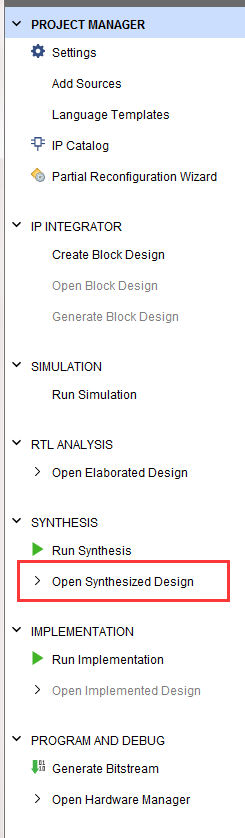

24.綜合完成之后打開綜合設計。

圖23

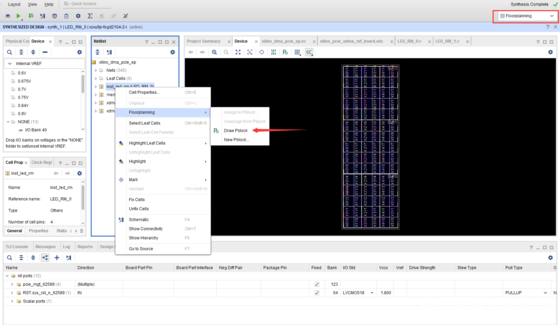

25.在Floorplanning界面,右鍵LED_RM_0,選擇Floorplanning->Draw Pblock,給RM模塊劃分重配置的區域。

圖24

26.在分配完重配置區域之后,保存相應的約束到xdc文件中,然后做DRC檢查,檢查分配的區域是否符合要求。

圖25

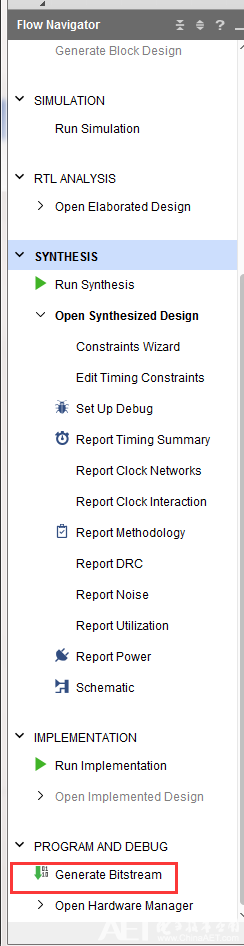

27.DRC檢查沒有問題之后,點擊Generate Bitstream.

圖26

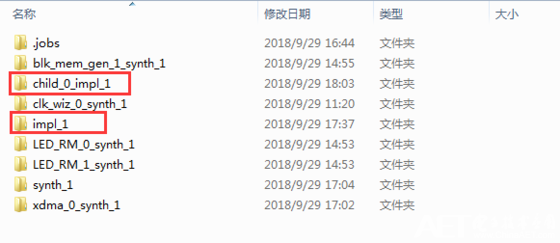

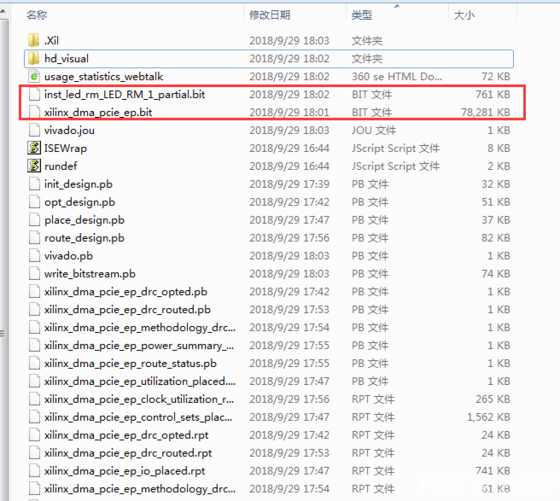

28.至此,部分重配置的工程就生成完畢,在生成出來的文件里面,在工程目錄下會有兩個imp的文件夾,里面會分別有靜態邏輯和各自的重配置邏輯,我們將靜態邏輯先燒寫進去FPGA,之后就可以通過PCIE配置動態邏輯,關于MCAP的驅動的上位機,在Xilinx_Answer_64761__UltraScale_Devices這份文檔中有詳細的說明。

圖27

圖28

編輯:hfy

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615302 -

Xilinx

+關注

關注

73文章

2184瀏覽量

124582 -

JTAG

+關注

關注

6文章

403瀏覽量

73033 -

PCIe

+關注

關注

16文章

1329瀏覽量

84827

發布評論請先 登錄

清微智能官宣:國產可重構芯片全球出貨量突破2000萬顆

中科億海微可重構智能超表面電磁單元控制方案:多維調控電磁波,助力6G無線中繼

nvme IP開發之PCIe上

PCIe信號完整性問題解決方案

PCIe延遲對系統性能的影響

基于相變材料的可重構超構表面用于圖像處理

Cadence展示完整的PCIe 7.0 IP解決方案

PCIe 5.0 SerDes 測試

實測952Mbps!四路千兆網PCIe拓展方案,國產工業級!

新思科技PCIe 7.0驗證IP(VIP)的特性

基于PCIE(mcap)的部分可重構實現方案

基于PCIE(mcap)的部分可重構實現方案

評論