大家好,又到了每日學(xué)習(xí)的時候了。自1985年問世以來,FPGA這種可編程邏輯器件憑借在性能、上市時間、成本、穩(wěn)定性和長期維護方面的優(yōu)勢,在通信、醫(yī)療、工控和安防等領(lǐng)域占有一席之地。特別是近兩年,隨著云計算、高性能計算和人工智能的繁榮,擁有先天優(yōu)勢的FPGA更是得到了前所未有的關(guān)注。近幾年隨著國家開始大力發(fā)展實業(yè),國內(nèi)集成電路行業(yè)發(fā)展越來越好,隨之由于用戶對性能的要求越來越高,F(xiàn)PGA的可編程、高速度、低功耗、較低的二次開發(fā)成本的優(yōu)越特性,帶動了FPGA行業(yè)的發(fā)展,有很多同學(xué)們開始自學(xué)FPGA。

首先,先來了解一下FPGA,F(xiàn)PGA:Field-Programmable Gate Array,中文名字:現(xiàn)場可編程門陣列。FPGA由六部分組成:可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核。英特爾首席執(zhí)行官科再奇曾這樣描述:“你可以把FPGA想象成一堆gate,能夠隨時編程。FPGA可以用作多個領(lǐng)域的加速器,例如在加密的同時進行面部搜索,并能在微秒內(nèi)重新編程。其成本遠低于大規(guī)模單個定制部件,并具有更高的靈活性。”

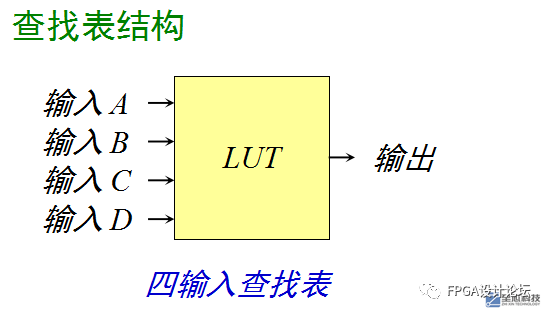

FPGA是可編程器件,與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,具有不同的結(jié)構(gòu),F(xiàn)PGA利用小型查找表(16×1RAM)來實現(xiàn)組合邏輯,每個查找表連接到一個D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動其他邏輯電路或驅(qū)動I/O,由此構(gòu)成了既可實現(xiàn)組合邏輯功能又可實現(xiàn)時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內(nèi)部靜態(tài)存儲單元加載編程數(shù)據(jù)來實現(xiàn)的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實現(xiàn)的功能,F(xiàn)PGA允許無限次的編程。

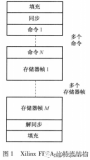

下圖為四輸入查找表結(jié)構(gòu)。

下圖為FPGA的結(jié)構(gòu)

關(guān)于FPGA概念以及結(jié)構(gòu)等等的介紹就到這里,如果大家還想要詳細了解,可以自己去查閱資料。接下來,咱們就來聊聊初學(xué)FPGA時需要注意哪些知識點或者小細節(jié),希望對大家的學(xué)習(xí)有所幫助。 區(qū)別一下軟硬件幾種類型

通用應(yīng)用軟件

a. 軟件匯編語言(Assembly Language)是面向機器的程序設(shè)計語言。

b. 主要關(guān)心邏輯和抽象,關(guān)心代碼量大了之后復(fù)雜度可控。硬件資源較多,硬件性能差別較大,不需要針對特定資源設(shè)計。

c. 邏輯分層較多,來源于抽象的性能損耗可以接受。甚至于現(xiàn)在很多主流語言構(gòu)建在虛擬機和解釋器上。

d. 非實時。

e. 不需要了解底層硬件原理。

嵌入式軟件(面向硬件編程)

a. 時序可控。大部分場景要求實時,因為要滿足硬件時序。非搶占的任務(wù)調(diào)度和中斷隊列都會引入定時的偏差。

b. 資源開銷可控。因為嵌入式硬件環(huán)境大多只有有限的 RAM 和 Flash 資源。

c. 針對特定硬件環(huán)境設(shè)計。

d. 所有代碼上的抽象和優(yōu)化都必須是零損耗或者損耗可控(可以參考 rust 語言)。比較典型的是 GC 會引入嚴(yán)重的時序和資源不可控,所以系統(tǒng)語言很少使用。

數(shù)字邏輯電路設(shè)計(硬件描述性語言)

a. 數(shù)字電路設(shè)計不是編程,是設(shè)計的時候先有電路,再用語言描述出來。

b. 時序要求更嚴(yán),需要考慮建立時間和保持時間,及隨之而來的亞穩(wěn)態(tài)。

c. Coding style 會明顯的影響電路性能。邏輯都一樣,但是 DFF 的位置不一樣,就可能導(dǎo)致時序不滿足。

d. 并行化。執(zhí)行順序不再是 CPU 的順序執(zhí)行,而是多個并行的流水線。比如快速傅立葉 FFT。比如路由器的 CAM,單次動作完成整表查表。

1. FPGA學(xué)習(xí)時使用的 VHDL 和 verilog HDL 不是編程語言,而是一種可綜合的硬件描述語言,我們在描述的時候一定要明白所要設(shè)計的是一個怎樣的電路。

2. 當(dāng)今社會做開發(fā)用的 Verilog HDL 語言偏多,Verilog HDL 支持兩種進程 initial 和 always 進程,前者只能用在TB(TestBench)中,后者才是可綜合的。

3. 阻塞與非阻塞指都是相對于進程本身而言的,簡單來講,阻塞用在描述組合邏輯電路,而非阻塞用于時序邏輯電路。

4. 使用進程模塊的電路類型:

組合電路-----對組合邏輯中使用的所有輸入敏感

例子:

always@(a or b or c)

時序電路-----僅對時鐘和控制信號敏感

例子:

always @(posedge clk or negedge rst_n)

always既可以描述組合邏輯,也可以描述時序邏輯。

5. 可以用case語句完成多路選擇器的功能,但是列舉的情況一定要考慮全,否則會產(chǎn)生Latch。

6. verilog中有兩類子程序:

函數(shù)和任務(wù)

函數(shù)-----根據(jù)輸入返回一個值

-----產(chǎn)生組合邏輯

-----用在表達式中:assign mult_out=mult(ina,inb);

-----函數(shù)是組合邏輯,不能含有任何延時,事件,或者時序控制聲明,至少有一個輸入變量

總是返回一個變量

-----可以調(diào)用函數(shù),但是不能調(diào)用任務(wù)。

任務(wù)-----可以是組合或者寄存器

-----以聲明的形式調(diào)用任務(wù):stm_out(nxt,first,sel,filter);

-----與其他編程語言中的任務(wù)相似

-----與函數(shù)不同任務(wù)不需要傳遞參數(shù),而函數(shù)要傳遞參數(shù)

-----可以調(diào)用任務(wù)和函數(shù)。

----- 可以含有任何延時,事件,或者時序控制聲明

-----返回零個或者多個數(shù)值

可綜合的verilog語法子集是指用硬件可以實現(xiàn)的語法。力求用最簡單的語言實現(xiàn)最復(fù)雜的硬件電路。

7. 硬件都有相應(yīng)的輸入輸出的接口,或者是輸入或者是輸出,或者是輸入輸出。

8. reg 型是指時序邏輯里面的一個寄存數(shù)據(jù)(寄存機類型),wire 是組合邏輯里面的一條連線(線型)。

9. define 定義了一個參數(shù),在整個工程里面都是有效地使用。parameter 定義的一個參數(shù)只在當(dāng)前文件里面進行使用。

10. 各種邏輯操作符,移位操作符,算術(shù)操作符大多是可綜合的。

11. assign一般是只針對于組合邏輯,而always語句既可以用于組合邏輯又可以用于時序邏輯,always模塊的敏感表,如果是電平,則為組合邏輯,如果是沿信號posedge或者negedge 則為時序邏輯。

12. begin----end和C語言里面的{}是類似的。

13. for 語句-----循環(huán)因為綜合出來的結(jié)果可能比較浪費資源,所以就一般用的比較少,但是在一些特定的設(shè)計中可以起到事半功倍的效果。

14. Total logic element 總共消耗的邏輯單元。

15. 行為級仿真可以理解為功能仿真(前仿真);布局布線后仿真可以理解為時序仿真(后仿真)。

16. 時序邏輯中時鐘和復(fù)位信號是必須的。

17. 注意wire賦值的一個問題如下:

wire[2:0] key_an=key_rst_r&(~key_rst)

其相當(dāng)于如下的一個賦值語句

wire[2:0] key_an;

assign key_an=key_rst_r&(~key_rst);

其實現(xiàn)的效果是一樣的。

此種方法為:脈沖邊沿檢測法。

18. 實際工作中,除了描述仿真測試激勵(Testbench)時使用for循環(huán)語句外,極少在RTL級編碼中使用for循環(huán),這是因為for循環(huán)會被綜合器展開為所有變量情況的執(zhí)行語句,每個變量獨立占用寄存器資源,不能有效的復(fù)用硬件邏輯資源,造成巨大的浪費。一般常用case語句代替。

19. FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富。

20. FPGA使用的兩種語言:VHDL 和 verilog HDL 。

VHDL 為美國國防部發(fā)明,用于較多的設(shè)計人員合作完成的特大型項目(一百萬門以上),語法/結(jié)構(gòu)比較嚴(yán)謹(jǐn),因為編寫出的模塊風(fēng)格清晰。

verilog HDL 第三方支持工具較多,語法結(jié)構(gòu)比VHDL簡單,學(xué)習(xí)來比較容易,仿真工具比較好用,測試激勵模塊容易編寫。

21. 時序設(shè)計的實質(zhì):電路設(shè)計的難點在于時序設(shè)計,實質(zhì)就是滿足么一個觸發(fā)器 建立時間/保持時間 的要求。

(備注:建立時間:觸發(fā)器在時鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時間;保持時間:觸發(fā)器在時鐘上升沿到來之后,觸發(fā)器在時鐘上升沿到來之前,其數(shù)據(jù)輸入端的數(shù)據(jù)必須保持不變的最小時間。)

22. 為什么觸發(fā)器要滿足建立時間和保持時間?

因為觸發(fā)器內(nèi)部數(shù)據(jù)的形成是需要一定的時間的,如果不滿足建立和保持時間,觸發(fā)器將進入亞穩(wěn)態(tài),進入亞穩(wěn)態(tài)后觸發(fā)器的輸出將不穩(wěn)定,在0和1之間變化,這時需要經(jīng)過一個恢復(fù)時間,其輸出才能 穩(wěn)定,但穩(wěn)定后的值并不一定是你的輸入值。這就是為什么要用兩級觸發(fā)器來同步異步輸入信號。這樣做可以防止由于異步輸入信號對于本級時鐘可能不滿足建立保持時間而使本級觸發(fā)器產(chǎn)生的亞穩(wěn)態(tài)傳播到后面邏輯中,導(dǎo)致亞穩(wěn)態(tài)的傳播。

23. 鎖存器(latch)和觸發(fā)器(flip-flop)區(qū)別?

電平敏感的存儲器件稱為鎖存器。可分為高電平鎖存器和低電平鎖存器,用于不同時鐘之間的信號同步。

有交叉耦合的門構(gòu)成的雙穩(wěn)態(tài)的存儲原件稱為觸發(fā)器。分為上升沿觸發(fā)和下降沿觸發(fā)。可以認為是兩個不同電平敏感的鎖存器串連而成。前一個鎖存器決定了觸發(fā)器的建立時間,后一個鎖存器則決定了保持時間。

24. and so on.

最后,我們來簡單聊一聊FPGA的應(yīng)用范圍。FPAG的應(yīng)用越來越廣泛,航天航空、汽車駕駛、醫(yī)療、廣播、測量測試、消費電子、工業(yè)控制、計算機設(shè)備、武器裝備等等。從應(yīng)用場景角度分析,我們可以看到隨著谷歌的阿爾法狗打敗了人類圍棋冠軍后,深度學(xué)習(xí)已經(jīng)從神壇走下來,越來越多的人開始認識到深度學(xué)習(xí)可能會改變未來的生活,成為未來科技發(fā)展的方向;而FPGA設(shè)計工具使其對深度學(xué)習(xí)領(lǐng)域經(jīng)常使用的上層軟件兼容性更強,F(xiàn)PGA正是助力深度學(xué)習(xí)的一大技術(shù)。不同于CPU的是,F(xiàn)PGA和GPU內(nèi)都有大量的計算單元,因此它們的計算能力都很強。在進行神經(jīng)網(wǎng)絡(luò)運算的時候,兩者的速度會比CPU快很多。但是GPU由于架構(gòu)固定硬件原生支持的指令固定了,而FPGA則是可編程的。

隨著國家綜合實力越來越強大,國民經(jīng)濟越來越好,F(xiàn)PGA從之前的運用廣泛的軍工行業(yè)在慢慢延伸到民用行業(yè),并且會越來越廣泛。

原文標(biāo)題:FPGA學(xué)習(xí)需要注意的知識點

文章出處:【微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1643文章

21968瀏覽量

614311

原文標(biāo)題:FPGA學(xué)習(xí)需要注意的知識點

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文帶你了解工業(yè)計算機尺寸

帶你一文了解芯片開封技術(shù)

一文帶你了解arm主板

一文帶你了解FIB技術(shù)

一文帶你了解什么是SD NAND存儲芯片

一文帶你了解透過率測量

一文帶你了解IP地址別名

一文帶你了解IP版本

一文帶你了解半導(dǎo)體公司的各個崗位

一文了解FPGA比特流的內(nèi)部結(jié)構(gòu)

科普 | 一文了解FPGA

一文帶你了解什么是工控機?

一文了解FPGA技術(shù)知識

一文帶你詳細了解工業(yè)電腦

一文帶你了解FPGA

一文帶你了解FPGA

評論