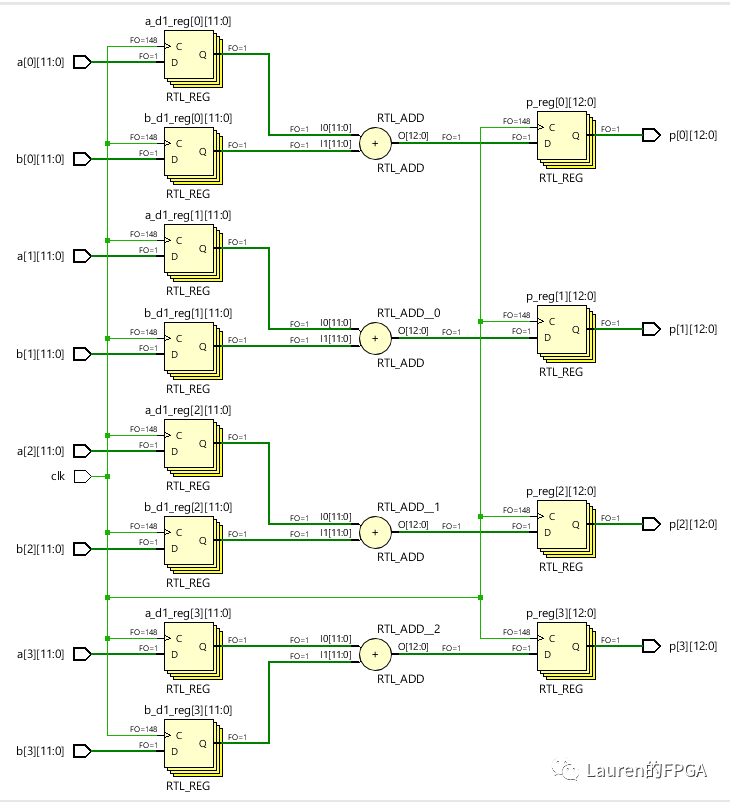

這里并行加法是指多個(gè)加法操作同時(shí)執(zhí)行,這意味著需要消耗多個(gè)加法器。這里我們以4個(gè)12-bit數(shù)相加(加數(shù)和被加數(shù)均為12-bit,故和為13-bit,從而避免了溢出問(wèn)題)。相應(yīng)的電路圖如下圖所示。圖中的RTL_ADD即為加法器,同時(shí)此電路對(duì)輸入和輸出數(shù)據(jù)均添加了流水寄存器。

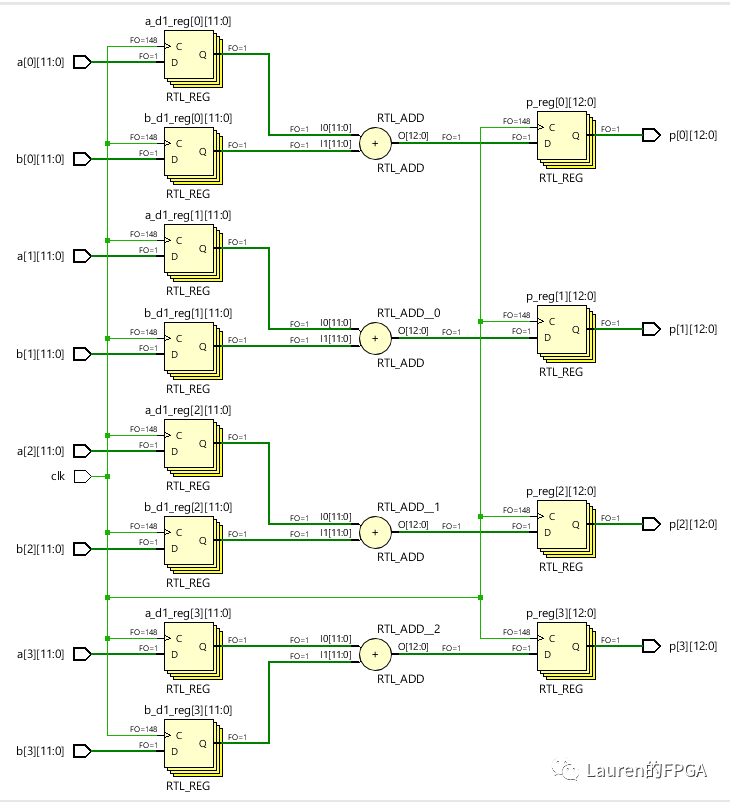

此電路對(duì)應(yīng)的RTL代碼如下圖所示,這里我們使用了SystemVerilog來(lái)描述。輸入a和b均為4個(gè)12-bit數(shù)據(jù)構(gòu)成的數(shù)組。輸出p也是4個(gè)12-bit構(gòu)成的數(shù)組。代碼第17行至第23行是核心部分,包括了對(duì)輸入、輸出添加流水寄存器和加法操作。

責(zé)任編輯:lq

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:并行加法的高效實(shí)現(xiàn)

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

在大數(shù)據(jù)時(shí)代,機(jī)器學(xué)習(xí)算法需要處理的數(shù)據(jù)量日益增長(zhǎng)。為了提高數(shù)據(jù)處理的效率,許多算法都開(kāi)始支持并行計(jì)算。XGBoost作為一種高效的梯度提升樹算法,其并行計(jì)算能力是其受歡迎的原因

![的頭像]() 發(fā)表于

發(fā)表于 01-19 11:17

?738次閱讀

多個(gè)數(shù)據(jù)通道的同時(shí)傳輸。與串行總線相比,并行總線在同一時(shí)間內(nèi)能夠傳輸多個(gè)數(shù)據(jù)位,從而提高了數(shù)據(jù)傳輸?shù)乃俾省_@種并行傳輸方式通常通過(guò)一組數(shù)據(jù)線來(lái)實(shí)現(xiàn),每條線傳輸數(shù)據(jù)的一個(gè)位(bit)。為了確保數(shù)據(jù)的同步和完整性,

![的頭像]() 發(fā)表于

發(fā)表于 10-06 15:17

?1072次閱讀

電子發(fā)燒友網(wǎng)站提供《GaN如何實(shí)現(xiàn)更高效、更緊湊的電源.pdf》資料免費(fèi)下載

發(fā)表于 09-12 10:00

?0次下載

實(shí)現(xiàn)兩個(gè)單一頻率正弦波相加的加法器的芯片選取有什么特殊要求嗎?opa2320可以嗎?

發(fā)表于 09-11 08:30

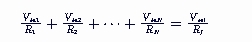

加法運(yùn)放電路實(shí)驗(yàn)報(bào)告的數(shù)據(jù)分析主要包括對(duì)實(shí)驗(yàn)結(jié)果的觀察、與理論值的對(duì)比以及誤差原因的分析。以下是一個(gè)基于常見(jiàn)加法運(yùn)放電路實(shí)驗(yàn)的數(shù)據(jù)分析示例: 一、實(shí)驗(yàn)?zāi)康呐c原理 實(shí)驗(yàn)?zāi)康?:了解加法器的模擬實(shí)

![的頭像]() 發(fā)表于

發(fā)表于 09-03 10:03

?1344次閱讀

加法運(yùn)放電路(也稱為求和放大器)是一種使用運(yùn)算放大器(Op-Amp)來(lái)將多個(gè)輸入信號(hào)相加并放大的電路。在理想情況下,運(yùn)算放大器具有無(wú)限大的開(kāi)環(huán)增益、無(wú)限大的輸入阻抗和零輸出阻抗。這使得運(yùn)算放大器在

![的頭像]() 發(fā)表于

發(fā)表于 09-03 09:50

?895次閱讀

加法器不是時(shí)序邏輯電路 ,而是組合邏輯電路的一種。時(shí)序邏輯電路和組合邏輯電路的主要區(qū)別在于它們?nèi)绾翁幚磔敵鲂盘?hào)。 組合邏輯電路的輸出僅依賴于當(dāng)前的輸入信號(hào),而不依賴于電路之前的狀態(tài)或輸入歷史。這

![的頭像]() 發(fā)表于

發(fā)表于 08-28 11:05

?1128次閱讀

今天我們看的這篇論文介紹了在多FPGA集群上實(shí)現(xiàn)高級(jí)并行編程的研究,其主要目標(biāo)是為非FPGA專家提供一個(gè)成熟且易于使用的環(huán)境,以便在多個(gè)并行運(yùn)行的設(shè)備上擴(kuò)展高性能計(jì)算(HPC)應(yīng)用。

![的頭像]() 發(fā)表于

發(fā)表于 07-24 14:54

?1653次閱讀

邊OTG邊充電芯片實(shí)現(xiàn)充電與數(shù)據(jù)傳輸并行的功能,主要依賴于其內(nèi)部的設(shè)計(jì)和與USB Type-C接口標(biāo)準(zhǔn)的結(jié)合。

![的頭像]() 發(fā)表于

發(fā)表于 07-14 10:35

?1064次閱讀

增益為1的加法器指的是輸出信號(hào)的幅度與輸入信號(hào)幅度相等的加法器。這類加法器在模擬電路設(shè)計(jì)中非常重要,因?yàn)樗鼈冊(cè)趫?zhí)行加法運(yùn)算的同時(shí),不會(huì)改變信號(hào)的幅度。

![的頭像]() 發(fā)表于

發(fā)表于 05-23 15:10

?1434次閱讀

串行加法器和并行加法器是兩種基本的數(shù)字電路設(shè)計(jì),用于執(zhí)行二進(jìn)制數(shù)的加法運(yùn)算。它們?cè)谠O(shè)計(jì)哲學(xué)、性能特點(diǎn)以及應(yīng)用場(chǎng)景上有著明顯的區(qū)別。

![的頭像]() 發(fā)表于

發(fā)表于 05-23 15:06

?3466次閱讀

加法器是數(shù)字電路中的基本組件之一,用于執(zhí)行數(shù)值的加法運(yùn)算。加法器的基本原理和作用可以從以下幾個(gè)方面進(jìn)行詳細(xì)闡述。

![的頭像]() 發(fā)表于

發(fā)表于 05-23 15:01

?4500次閱讀

同相加法器和反相加法器是運(yùn)算放大器在模擬電路設(shè)計(jì)中常用的兩種基本電路結(jié)構(gòu),它們?cè)谛盘?hào)處理方面有著不同的特性和應(yīng)用場(chǎng)景。

![的頭像]() 發(fā)表于

發(fā)表于 05-23 14:35

?3722次閱讀

加法放大器,作為一種重要的電子電路設(shè)備,其在信號(hào)處理、音頻混合、以及多種電子系統(tǒng)中發(fā)揮著關(guān)鍵作用。它基于放大器的線性特性,通過(guò)特定的電路設(shè)計(jì),將多個(gè)輸入信號(hào)進(jìn)行相加,并輸出放大后的信號(hào)。本文將對(duì)加法放大器的原理、特點(diǎn)、設(shè)計(jì)方法以及其在不同領(lǐng)域的應(yīng)用進(jìn)行詳細(xì)的闡述。

![的頭像]() 發(fā)表于

發(fā)表于 05-22 18:09

?2111次閱讀

想做個(gè)加法器,經(jīng)打板焊接,芯片焊接完還用萬(wàn)用表檢測(cè)了,無(wú)短接,虛焊情況。輸入5V后,ICL7660電源極性反轉(zhuǎn)變換器芯片發(fā)熱。但是芯片輸入電壓極限值是10V,輸入5V芯片就發(fā)熱冒煙了。經(jīng)檢查,芯片

發(fā)表于 05-06 16:32

并行加法的高效實(shí)現(xiàn)

并行加法的高效實(shí)現(xiàn)

評(píng)論