本應用筆記介紹了CS61575和CS61574A的抖動衰減性能。它介紹了抖動衰減器電路的描述以及衰減器設計的性能含義。

抖動衰減器電路說明

本節介紹CS61575和CS61574A的抖動衰減器電路。這為更詳細地討論兩個IC的性能差異提供了基礎。

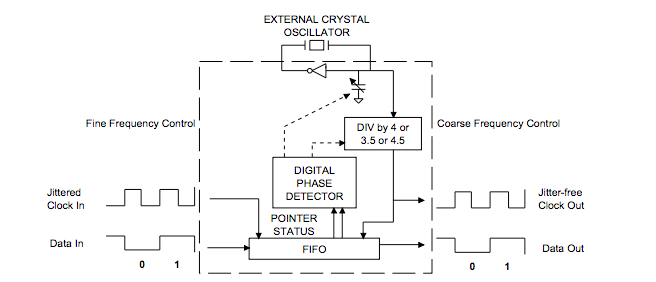

圖1顯示了衰減器電路。抖動衰減器可減少恢復的時鐘信號中的抖動。它由一個FIFO,一個晶體振蕩器,一組用于晶體的負載電容器和控制邏輯組成。恢復的時鐘和數據輸入到FIFO,恢復的時鐘控制FIFO的寫指針。晶體振蕩器控制FIFO的讀取指針,該指針從FIFO中讀取數據。通過改變IC呈現給晶體的負載電容,可以將振蕩頻率精細地調整到恢復信號的平均頻率。邏輯確定讀寫指針之間的相位關系,并決定如何調整晶體的負載電容。因此,抖動衰減器表現為一階鎖相環。信號抖動被FIFO吸收。

抖動衰減器中的FIFO設計為既不上溢也不下溢。如果抖動幅度變得非常大,則讀指針和寫指針可能會變得非常靠近。如果它們試圖交叉,則振蕩器的四分頻電路會通過執行3.5分頻或4.5分頻來進行調整,以防止FIFO上溢或下溢。這是對輸出時鐘的粗略調整。在此活動期間,數據將永遠不會丟失,但會發生抖動增益。

衰減器設計的性能含義

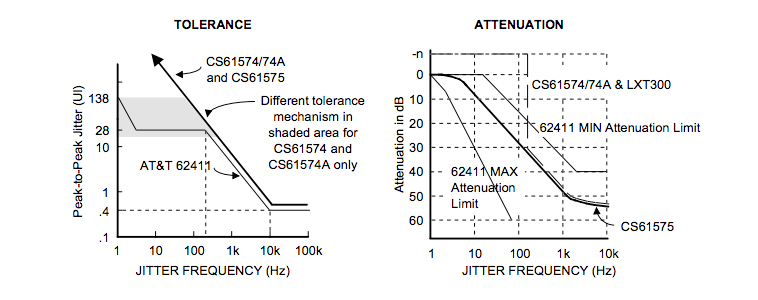

如圖2所示,CS61575,CS61574A和CS61574都可以忍受AT&T 62411定義的輸入抖動。(請注意,所有其他最近的標準都要求10 UI的最大容限)。但是,當輸入幅度超過23 UI時,CS61575繼續提供連續的抖動傳遞功能。如圖2所示,當將超過23個UI輸入到CS61574A,CS61574或類似設備(例如LXT300)時,除以3.5或4.5的機制將產生抖動增益。

AT&T 62411要求的變更

1990年12月,AT&T更改了在62411上使用的高頻抖動傳遞測試程序,該程序正式要求60 dB的衰減(任何供應商的任何線路接口IC在所有操作條件下都無法達到的性能水平),最新的62411規范僅要求40 dB衰減。

編輯:hfy

-

fifo

+關注

關注

3文章

400瀏覽量

44678 -

衰減器

+關注

關注

4文章

726瀏覽量

35033 -

晶體振蕩器

+關注

關注

9文章

688瀏覽量

30109 -

CS61575

+關注

關注

0文章

3瀏覽量

6676

發布評論請先 登錄

CS51411/CS51412/CS51413/CS5141

cs54111/cs54112/cs54113/cs5411

CS51023A, CS51024A pdf datashe

CS51023, CS51024 pdf datasheet

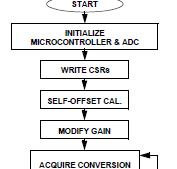

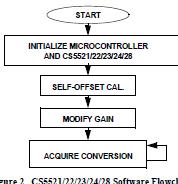

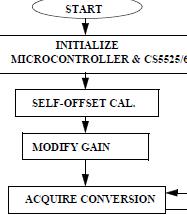

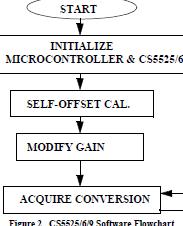

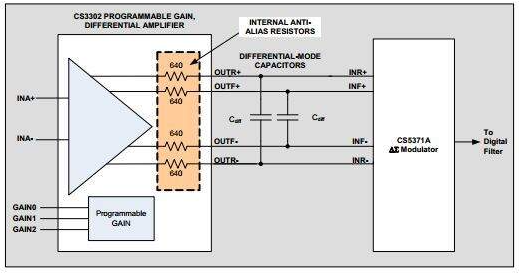

CS5521 CS5522 CS5523 CS5524 CS5528 AD轉換器與68HC05微控制器接口

CS5521 CS5522 CS5523 CS5524 CS5528 AD轉換器與PIC16C84微控制器接口

CS5521 CS5522 CS5523 CS5524 CS

基于CS61575和CS61574A的抖動衰減設計

基于CS61575和CS61574A的抖動衰減設計

評論