作為硬件/PCB/SI工程師一個基礎性的日常操作,從板材選型,PP選型,銅箔選型,然后分配厚度,對于設計疊層相信有經驗的粉絲們都get得七七八八了。但是設計中的這一點差別你們都有考慮過嗎???

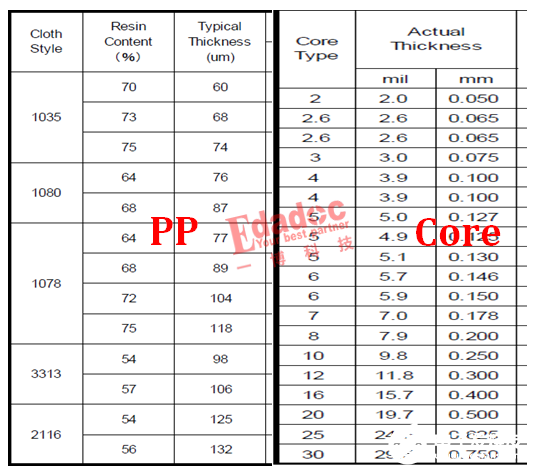

常規的疊層操作方法我們都已經懂了,無非就是看長度吃飯。長度決定我們要的板材級別,然后PP盡量選好的,也就是盡量不要選單張106或者1080(不要再問高速先生為什么了哈,我們會生氣的)。然后選好PP/core的厚度之后就把對應阻抗的線寬/線距算出來,交給板廠確認一下就基本OK了。

但是呢,有一個很重要的點不知道你們在設計疊層,或者看別人的疊層時有沒有發現。好吧,高速先生給你們舉個例子說明下咯。

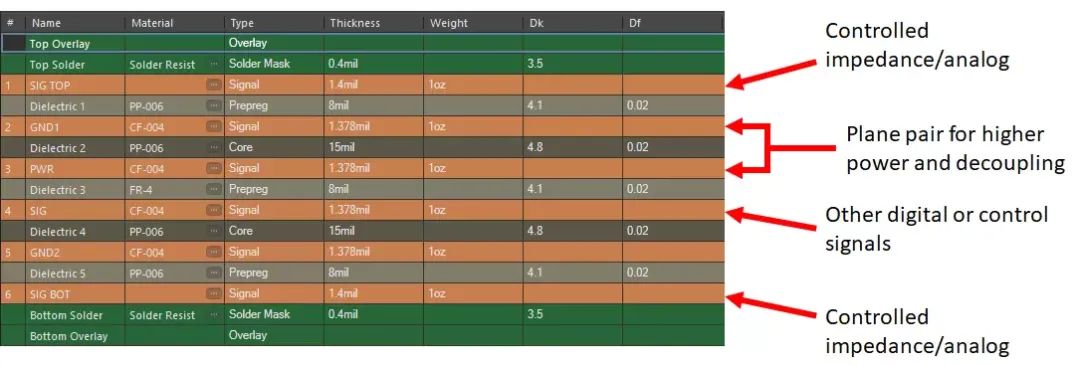

假設我們在做一個很厚的背板的疊層設計時,通過分配走線層數之后得到一個地-信號層-地的組合能分到15mil,就像下圖所示:

打開你們的PP和CORE的line-up之后,問題來了,你們會怎么選擇在上下兩層去分配PP/core呢?

根據以上的參數會有很多種組合,例如3milPP-12mil Core,又或者5milPP-10mil Core,那么我們來選2種最極端的組合,如下所示:

這兩種疊層有什么不一樣嗎?不就是用不一樣的PP和CORE來湊夠厚度嗎?如果你們算阻抗的話,你就會發現它們最大的區別了。

時間關系我們已經大概幫你算出來了,這兩者疊層的線寬線距是這樣的:

說到了線寬不同,你們就會知道關于它的最大的秘密來了,那就是什么?你們大聲的說出來!!!

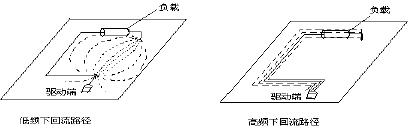

對,那就是損耗。如果同樣是10inch的走線,4mil的線寬和6mil線寬的損耗在10GHz處其實可以差得很多。

對于走線很長或者裕量很緊張的情況,其實這個無形的差別就顯得非常的重要了。大家想一想,要是走線走到了20inch時,然后速率在25Gbps,那這個差距更大了。

一般按照我們高速先生的風格,寫到這里就基本上要結束了。但是這個劇情還會有反轉,本來想留到答題的時候再進行分析,但是粉絲們可能知道我們高速先生一貫的套路,答題也就是回答下網友的問題,并沒有周一正文那么經典,因此干脆就把反轉的劇情提前劇透了。

大家有沒有想過,6mil會比4mil線寬要寬(這不是fei話嗎?)。我們知道板子的空間是一定的,如果一對差分線占用的2W+S多了,那么差分對與差分對的間距就近了,我們在保證兩種情況下差分對間中心距一樣的前提下再進行仿真,當然我們要看的就是兩種情況下的串擾結果了。

劇情果然反轉了,6mil線寬在串擾上是差的。細思一下當然也很正常,線寬寬了,空間用到這里去了,那么對間的間距自然就得近咯,因為空間是確定的,就看你是用到線寬還是間距那里咯。好,這篇文章到這里就真正結束了。

編輯:hfy

-

pcb

+關注

關注

4358文章

23443瀏覽量

407724 -

背板

+關注

關注

0文章

29瀏覽量

16616 -

疊層

+關注

關注

0文章

29瀏覽量

10077

發布評論請先 登錄

6層PCB疊層設計指南

關于PCB技術中背板的疊層設計

關于PCB技術中背板的疊層設計

評論