走線熙熙,汲汲交期;走線攘攘,亟亟歸檔。

項(xiàng)目伊始,高速先生的內(nèi)心其實(shí)是抗拒的,因?yàn)閷?shí)在看不出仿真的必要:目標(biāo)信號(hào)是DDR3L,數(shù)據(jù)速率最高800Mbps,地址控制類信號(hào)走線拓?fù)錇橐煌隙型拓?fù)洹P盘?hào)普通、速率尋常、拓?fù)浜?jiǎn)單。

架不住客戶的一再堅(jiān)持,加上前期項(xiàng)目介入階段,客戶言辭閃爍,提供PCB文件時(shí)也不大爽快,似乎有難言之隱,高速先生漸生警覺——事情可能并沒有想象的那么簡(jiǎn)單。客戶最終還是提供了單板文件,不過(guò)一直強(qiáng)調(diào)是外協(xié)設(shè)計(jì)的。

打開板子仔細(xì)查看,卻是險(xiǎn)象環(huán)生,高速先生精神為之一振,心里大概有了譜。雖然有了預(yù)判,不過(guò),對(duì)于如此不走尋常路的設(shè)計(jì)以前只是耳聞,今日一見,難免興奮,實(shí)在想看看仿真結(jié)果與預(yù)期是否一致。

考慮選擇地址控制類信號(hào)作為仿真對(duì)象,之所以這么做除了因?yàn)樵搯伟宓拇祟愋盘?hào)布線激進(jìn),另一個(gè)原因是相對(duì)于絕大多數(shù)數(shù)據(jù)信號(hào)的點(diǎn)到點(diǎn)拓?fù)洌刂房刂祁愋盘?hào)通常是一拖多,而且沒有數(shù)據(jù)信號(hào)對(duì)應(yīng)的片內(nèi)端接來(lái)減小反射,因此出問(wèn)題的概率相對(duì)較大。先看DDR3L地址控制類走線最長(zhǎng)的信號(hào)波形(如下圖):高低電平分明,滿足閾值要求,邊沿單調(diào),沒有回溝,整體看來(lái)雖然有輕微的過(guò)沖和振鈴,不是十分完美,也算比較正常。

難道就這樣愉快的PASS了?不,還沒到重點(diǎn)。因?yàn)橥ǖ勒w仿真的結(jié)果會(huì)讓你得出截然相反的結(jié)論!不信請(qǐng)看同組地址信號(hào)同時(shí)運(yùn)行時(shí)黯然失色的眼圖:仿佛熬夜之后勉強(qiáng)睜開的眼睛,布滿血絲,感受到他的疲憊了嗎?

不好意思,放錯(cuò)圖了,應(yīng)該是這張。

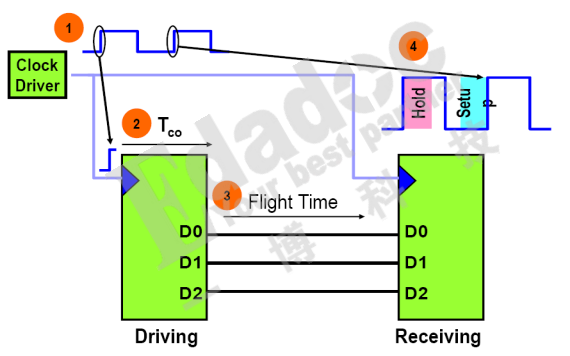

單拎出來(lái)的信號(hào)質(zhì)量沒問(wèn)題,同組信號(hào)一起運(yùn)行卻不給力,想必一直關(guān)注高速先生公眾號(hào)的朋友已經(jīng)想到了答案:串?dāng)_!是的,高速先生也這么想。尤其是在高速先生新近推出一期關(guān)于層間串?dāng)_的短視頻之后,串?dāng)_問(wèn)題更是引起了不少人的關(guān)注。

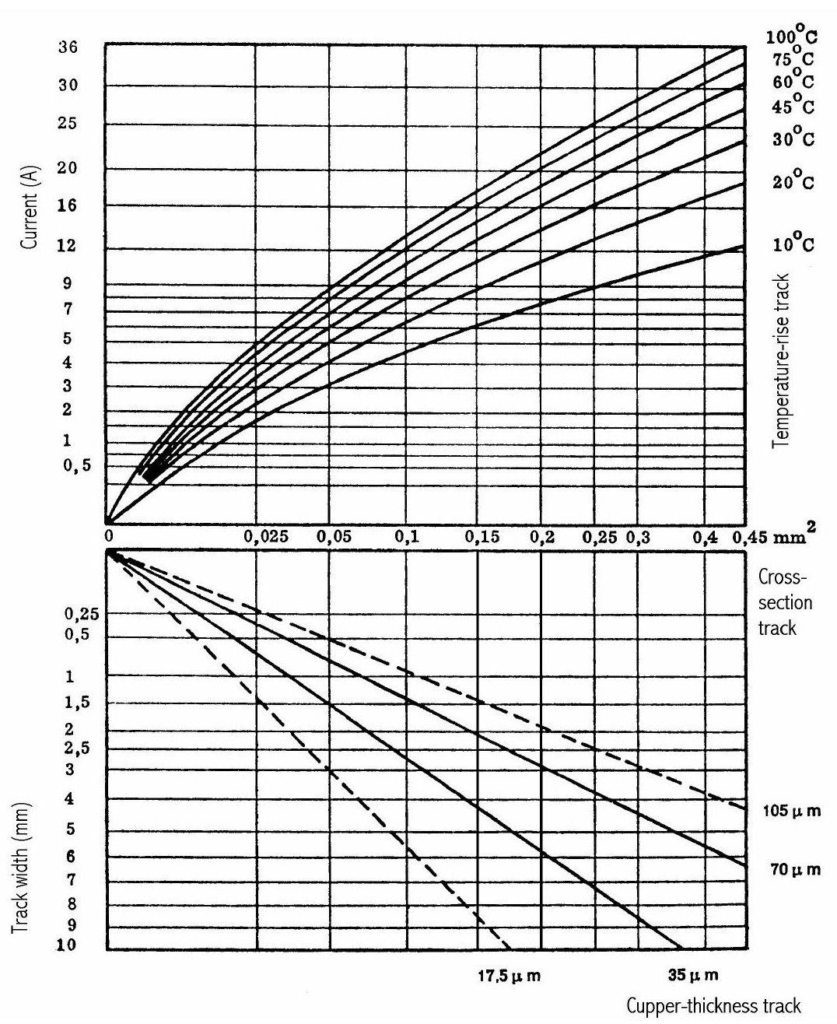

回到本期案例,繼續(xù)抽絲剝繭。仔細(xì)觀察DDR3L地址信號(hào)走線之間的間距就能發(fā)現(xiàn)端倪:線寬0.1mm,相鄰走線air-gap也是0.1mm!而且還不是零散的個(gè)別現(xiàn)象,整個(gè)通道的地址控制類信號(hào)都是如此處理。

當(dāng)然了,以上關(guān)于串?dāng)_的推斷還只是大膽的假設(shè),下面就需要小心的求證。既然懷疑問(wèn)題的癥結(jié)在于串?dāng)_,那么對(duì)比不同程度的串?dāng)_對(duì)通道信號(hào)的影響最具有說(shuō)服力。好在仿真的時(shí)候可以調(diào)整串?dāng)_系數(shù),這樣就不必等客戶提供不同的PCB版本來(lái)逐一驗(yàn)證。提取參數(shù)時(shí)通過(guò)調(diào)整串?dāng)_系數(shù),先將串?dāng)_降低為原版本的75%,由于振鈴的減小,眼睛中的“血絲”開始減少,眼圖如下:

繼續(xù)調(diào)整串?dāng)_系數(shù),將串?dāng)_減小至原設(shè)計(jì)的50%,信號(hào)振鈴進(jìn)一步減小,眼圖逐漸恢復(fù)正常。

直接將串?dāng)_減小到原設(shè)計(jì)的5%,整個(gè)眼圖都變的精神抖擻,十分清爽。

通過(guò)仿真反饋,客戶最終還是把DDR3L的走線中心距調(diào)整至3W,線距調(diào)整后的通道仿真結(jié)果達(dá)到了預(yù)期的要求。

后來(lái)才了解到,初始版本PCB是客戶的一個(gè)Layout新手設(shè)計(jì),初生牛犢不怕虎,加上交期的壓力,走線約束設(shè)置出現(xiàn)偏差,于是就出現(xiàn)了這么一版試探信號(hào)底線的設(shè)計(jì),相信經(jīng)過(guò)這次返工的煎熬,串?dāng)_對(duì)這名Layout攻城獅而言不會(huì)再是書本上蒼白的理論。正所謂:走線熙熙,急趕交期;走線攘攘,串?dāng)_飆漲。只是,有多少走線可以重來(lái),有多少單板經(jīng)得起等待?

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4359文章

23449瀏覽量

407880 -

DDR3

+關(guān)注

關(guān)注

2文章

283瀏覽量

43010

發(fā)布評(píng)論請(qǐng)先 登錄

混合信號(hào)PCB設(shè)計(jì)有什么注意事項(xiàng)?

PCB設(shè)計(jì)有哪些問(wèn)題需要注意?

GSM手機(jī)在PCB設(shè)計(jì)有什么要求和技巧

開關(guān)電源的PCB設(shè)計(jì)(布局、排版、走線)規(guī)范

開關(guān)電源的PCB設(shè)計(jì)(布局、排版、走線)規(guī)范

PCB設(shè)計(jì)布線中的3種特殊走線技巧

pcb開窗怎么設(shè)計(jì)_PCB設(shè)計(jì)怎樣設(shè)置走線開窗

PCB設(shè)計(jì)有哪些誤區(qū)PCB設(shè)計(jì)的十大誤區(qū)上部分內(nèi)有下部分鏈接

PCB設(shè)計(jì)有哪些誤區(qū)PCB設(shè)計(jì)的十大誤區(qū)下部分內(nèi)有上部分鏈接

高速PCB設(shè)計(jì)有沒有什么技巧

PCB設(shè)計(jì)有著怎樣的規(guī)范

PCB設(shè)計(jì)有哪些地方容易錯(cuò)

SMT生產(chǎn)設(shè)備對(duì)PCB設(shè)計(jì)有哪些要求

可以優(yōu)化ESD防護(hù)的PCB設(shè)計(jì)準(zhǔn)則

有關(guān)PCB走線以及如何為PCB設(shè)計(jì)正確走線的重要事項(xiàng)

PCB設(shè)計(jì)有多少線可以重來(lái)?

PCB設(shè)計(jì)有多少線可以重來(lái)?

評(píng)論