對新設計方法的需求

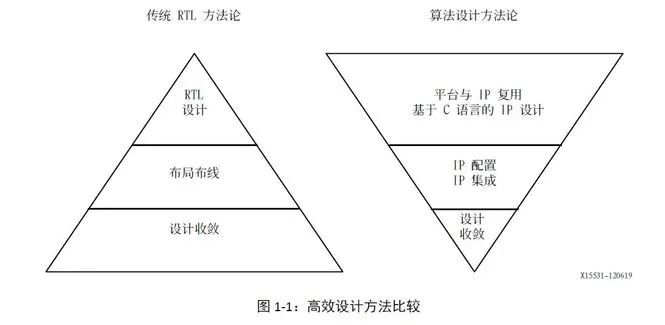

當今日益復雜的電子產品中所使用的先進設計正在不斷對器件密度、性能和功耗的極限發起挑戰,同時也對設計團隊提出了挑戰,要求他們在限定的預算內按時完成設計目標。 應對這些設計挑戰的高效方法之一是將更多時間投入到更高的抽象層,這樣即可最大程度縮短驗證時間和提升工作效率。對新設計方法的需求在下圖中得到了充分體現,其中每個區域的面積分別代表設計流程中每個階段的開發工作量的比例。

對傳統 RTL 方法而言,大部分工作主要耗費在實現的細節工作上。

在高效設計方法中,大部分工作主要集中于設計系統和驗證構建的系統是否正確。

關于本指南

賽靈思可編程器件含有數百萬個邏輯單元 (LC),并且集成的現代復雜電子系統也與日俱增。本高效設計方法指南提供了一整套最佳做法,旨在于較短的設計周期內完成此類復雜系統的創建。

本方法指南主要圍繞下列概念展開:

使用并行開發流程來提供有價值的差分邏輯,使您的產品在市場中脫穎而出,并提供 shell 用于將此類差分邏輯與生態系統其余部分有機整合。

廣泛使用基于 C 語言的 IP 開發流程實現差分邏輯,使仿真速度較 RTL 仿真成倍增長,并提供時序精確且經過最優化的 RTL。

使用現有預驗證的塊級和組件級 IP 來快速構建 shell,將差分邏輯封裝到系統中。

使用腳本來實現從設計精確性驗證到 FPGA 編程在內整個流程的高度自動化。

本指南中的建議是根據多年來廣泛收集的專家級用戶經驗總結而成的。與傳統 RTL 設計方法相比,這些建議持續不斷實現了各方面提升,包括:

1) 設計開發時間加快 4 倍。

2) 衍生設計開發時間加快 10 倍。

3) 結果質量 (QoR) 提高 0.7 倍到 1.2 倍。

雖然本指南以大型復雜設計為重點,但其中論述的做法也同樣適用于并已成功應用到下列各類設計中:

● 數字信號處理

● 圖像處理

● 視頻

● 雷達

● 汽車

● 處理器加速

● 無線

● 存儲

● 控制系統

傳統方法與高效設計方法的區別

傳統設計方法

傳統設計開發首先是由有經驗的設計人員預估如何使用新技術來實現自己的設計、完成寄存器傳輸級(RTL)的設計捕獲、通過綜合和布局布線執行一些嘗試以確認自己的預估是否正確,然后繼續開展設計其余部分的捕獲工作。在此過程中通常需要逐一對每個塊進行綜合,以重復確認設計的實現細節是否可接受。 確認設計能否提供所需功能的主要方法是對 RTL 進行仿真。由于 RTL 可提供極為詳細的位精度和周期精度描述,雖然這些描述精度極高,但此流程仍較為緩慢且易于出錯。僅當在 RTL 中捕獲設計中的所有塊之后才能執行完整的系統驗證,這往往會導致對 RTL 進行反復調整。在系統中的全部塊驗證完畢后,即可對其進行集中布局布線,此時才能完全確認先前預估的時序和面積的精確性,或者發現其中不精確的地方。這也往往會導致對 RTL 進行更改、重新啟動系統驗證以及重新進行實現。 設計人員現在通常需要在給定工程中實現數十萬行 RTL 代碼,把大部分設計時間都用在實現的細節工作上。如圖 1-1 所示,設計人員把更多時間用在設計的實現上,而不是設計出使所有產品保持競爭力所需的新穎創新的解決方案。

無論是采用更新的技術以提升性能,還是采用更緩慢的技術以提供更具競爭力的定價,都意味著必須重寫大部分 RTL,并且設計人員必須重新實現寄存器間的大量邏輯。

高效設計方法指南

高效設計方法沿襲了傳統 RTL 方法的基本步驟,如圖 1-1 所示。但是,它能夠讓設計人員把更多時間用來設計增值解決高效設計方法,該方法的主要特性包括:

提出了隨差分邏輯并行開發并驗證的 shell 概念。此 shell 包含差分邏輯,用于捕獲獨立設計工程中的 I/O 外設和接口。

使用基于 C 語言的 IP 仿真,使仿真時間相比于傳統 RTL 仿真縮短多個數量級,為設計人員提供了設計理想解決方案的時間。

借助賽靈思 VivadoDesign Suite 利用基于 C 語言的 IP 開發、IP 復用和標準接口,實現時序收斂的高度自動化。

使用 Vivado IP 目錄輕松復用您自己的塊級和組件級 IP,還能輕松獲取賽靈思 IP,這些 IP 均已驗證且已知在技術中能夠有效。

高效設計方法中的所有步驟都能交互執行,也可使用命令行腳本來執行。所有人工交互的結果均可保存到腳本,實現從設計仿真直至 FPGA 編程的整個流程的完全自動化。根據您的設計和 RTL 系統級仿真的運行時間,該流程通常在任何 RTL 設計仿真完成之前即可在開發板上生成 FPGA 比特流并對設計進行測試。

創建衍生設計時,效率提升將更為明顯。基于 C語言的 IP 能夠與不同器件、技術和時鐘速度輕松對應,就像更改工具選項一樣簡單。完全腳本化的流程與通過 C 語言綜合實現的自動時序收斂意味著能夠快速完成衍生設計的驗證和組裝。

責任編輯:lq

-

賽靈思

+關注

關注

33文章

1796瀏覽量

132142 -

C語言

+關注

關注

180文章

7630瀏覽量

140511 -

可編程器件

+關注

關注

2文章

60瀏覽量

21142

原文標題:傳統與創新設計的區別有多大?看了它你就知道了!

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

物聯網卡與傳統 SIM 卡的區別,看完你就懂了

柔性網線和非柔性網線區別有哪些

2024全國大學生FPGA創新設計競賽紫光同創杯勇攀新高

AIGC與傳統內容生成的區別 AIGC的優勢和挑戰

DAC7714和DAC7715有區別嗎?DAC7714支持最大的SPI通信速率是多大?

AIGC與傳統內容生成的區別

AI大模型與傳統機器學習的區別

工控機與服務器的區別有哪些?

錫膏印刷與回流焊空洞的區別有哪些?

傳統與創新設計的區別有多大?

傳統與創新設計的區別有多大?

評論