在FPGA開發(fā)板設(shè)計(jì)時(shí),為任何基于SERDES的協(xié)議選擇一個(gè)參考時(shí)鐘源都是非常具有挑戰(zhàn)性的。器件成本、通過耦合高速信號(hào)使得噪聲最小化、超低抖動(dòng)要求、由于信號(hào)長(zhǎng)度匹配的要求而對(duì)走線的限制、考慮周全的電源供電設(shè)計(jì)(包括噪聲的考慮、元件布局上的限制、信號(hào)布線的要求和電源去耦)以及測(cè)試/生產(chǎn)要求,這些都必須考慮到并對(duì)各個(gè)因素的利弊進(jìn)行權(quán)衡分析。

為滿足目前的56GPAM-4SerDes技術(shù),以支持更高帶寬的100G+以太網(wǎng)和光網(wǎng)絡(luò)設(shè)計(jì)。硬件開發(fā)人員通常需要100fs(典型值)以下RMS相位抖動(dòng)規(guī)范的時(shí)鐘。這些設(shè)計(jì)通常需要與CPU和系統(tǒng)時(shí)鐘等其他頻率時(shí)鐘混用。

在選取參考時(shí)鐘參考源時(shí),必須選取超低抖動(dòng)的時(shí)鐘芯片以滿足互聯(lián)網(wǎng)基礎(chǔ)設(shè)施的嚴(yán)格規(guī)范和高性能要求,同時(shí)也要考慮各種時(shí)鐘應(yīng)用的成本和復(fù)雜性。

針對(duì)56G/112G的Serdes接口,目前市場(chǎng)上知名度大的是Silicon發(fā)布的Si539x系列時(shí)鐘,它能夠從任意頻率輸入時(shí)鐘產(chǎn)生任意頻率輸出時(shí)鐘組合,同時(shí)提供業(yè)界領(lǐng)先的抖動(dòng)性能(90fsRMS相位抖動(dòng)),其中Si5395/4/2P級(jí)時(shí)鐘器件為56G/112GSerDes時(shí)鐘應(yīng)用提供了最佳的抖動(dòng)性能(69fsRMS典型相位抖動(dòng))。

責(zé)任編輯:lq

-

以太網(wǎng)

+關(guān)注

關(guān)注

41文章

5635瀏覽量

175956 -

單通道

+關(guān)注

關(guān)注

0文章

407瀏覽量

18620 -

時(shí)鐘源

+關(guān)注

關(guān)注

0文章

98瀏覽量

16328

原文標(biāo)題:SI-list【中國(guó)】單通道56G的SERDES,參考時(shí)鐘如何選取?

文章出處:【微信號(hào):si-list,微信公眾號(hào):高頻高速研究中心】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Electronica現(xiàn)場(chǎng)演示 | 嚴(yán)苛環(huán)境下的56G互連

從SerDes到SoC,全場(chǎng)景適配的FCom差分晶振設(shè)計(jì)全解

是德科技 單通道448G未來之路:PAM4? PAM6? PAM8?

448 Gbps多級(jí)脈沖幅度調(diào)制測(cè)試方案

PCB仿真相同損耗下,28G NRZ的產(chǎn)品不能直接升級(jí)到56G PAM4?

DLPDLCR4710EVM-G2如何實(shí)現(xiàn)單通道無閃爍地圖像輸出?

如何使用ADC08D1000的芯片進(jìn)行1G雙通道采樣或2G單通道采樣?

高速線纜在數(shù)據(jù)中心的應(yīng)用和解決方案

基于兆易創(chuàng)新GD32G553系列MCU的單通道可編程高精度直流源表設(shè)計(jì)

config108讀取config108寄存器的值時(shí)鐘為000f,只是serdes_pll未鎖定,為什么?

請(qǐng)問ADC12DJ3200如何實(shí)現(xiàn)雙通道、單通道模式切換?

有單通道數(shù)據(jù)鎖存模塊嗎?

單通道、配電開關(guān)評(píng)估模塊

了解高速56G PAM-4串行鏈路的時(shí)鐘需求

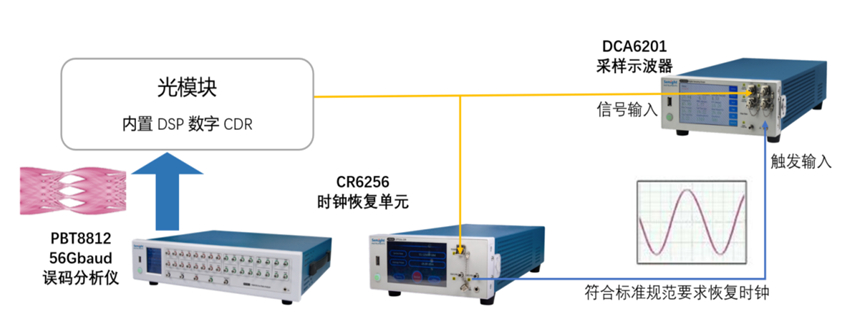

56Gbaud CR6256!400G/800G單多模光模塊及接口的時(shí)鐘提取

單通道56G的SERDES,參考時(shí)鐘如何選取?

單通道56G的SERDES,參考時(shí)鐘如何選取?

評(píng)論