軟件定義無線電是當今業(yè)界的主要話題之一。射頻(RF)收發(fā)器在單芯片集成電路中(IC)中提供了完整的無線電解決方案,推動了軟件定義無線電的領域的發(fā)展。ADI 收發(fā)器產品線推出了這類強大的芯片,正快速應用于許多通過軟件控制的無線電設計中。但是如何獲得較低的相位噪聲仍是使用這些器件需要探索的領域之一。本文評估這些高度集成的射頻集成電路(RFIC)的相位噪聲性能,重點評估提供外部頻率時的情況。

使用外部本振(LO)時對ADI公司 ADRV9009 收發(fā)器進行測量表明,當使用低噪聲LO時,可顯著改善相位噪聲。從相位噪聲貢獻角度來分析收發(fā)器架構。通過一系列測量,殘余或加性相位噪聲被提取為在DAC輸出編程的頻率的函數(shù)。利用該噪聲貢獻以及LO和參考電壓輸入頻率的相位噪聲,可估計出發(fā)射輸出的總相位噪聲。將這些估計值與測得的結果進行比較。

動機 相位噪聲是無線電設計中表征信號質量的重要指標之一。在架構定義階段需要進行大量工作,確保以經濟的方式滿足相位噪聲需求。

通過分析ADRV9009收發(fā)器的測量結果,其噪聲性能結果卻決于所選架構,不同架構結果差異較大。使用內部LO功能時,相位噪聲由IC內部的鎖相環(huán)(PLL)和壓控振蕩器(VCO)決定。內部LO在設計上能滿足大多數(shù)通信應用的需求。對于需要改進相位噪聲的應用,將低相位噪聲源作為外部LO時,可顯著改進相位噪聲。

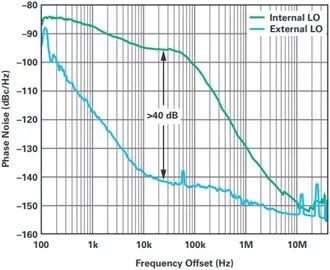

如圖1所示,ADRV9009收發(fā)器在10 kHz至100 kHz頻段相位噪聲改善超過40 dB。以上測量的條件為:對于內部LO測量,LO頻率設置為2.6 GHz, DAC輸出為8 MHz。對于外部LO測量,Rohde & SchwarzSMA100B用作LO源。由于外部LO信號需要經過ADRV9009的內部分頻器,因此為獲得2.6 GHz的LO頻率,信號源設置為5.2 GHz。使用Holzworth HA7402相位噪聲分析儀進行相位噪聲的測量。

圖1. ADRV9009收發(fā)器相位噪聲測量。使用內部LO時,相位噪聲受到IC內部PLL/VCO的限制。如果使用低相位噪聲外部LO,可顯著改進相位噪聲。

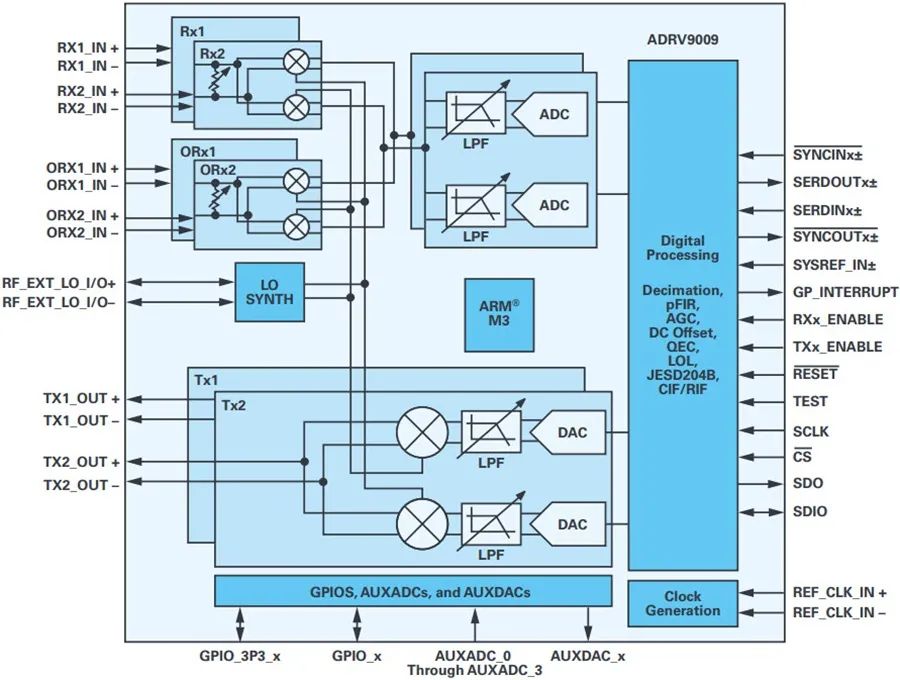

ADRV9009收發(fā)器 ADRV9009是ADI收發(fā)器產品線的新產品。收發(fā)器架構如圖2所示。該芯片使用直接變頻架構,將發(fā)射和接收雙通道收發(fā)鏈路集成在單芯片中。其中包含正交校正、直流失調和LO泄漏校正等數(shù)字處理算法,這些算法保證了直接變頻架構的性能。收發(fā)器提供了射頻(RF)與數(shù)字之間轉換的完整功能。支持高達6GHz的RF頻率,JESD204B接口則為基于ASIC或FPGA的處理器提供高速數(shù)據(jù)接口。

圖2. ADRV9009收發(fā)器功能框圖。

無線電與外部輸入的參考頻率同步。轉換器時鐘、LO和數(shù)字時鐘的PLL均會與參考時鐘鎖相。通過外部LO的配置可以繞過內部LO PLL。LO路徑的PLL或外部LO輸入與混頻器端口之間有一個分頻器,用于生成直接變頻架構所需的正交LO信號。轉換器時鐘和LO會直接影響相位噪聲,在評估相位噪聲貢獻因素時我們會對此進行進一步討論。

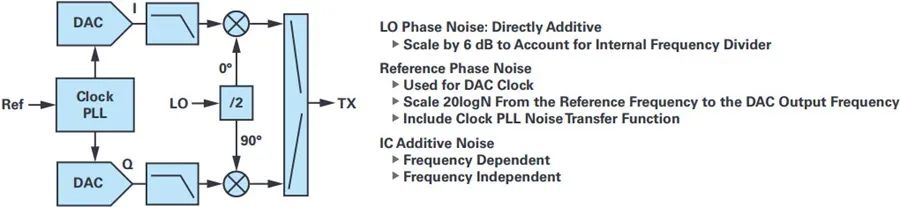

檢查相位噪聲貢獻因素 發(fā)射的相位噪聲由多個因素組成。圖3闡明了使用直接變頻波形發(fā)生器架構的簡單功能框圖以及主要相位噪聲因素。

圖3. 直接上變頻功能框圖和關聯(lián)相位噪聲貢獻因素。

在倍頻器或分頻器中,相位噪聲的比例為20logN,其中N是輸入輸出頻率比。

這比例也適用于直接數(shù)字頻率合成器(DDS),其中時鐘噪聲貢獻與DDS輸出頻率的比例為20logN。

要考慮的第二個方面是PLL中的相位噪聲傳遞函數(shù),注入PLL的基準頻率將作為頻率比例函數(shù)(類似于倍頻器)按比例分配到輸出,但會受環(huán)路帶寬(BW)和所選的環(huán)路濾波器所形成的低通濾波器影響。

將這些原則應用于收發(fā)器,可檢查各種噪聲因素的貢獻。注入收發(fā)器的頻率有兩種,即LO頻率和基準頻率。LO頻率直接影響相位噪聲輸出,但在用于創(chuàng)建混頻器正交LO信號的內部分頻器中減少了6 dB。基準頻率貢獻由幾個因素決定。它用于在時鐘PLL中創(chuàng)建DAC時鐘。時鐘輸出上由于基準頻率而產生的噪聲將與PLL的噪聲傳遞函數(shù)成比例。然后,這種噪聲貢獻再次與DAC時鐘與DAC輸出頻率比成比例。這種效果可以簡化為基準頻率和DAC輸出頻率的比例,并受PLL BW低通傳遞函數(shù)影響。

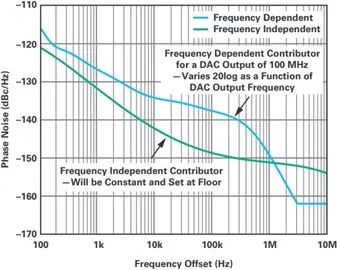

接下來,考慮收發(fā)器相位噪聲貢獻。在發(fā)射路徑中,所有電路元件都會產生殘余噪聲,另一個噪聲貢獻是DAC輸出的加性噪聲,它隨DAC輸出頻率而變化。這可以總結為兩個殘余相位噪聲術語:頻率相關噪聲貢獻和頻率無關噪聲貢獻。頻率相關噪聲與DAC輸出頻率的比例為20logN。頻率無關噪聲是固定的,將作為收發(fā)器的相位噪底。

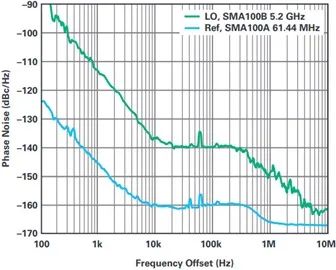

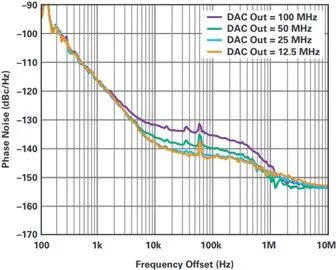

為了提取IC殘余噪聲貢獻作為頻率相關貢獻因素和頻率無關貢獻因素的函數(shù)進行了一系列相位噪聲測量,如圖4所示。

(a). The Reference Frequency and LO Frequency.

(b). The Transceiver Transmit Output Phase Noise.

(c). The Transceiver Residual Phase Noise.

圖4. 用于提取可變相位噪聲貢獻因素的相位噪聲測量。

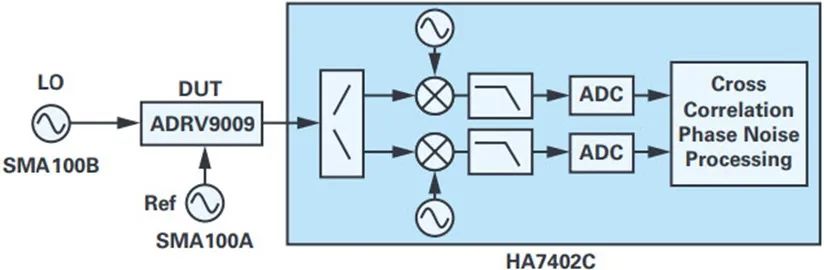

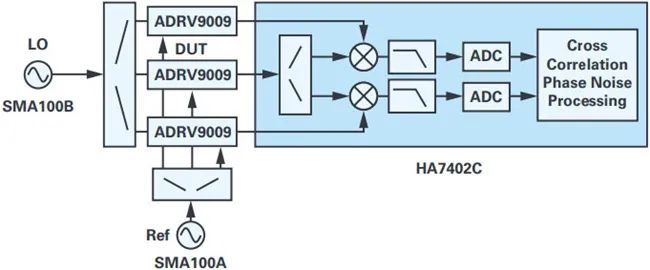

用于相位噪聲測量的測試設置如圖5所示。對于收發(fā)器LO和基準頻率輸入,分別使用了Rohde & Schwarz SMA100B和100 A。Holzworth HA7402C用作相位噪聲測試設置。對于絕對相位噪聲測量,將收發(fā)器的發(fā)射輸出注入測試設置。對于殘余相位噪聲測量,需要三個收發(fā)器,并且將額外的收發(fā)器作為測試設置中混頻器的LO端口,可從測量中去除基準頻率和LO頻率的噪聲貢獻。

(a). Absolute Phase Noise Measurement.

(b). Residual Phase Noise Measurement.

圖5. 用于相位噪聲測量的測試設置。

通過評估圖4的實測數(shù)據(jù),從收發(fā)器IC中提取了頻率相關和頻率無關相位噪聲貢獻因素。估計值如圖6所示。估計值來自于對實測數(shù)據(jù)的擬合結果以及在偏移頻率大于1 MHz時對相位噪底應用的閾值設置。

圖6. 收發(fā)器殘余相位噪聲貢獻。這些曲線是從圖4的實測數(shù)據(jù)中提取出來的。

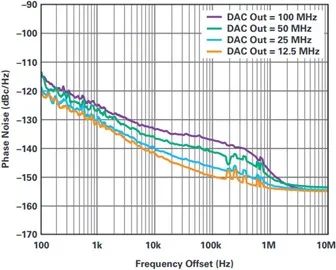

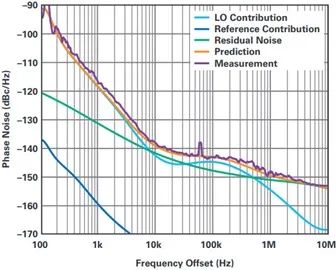

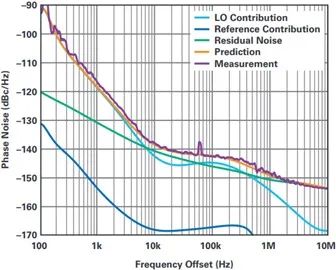

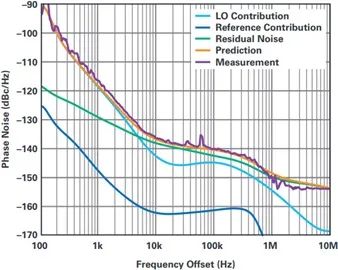

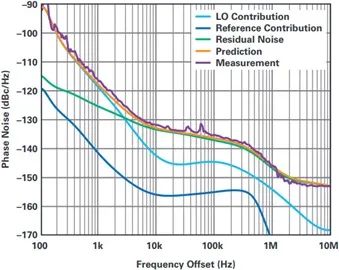

絕對相位噪聲測量和預測 如前所述通過評估不同相位噪聲貢獻,基于DAC輸出頻率以及用于參考和本振的振蕩源,相位噪聲可以通過計算預測。實測和預測結果如圖7所示。

(a). DAC Ouput = 12.5 MHz.

(b). DAC Output = 25 MHz.

(c). DAC Output = 50 MHz.

(d). DAC Output = 100 MHz.

圖7. 外部LO的測量相位噪聲與預測相位噪聲的對比。對于2.6 GHz的收發(fā)器中心頻率,LO設置為5.2GHz。DAC輸出頻率從12.5 MHz到100 MHz不等。結果是可預測的,并表明這種分析方法可以推廣到額外的頻率。

貢獻可通過下式計算:

LO相位噪聲貢獻:使用了圖4測得的LO相位噪聲,并將其降低了6 dB,以對應收發(fā)器內部的分頻器。

參考相位噪聲貢獻:以圖4的實測參考噪聲作為起始點。收發(fā)器中的時鐘PLL具有幾百kHz的環(huán)路帶寬,因此采用具有類似環(huán)路帶寬的二階低通濾波器來抑制參考噪聲。然后將噪聲按DAC輸出頻率與基準頻率比的20log進行縮減。

IC貢獻:使用了圖6的曲線。

測量結果與預測結果非常接近,圖表顯示了哪些貢獻因素控制不同的偏移頻率。在低于5 kHz左右的偏移頻率下,第一個LO占主導地位。在高于1 MHz左右的偏移頻率下,IC殘余噪聲占主導地位。在10 kHz左右至500 kHz左右的中等偏移頻率下,DAC輸出頻率成為一個因素。在較高的DAC輸出頻率下,IC頻率相關噪聲占主導地位。降低DAC輸出頻率時,IC貢獻減至LO頻率主導性能的那個點。

外部LO考慮因素

探索外部LO用法的設計有一些因素值得注意。有兩點可能有所限制:

使用內部分頻器時,啟動或切換外部LO時存在相位模糊。內部LO包含RF相位同步功能,這是外部LO尚不具備的。

當外部LO跳頻時,QEC算法存在一個建立時間,該時間可能在頻率變化后的瞬間以雜散方式影響圖像。

這兩項都導致了多通道系統(tǒng)跨越大于收發(fā)器瞬時帶寬工作的復雜性。未來的收發(fā)器可能會克服這些限制,但在撰寫本文之際,當ADRV9009與外部LO一起使用時,這些復雜性依然存在。

盡管存在這些復雜性,仍有許多應用可以利用外部LO改進相位噪聲。其中包括具有不太嚴格的動態(tài)跳頻要求的任何單通道或低通道系統(tǒng),或任何具有固定LO頻率的多通道系統(tǒng)。

如窄帶相控陣這種特殊應用使用外部LO可以獲得更好的相位噪聲性能。在該應用中,使用收發(fā)器作為通用波形發(fā)生器和接收器是切實可行的,它可以支持各種工作頻率,然后在實際運行或最終的LO實現(xiàn)中選擇特定的頻段。

對于工作頻帶在收發(fā)器瞬時帶寬內的相控陣系統(tǒng),外部LO可以是單一頻率,在這種情況下,使用外部LO結構來構建相控陣是一個非常實用的選擇。在評估系統(tǒng)相位噪聲時,可以選擇一個噪聲遠遠小于LO的參考頻率信號。如果將一個公共LO分布到多個收發(fā)器,當系統(tǒng)中收發(fā)器數(shù)量增加時,來自IC的噪聲貢獻將降低,直到系統(tǒng)噪聲主要來自于外部LO。該結論簡化了系統(tǒng)工程噪聲分析。由于噪聲主要由公共LO控制,工程工作可以集中在中央LO設計的性能/價格權衡上。

總結

現(xiàn)在有一種方法是利用外部LO來預測ADRV9009收發(fā)器相位噪聲。該方法允許利用DAC輸出頻率的函數(shù)方程來跟蹤參考振蕩器、LO源和收發(fā)器的貢獻。測量結果與預測結果非常吻合,表明該方法也可用于分析使用其他參考源是收發(fā)器的性能。這種方法也很普遍,可以用于任何波形發(fā)生器的設計中。

在努力創(chuàng)建低相位噪聲LO源時,使用外部LO測得的相位噪聲性能有明顯的優(yōu)勢。我們的目的是在評估架構選項時為系統(tǒng)設計人員提供一系列選項。對于使用收發(fā)器外部LO輸入的低相位噪聲應用中,該描述為在各種條件下評估系統(tǒng)級相位噪聲奠定了基礎。

在評估系統(tǒng)相位噪聲時,可以選擇噪聲貢獻遠遠小于LO的參考頻率源。如果將一個公共LO分布到多個收發(fā)器,當系統(tǒng)中收發(fā)器數(shù)量增加時,來自IC的噪聲貢獻將降低,直到系統(tǒng)噪聲主要來自于外部LO。該結論簡化了系統(tǒng)工程噪聲分析。由于噪聲主要由公共LO控制,工程工作可以集中在中央LO設計的性能/價格權衡上。

在努力創(chuàng)建低相位噪聲LO源時,使用外部LO測得的相位噪聲性能有明顯的優(yōu)勢。我們的目的是在評估架構選項時為系統(tǒng)設計人員提供一系列選項。對于使用收發(fā)器外部LO輸入的低相位噪聲應用中,該描述為在各種條件下評估系統(tǒng)級相位噪聲奠定了基礎。

ADRV9009

雙發(fā)射器

雙接收器

雙輸入共享觀察接收器

最大接收器帶寬:200 MHz

最大可調諧發(fā)射器合成帶寬:450 MHz

最大觀察接收器帶寬:450 MHz

全集成的小數(shù) N 射頻合成器

全集成的時鐘合成器

適用于射頻 LO 和基帶時鐘的多芯片相位同步

JESD204B 數(shù)據(jù)路徑接口

調諧范圍:75 MHz 至 6000 MHz

責任編輯:lq

-

集成電路

+關注

關注

5415文章

11849瀏覽量

366023 -

收發(fā)器

+關注

關注

10文章

3549瀏覽量

107015 -

射頻

+關注

關注

106文章

5701瀏覽量

169290

原文標題:當收發(fā)器遇上外部本振,更強的射頻性能get√

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

中國集成電路大全 接口集成電路

法動科技EMOptimizer解決模擬/射頻集成電路設計難題

高度集成的射頻集成電路(RFIC)的相位噪聲性能

高度集成的射頻集成電路(RFIC)的相位噪聲性能

評論