一種新的轉換器接口的使用率正在穩(wěn)步上升,并且有望成為未來轉換器的協(xié)議標準。這種新接口JESD204誕生于幾年前,其作為轉換器接口經過幾次版本更新后越來越受矚目,效率也更高。

隨著轉換器分辨率和速度的提高,對于效率更高的接口的需求也隨之增長。JESD204接口可提供這種高效率,較之其前代互補金屬氧化物半導體(CMOS)和低壓差分信號(LVDS)產品在速度、尺寸和成本方面更有優(yōu)勢。采用JESD204的設計擁有更快的接口帶來的好處,能與轉換器更快的采樣速率同步。此外,引腳數(shù)的減少導致封裝尺寸更小,走線布線數(shù)更少,從而極大地簡化了電路板設計,降低了整體系統(tǒng)成本。該標準可以方便地調整,從而滿足未來需求,這從它已經歷的兩個版本的變化中即可看出。自從2006年發(fā)布以來,JESD204標準經過兩次更新,目前版本為B。由于該標準已為更多的轉換器供應商、用戶以及FPGA制造商所采納,它被細分并增加了新特性,提高了效率和實施的便利性。此標準既適用于模數(shù)轉換器(ADC)也適用于數(shù)模轉換器(DAC),初步打算作為FPGA的通用接口(也可能用于ASIC)。

JESD204——它是什么?

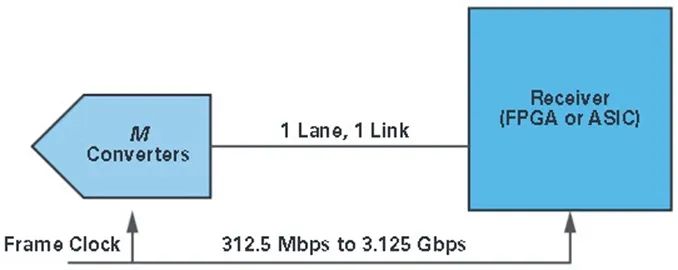

2006年4月,JESD204最初版本發(fā)布。該版本描述了轉換器和接收器(通常是FPGA或ASIC)之間數(shù)Gb的串行數(shù)據鏈路。在 JESD204的最初版本中,串行數(shù)據鏈路被定義為一個或多個轉換器和接收器之間的單串行通道。圖1給出了圖形說明。圖中的通道代表 M 轉換器和接收器之間的物理接口,該接口由采用電流模式邏輯(CML)驅動器和接收器的差分對組成。所示鏈路是轉換器和接收器之間的串行數(shù)據鏈路。幀時鐘同時路由至轉換器和接收器,并為器件間的JESD204鏈路提供時鐘。

圖1. JESD204最初標準。

通道數(shù)據速率定義為312.5 Mbps與3.125 Gbps之間,源阻抗與負載阻抗定義為100 Ω ±20%。差分電平定義為標稱800 mV峰峰 值、共模電平范圍從0.72 V至1.23 V。該鏈路利用8b/10b編碼,采用嵌入式時鐘,這樣便無需路由額外的時鐘線路,也無需考慮相關的高數(shù)據速率下傳輸?shù)臄?shù)據與額外的時鐘信號對齊的復雜性。當JESD204標準開始越來越受歡迎時,人們開始意識到該標準需要修訂以支持多個轉換器下的多路、對齊的串行通道,以滿足轉換器日益增長的速度和分辨率。

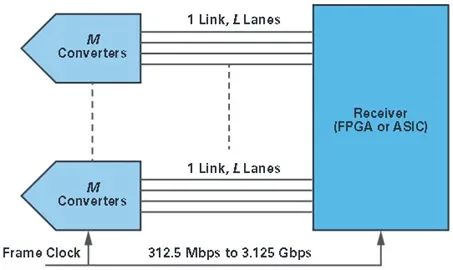

這種認識促成了JESD204第一個修訂版的發(fā)布,即JESD204A。此修訂版增加了支持多個轉換器下的多路對齊串行通道的能力。該版本所支持的通道數(shù)據速率依然為312.5 Mbps至3.125 Gbps,另外還保留了幀時鐘和電氣接口規(guī)范。增加了對多路對齊串行通道的支持,可讓高采樣速率和高分辨率的轉換器達到3.125 Gbps的最高支持數(shù)據速率。圖2以圖形表示JESD204A版本中增加的功能,即支持多通道。

圖2. 第一版——JESD204A。

雖然最初的JESD204標準和修訂后的JESD204A標準在性能上都比老的接口標準要高,它們依然缺少一個關鍵因素。這一缺少的因素就是鏈路上串行數(shù)據的確定延遲。對于轉換器,當接收到信號時,若要正確重建模擬域采樣信號,則關鍵是了解采樣信號和其數(shù)字表示之間的時序關系(雖然這種情況是針對ADC而言,但DAC的情況類似)。該時序關系受轉換器的延遲影響,對于ADC,它定義為輸入信號采樣邊沿的時刻直至轉換器輸出數(shù)字這段時間內的時鐘周期數(shù)。類似地,對于DAC,延遲定義為數(shù)字信號輸入DAC的時刻直至模擬輸出開始轉變這段時間內的 時鐘周期數(shù)。JESD204及JESD204A標準中沒有定義可確定性設置轉換器延遲和串行數(shù)字輸入/輸出的功能。另外,轉換器的速度和分辨率也不斷提升。這些因素導致了該標準的第二個版本——JESD204B。

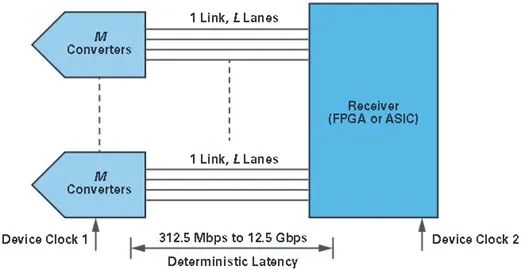

2011年7月,第二版本標準發(fā)布,稱為JESD204B,即當前版本。修訂后的標準中,其中一個重要方面就是加入了實現(xiàn)確定延遲的條款。此外,支持的數(shù)據速率也提升到12.5 Gbps,并劃分器件的不同速度等級。此修訂版標準使用器件時鐘作為主要時鐘源,而不是像之前版本那樣以幀時鐘作為主時鐘源。圖3表示JESD204B版本中的新增功能。

圖3. 第二個(當前)修訂版——JESD204B。

在之前的JESD204標準的兩個版本中,沒有確保通過接口的確定延遲相關的條款。JESD204B修訂版糾正了這個問題。通過提供一種機制,確保兩個上電周期之間以及鏈路重新同步期間,延遲是可重現(xiàn)和確定性的。其工作機制之一是:在定義明確的時刻使用SYNC~輸入信號,同時初始化所有通道中轉換器最初的通道對齊序列。另一種機制是使用SYSREF信號——一種JESD204B定義的新信號。SYSREF信號作為主時序參考,通過每個發(fā)射器和接收器的器件時鐘以及本地多幀時鐘對齊所有內部分頻器。這有助于確保通過系統(tǒng)的確定延遲。JESD204B規(guī)范定義了三種器件子類:子類0——不支持確定性延遲;子類1——使用SYSREF的確定性延遲;子類2——使用SYNC~的確定性延遲。子類0可與JESD204A鏈路做簡單對比。子類1最初針對工作在500MSPS或以上的轉換器,而子類2最初針對工作在500MSPS以下的轉換器。

除了確定延遲,JESD204B支持的通道數(shù)據速率上升到12.5 Gbps,并將器件劃分為三個不同的速度等級:所有三個速度等級的源阻抗和負載阻抗相同,均定義為100 Ω ±20%。第一速度等級與JESD204和JESD204A標準定義的通道數(shù)據速率相同,即通道數(shù)據電氣接口最高為3.125 Gbps。JESD204B的第二速度等級定義了通道數(shù)據速率最高為6.375 Gbps的電氣接口。該速度等級將第一速度等級的最低差分電平從500 mV峰峰值降為400 mV峰峰值。JESD204B的第三速度等級定義了通道數(shù)據速率最高為12.5 Gbps 的電氣接口。該速度等級電氣接口要求的最低差分電平降低至360 mV峰峰值。隨著不同速度等級的通道數(shù)據速率的上升,通過降低所需驅動器的壓擺率,使得所需最低差分電平也隨之降低,以便物理實施更為簡便。

為提供更多的靈活性,JESD204B版本采用器件時鐘而非幀時鐘。在之前的JESD204和JESD204A版本中,幀時鐘是JESD204系統(tǒng)的絕對時間參照。幀時鐘和轉換器采樣時鐘通常是相同的。這樣就沒有足夠的靈活性,而且要將此同樣的信號路由給多個器件,并考慮不同路由路徑之間的偏斜時,就會無謂增加系統(tǒng)設計的復雜性。JESD204B中,采用器件時鐘作為JESD204系統(tǒng)每個元件的時間參照。每個轉換器和接收器都獲得時鐘發(fā)生器電路產生的器件時鐘,該發(fā)生器電路負責從同一個源產生所有器件時鐘。這使得系統(tǒng)設計更加靈活,但是需要為給定器件指定幀時鐘和器件時鐘之間的關系。

JESD204——為什么我們要重視它?

就像幾年前LVDS開始取代CMOS成為轉換器數(shù)字接口技術的首選,JESD204有望在未來數(shù)年內以類似的方式發(fā)展。雖然CMOS技術目前還在使用中,但已基本被LVDS所取代。轉換器的速度和分辨率以及對更低功耗的要求最終使得CMOS和LVDS將不再適合轉換器。隨著CMOS輸出的數(shù)據速率提高,瞬態(tài)電流也會增大,導致更高的功耗。雖然LVDS的電流和功耗依然相對較為平坦,但接口可支持的最高速度受到了限制。

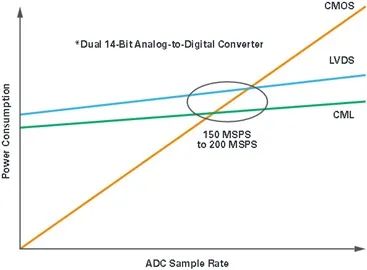

這是由于驅動器架構以及眾多數(shù)據線路都必須全部與某個數(shù)據時鐘同步所導致的。圖4顯示一個雙通道14位ADC的CMOS、LVDS和CML輸出的不同功耗要求。

圖4. CMOS、LVDS和CML驅動器功耗比較。

在大約150 MSP至200 MSPS和14位分辨率時,就功耗而言,CML輸出驅動器的效率開始占優(yōu)。CML的優(yōu)點是:因為數(shù)據的串行化,所以對于給定的分辨率,它需要的輸出對數(shù)少于LVDS和CMOS驅動器。JESD204B接口規(guī)范所說明的CML驅動器還有一個額外的優(yōu)勢,因為當采樣速率提高并提升輸出線路速率時,該規(guī)范要求降低峰峰值電壓水平。

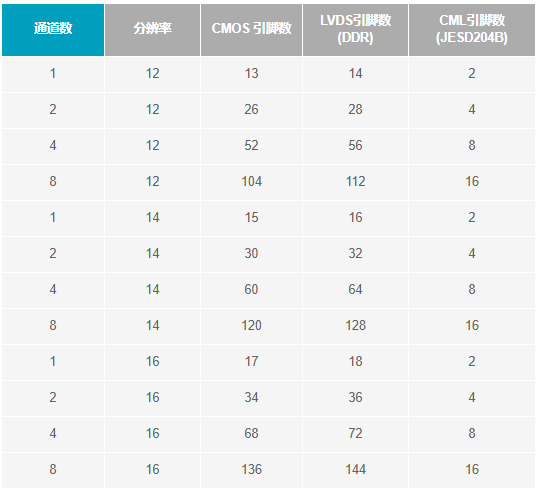

同樣,針對給定的轉換器分辨率和采樣率,所需的引腳數(shù)目也大為減少。表1顯示采用200 MSPS轉換器的三種不同接口各自的引腳數(shù)目,轉換器具有各種通道數(shù)和位分辨率。在CMOS和LVDS輸出中,假定時鐘對于各個通道數(shù)據同步,使用CML輸出時,JESD204B數(shù)據傳輸?shù)淖畲髷?shù)據速率為4.0 Gbps。從該表中可以發(fā)現(xiàn),使用CML驅動器的JESD204B優(yōu)勢十分明顯,引腳數(shù)大為減少。

表1. 引腳數(shù)比較——200 MSPS ADC

業(yè)內領先的數(shù)據轉換器供應商ADI預見到了推動轉換器數(shù)字接口向JESD204(由JEDEC定義)發(fā)展的趨勢。ADI自從初版JESD204規(guī)范發(fā)布之時起即參與標準的定義。迄今為止,ADI公司已發(fā)布多款輸出兼容JESD204和JESD204A的轉換器,目前正在開發(fā)輸出兼容JESD204B的產品。AD9639是一款四通道、12位、170 MSPS/210 MSPS ADC,集成JESD204接口。AD9644和AD9641是14位、80 MSPS/ 155 MSPS、雙通道/單通道ADC,集成JESD204A接口。DAC這方面,最近發(fā)布的AD9128是一款雙通道、16位、1.25 GSPS DAC,集成JESD204A接口。

隨著轉換器速度和分辨率的提高,對于效率更高的數(shù)字接口的需求也隨之增長。隨著JESD204串行數(shù)據接口的發(fā)明,業(yè)界開始意識到了這點。接口規(guī)范依然在不斷發(fā)展中,以提供更優(yōu)秀、更快速的方法將數(shù)據在轉換器和FPGA(或ASIC)之間傳輸。接口經過兩個版本的改進和實施,以適應對更高速度和分辨率轉換器不斷增長的需求。展望轉換器數(shù)字接口的發(fā)展趨勢,顯然JESD204有望成為數(shù)字接口至轉換器的業(yè)界標準。每個修訂版都滿足了對于改進其實施的要求,并允許標準演進以適應轉換器技術的改變及由此帶來的新需求。隨著系統(tǒng)設計越來越復雜,以及對轉換器性能要求的提高,JESD204標準應該可以進一步調整和演進,滿足新設計的需要。

責任編輯:lq

-

FPGA

+關注

關注

1642文章

21918瀏覽量

611923 -

轉換器

+關注

關注

27文章

8885瀏覽量

150120 -

接收器

+關注

關注

14文章

2533瀏覽量

73082

原文標題:小科普丨什么是JESD204標準,為什么我們要重視它?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

LTC6953具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9680 JESD204B接口的不穩(wěn)定會導致較大的電流波動,怎么解決?

使用jesd204b IP核時,無法完成綜合,找不到jesd204_0.v

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

DAC38J82在沒有jesd輸入的情況下,能單獨NCO輸出嗎?

調試ADS52J90板卡JESD204B接口遇到的問題求解

使用JESD204B接口,線速率怎么計算?

使用JESD204B如何對數(shù)據進行組幀?

ADC16DX370 JESD204B串行鏈路的均衡優(yōu)化

從JESD204B升級到JESD204C時的系統(tǒng)設計注意事項

TI AFE8092 AFE8030 JESD204配置及調試手冊- Part A

JESD204——它是什么?

JESD204——它是什么?

評論