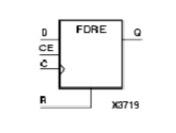

1、源語---FDRE

FDRE代表一個單D型觸發器,含的有五個信號分別為: 數據(data,D)、時鐘使能(Clock enable,CE)、時鐘(Clock)、同步復位(synchronous reset,R)、數據輸出(dataout,Q)。當輸入的同步復位信號為高時,否決(override)所有輸入,并在時鐘的上升沿將輸出Q為低信號。在時鐘的上升沿數據被加載進入D觸發器的輸入。

FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), // 同步時鐘 .D (data_sync0), //異步數據輸入 .Q (data_sync1), //同步數據輸出 .CE (1'b1), //時鐘使能信號 .R (1'b0) //復位信號輸入,高電平有效 );

由于數據可能與時鐘存在著不同步的情況,尤其是在對同步精度要求高的場合,一般還是用多次FDRE源語使得數據、控制信號等同步,例如在一個三態網數據同步模塊中使用了四個D觸發器進行數據同步:

`timescale 1ps / 1ps (* dont_touch = "yes" *) module tri_mode_ethernet_mac_0_sync_block #( parameter INITIALISE = 1'b0, parameter DEPTH = 5 ) ( input clk, // clock to be sync'ed to input data_in, // Data to be 'synced' output data_out // synced data ); // Internal Signals wire data_sync0; wire data_sync1; wire data_sync2; wire data_sync3; wire data_sync4; (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg0 ( .C (clk), .D (data_in), .Q (data_sync0), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg1 ( .C (clk), .D (data_sync0), .Q (data_sync1), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg2 ( .C (clk), .D (data_sync1), .Q (data_sync2), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg3 ( .C (clk), .D (data_sync2), .Q (data_sync3), .CE (1'b1), .R (1'b0) ); (* ASYNC_REG = "TRUE", SHREG_EXTRACT = "NO" *) FDRE #( .INIT (INITIALISE[0]) ) data_sync_reg4 ( .C (clk), .D (data_sync3), .Q (data_sync4), .CE (1'b1), .R (1'b0) ); assign data_out = data_sync4; endmodule

審核編輯 黃昊宇

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Xilinx

+關注

關注

73文章

2185瀏覽量

125293 -

觸發器

+關注

關注

14文章

2039瀏覽量

62137

發布評論請先 登錄

相關推薦

熱點推薦

硬件描述語言(HDL)編碼技術:xilinx verilog語法技巧

xilinx verilog語法技巧 一 硬件描述語言(HDL)編碼技術讓您: ?描述數字邏輯電路中最常見的功能。 ?充分利用Xilinx?器件的架構特性。 1 Flip-Flops

實施可行性警告:時鐘驅動太多寄存器

/ host_addr_r_reg [3] {FDRE}據我所知,這是我將單個時鐘引腳連接到多個模塊的情況。但是從RTL的角度來看,會在每個內部添加額外的緩沖區來解決問題嗎?我假設Xilinx工具會在

發表于 10-26 15:00

altera的ip源語在哪里可以獲取?在官網找的話要怎么搜索,有知道的大神求告知一下!

1.由于每次通過ip調取不方便移植也麻煩,所以需要獲取源語進行例化。有知道的大神求告知,鏈接代碼均可,常用的ip,ram,fifo,pll這些

發表于 01-14 10:15

關于labview輸入越南語亂碼

請問有沒有大佬知道labview支不支持越南語語言啊,我開了unicode輸入越南語還是會亂碼,可以顯示出越南語但是輸入到具體結構里面就會亂碼。請問有大佬知道怎么解決嗎

發表于 09-27 15:57

通信行業最齊全的英語縮語手冊

通信行業最齊全的英語縮語手冊:通信英語縮語手冊通信英語縮語手冊A&EM Alarm & Event Management 告警與事件管理 A&VE Audio / Video Editor 音頻/視頻編輯器 A-A Analog

發表于 02-11 12:43

?43次下載

在Xilinx FPGA上單源SYCL C++實現運行的方法

在此Xilinx研究實驗室演示中,解釋了單源SYCL C ++示例以及生成在Xilinx FPGA上運行的硬件實現的方法。

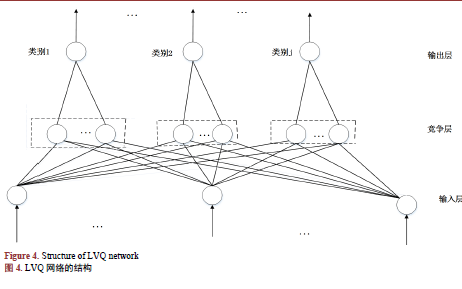

如何使用LVQ進行普米語語譜圖的識別說明

本文使用基于學習向量量化算法實現了對普米語語譜圖的識別。該算法首先通過傅立葉變換繪制出每條普米語語料的語譜圖;再次,提取每張語譜圖的圖像灰度

發表于 01-22 10:38

?7次下載

Xilinx源語-------FDRE

FDRE代表一個單D型觸發器,含的有五個信號分別為: 數據(data,D)、時鐘使能(Clock enable,CE)、時鐘(Clock)、同步復位(synchronous reset,R)、數據

發表于 01-25 07:27

?3次下載

xilinx源語中IDDR和ODDR介紹

1 IDDR ? 1.1 介紹 該設計元素是專用的輸入寄存器,旨在將外部雙數據速率(DDR)信號接收到Xilinx FPGA中。IDDR可用的模式可以在捕獲數據的時間和時鐘沿或在相同的時鐘沿向

Xilinx無源適配器的原理、特點及應用

在測試和驗證電子設備時,供電問題常常是一個關鍵的挑戰。作為一家領先的可編程邏輯器件制造商,為了幫助客戶解決供電問題,推出了一種創新的解決方案——Xilinx無源適配器。

Xilinx源語---FDRE

Xilinx源語---FDRE

評論