本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處(http://www.alinx.com)。

1. 實驗簡介

在HDMI測試實驗中講解了HDMI顯示原理和顯示方式,本實驗介紹如何使用FPGA實現字符顯示,通過這個實驗更加深入的了解HDMI的顯示方式。

2. 實驗原理

實驗通過字符轉換工具將字符轉換為16進制coe文件存放到單端口的ROM IP 核中,再從ROM 中把轉換后的數據讀取出來顯示到HDMI上。

3. 程序設計

字符顯示例程是在HDMI顯示的基礎上增加了一個osd_display的模塊,“osd_display”模塊是用來讀取存儲在Rom ip核里轉換后的字符信息,并在指定區域顯示。程序框圖如下圖所示:

osd_display模塊包含timing_gen_xy 模塊和osd_rom模塊。Osd_rom里存儲的字符數據,如果數據為1,OSD的區域顯示ROM中的前景紅色(顯示ALINX芯驛),如果數據是0,OSD的區域顯示數據為背景色(彩條)。

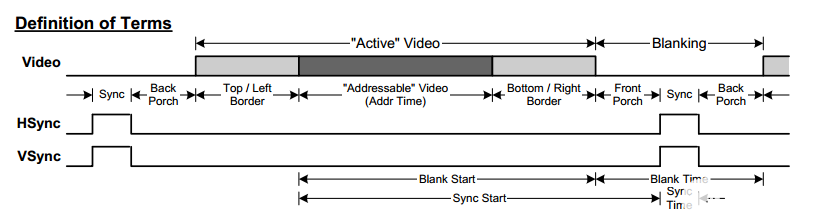

在“timing_gen_xy”模塊是根據HDMI時序標準定義了“x_cnt”和“y_cnt”兩個計數器并由這兩個計數器產生了HDMI顯示的“x”坐標和“y”坐標。程序中用“vs_edge”和“de_falling”分別表示場同步開始信號和數據有效結束信號。其原理如下圖所示:

| 信號名稱 | 方向 | 說明 |

| rst_n | in | 異步復位輸入,低復位 |

| clk | in | 外部時鐘輸入 |

| i_hs | in | 行同步信號 |

| i_vs | in | 場同步信號 |

| i_de | in | 數據有效信號 |

| i_data | in | color_bar數據 |

| o_hs | out | 輸出行同步信號 |

| o_vs | out | 輸出場同步信號 |

| o_de | out | 輸出數據有效信號 |

| o_data | out | 輸出數據 |

| x | out | 生成X坐標 |

| y | out | 生成Y坐標 |

timing_gen_xy模塊端口

下面介紹如何存儲文字信息的ROMIP,首先需要生成能夠被Pango FPGA識別的.dat文件。

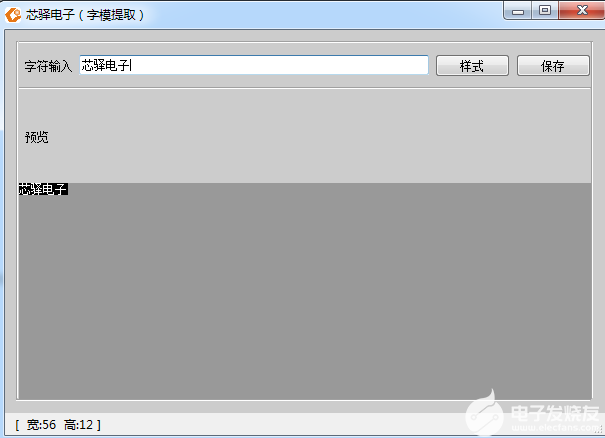

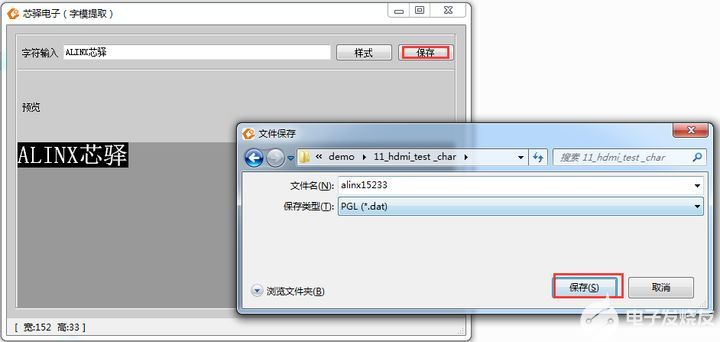

1)在軟件工具及驅動文件夾下找到“FPGA字模提取”工具。

2)雙擊.exe文件打開工具

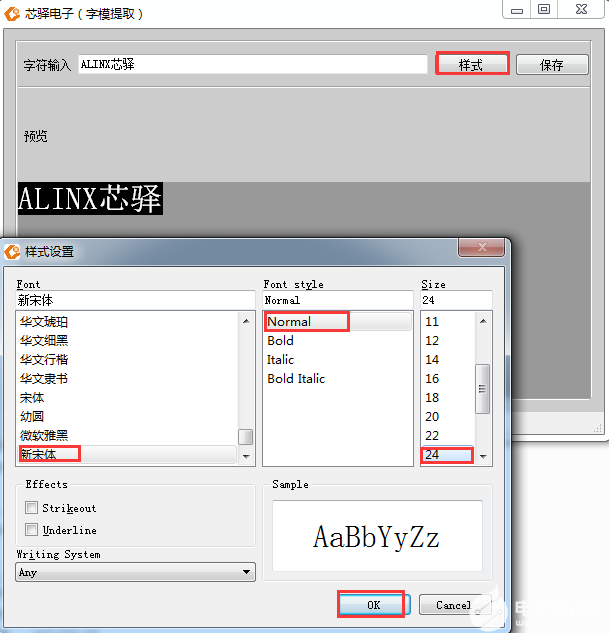

3)在提取工具的“字符輸入”框中輸入需要顯示的字符,字體和字符高度可以自定義選擇。設置完成后點擊“轉換”按鈕,在界面左下角可以看到轉換后的字符點陣大小,點陣的寬和高在程序中是需要用到的

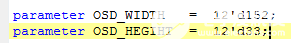

點陣的寬和高這里位152x33需要跟osd_display程序中定義的一致:

4)點擊“保存”按鈕,將文件保存到本例程源文件目錄下,需要注意的是在保存類型下應該選擇PGL(*.dat),點擊“保存”按鈕即可。

轉換后的字符已經成了8bit的數值文件,一個字節代表8個時鐘的像素,所以在從Rom IP核中讀取dat文件的值,需要判斷每一位的值,如果值為1,顯示紅色前景色,否則顯示背景色:

| always@(posedge pclk)begin if(region_active_d0 == 1'b1) if(q[osd_x[2:0]] == 1'b1) v_data <= 24'hff0000; else v_data <= pos_data; else v_data <= pos_data;end |

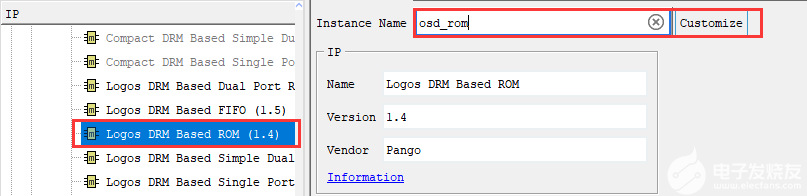

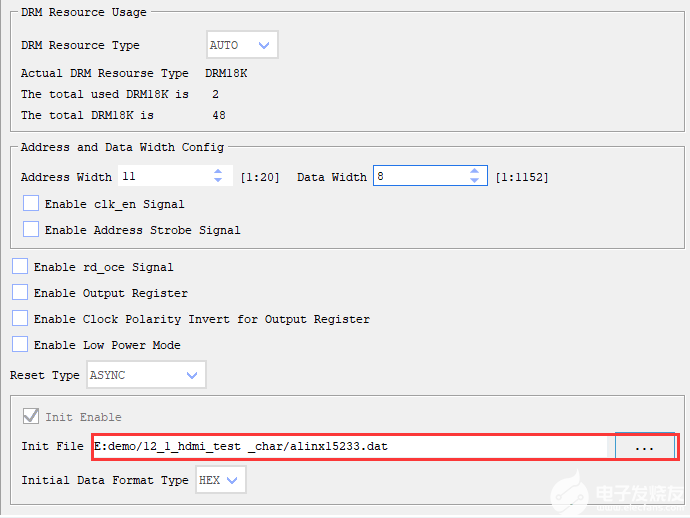

5)調用單端口Rom IP核的過程和調用其他IP 核一樣,打開菜單下的“IP Compiler”, "并按如下進行設置:

在彈出的界面中地址位寬、數據位寬、dat文件及類型進行設置,設置完成后按Generate即可生成osd_rom IP:

Rom IP核在“osd_display”模塊中例化如下:

| osd_rom osd_rom_m0( .address(osd_ram_addr[15:3]), .clock(pclk), .q(q)); |

| 信號名稱 | 方向 | 說明 |

| rst_n | in | 異步復位輸入,低復位 |

| pclk | in | 外部時鐘輸入 |

| i_hs | in | 行同步信號 |

| i_vs | in | 場同步信號 |

| i_de | in | 數據有效信號 |

| i_data | in | color_bar數據 |

| o_hs | out | 輸出行同步信號 |

| o_vs | out | 輸出場同步信號 |

| o_de | out | 輸出數據有效信號 |

| o_data | out | 輸出數據 |

osd_display模塊端口

4.試驗現象

連接好開發板和顯示器,連接方式參考《HDMI測試實驗》教程,需要注意,開發板的各個連接器不要帶電熱插拔,下載好試驗程序,可以看到顯示器顯示以彩條為背景的字符。開發板做為HDMI輸出設備,只能通過HDMI顯示設備來顯示,不要試圖通過筆記本電腦的HDMI接口來顯示,因為筆記本也是輸出設備。

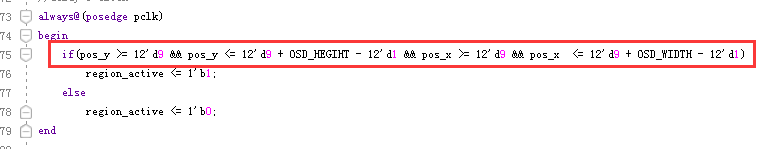

默認字符顯示的位置在X坐標和Y坐標都是9的地方顯示,另外用戶可以修改下面的pos_y和pos_x的判斷條件將字符顯示在顯示屏的任意位置:

-

FPGA

+關注

關注

1642文章

21918瀏覽量

611921 -

HDMI

+關注

關注

32文章

1804瀏覽量

154091 -

ROM

+關注

關注

4文章

577瀏覽量

86819 -

字符

+關注

關注

0文章

234瀏覽量

25422 -

紫光同創

+關注

關注

5文章

91瀏覽量

27815

發布評論請先 登錄

相關推薦

方正微電子亮相第十三屆儲能國際峰會暨展覽會

中科億海微亮相第十三屆中國電子信息博覽會

【紫光同創國產FPGA教程】【第十三章】字符顯示實驗

【紫光同創國產FPGA教程】【第十三章】字符顯示實驗

評論