視頻采集的主流實現(xiàn)方案有兩種:一是基于ASIC,該方案一般采用意法、AMD等公司的專用視頻處理芯片;二是基于DSP,主要采用TI、ADI等公司的DSP信號處理器。它們作為輔處理器,可在主CPU控制下進(jìn)行視頻信號的采集壓縮。隨著FPGA的發(fā)展,通過SOPC技術(shù)實現(xiàn)視頻采集已成為一種易于開發(fā)、設(shè)計靈活的方案。而這主要得益于IP復(fù)用技術(shù)的發(fā)展。在FPGA上構(gòu)建復(fù)雜嵌入式系統(tǒng)可利用既有的功能模塊及其驅(qū)動程序。該方案具有更大的集成度和靈活性,因而必將成為電子設(shè)計發(fā)展的一大趨勢。

本文介紹了采用Xilinx公司的Spartan-3 FPGA實現(xiàn)通用視頻采集系統(tǒng)的設(shè)計方案。該系統(tǒng)外接模擬PAL/NTAL制式的攝像頭,就能實時采集視頻信號并進(jìn)行MPEG-4格式壓縮編碼,碼流可通過USB接口傳給PC機,或通過以太網(wǎng)接口進(jìn)行網(wǎng)絡(luò)傳輸。本系統(tǒng)選用的是Spartan-3 FPGA系列的XC3S200芯片,該芯片有4320個邏輯單元(LC)、216Kbit BlockRAM、4個數(shù)字延遲鎖相環(huán)(DDL)、173個用戶I/O,而且邏輯密度高、I/O多、成本低。本設(shè)計主要涉及電路板級硬件設(shè)計、FPGA片級硬件系統(tǒng)設(shè)計和系統(tǒng)軟件設(shè)計。

1 板級硬件設(shè)計

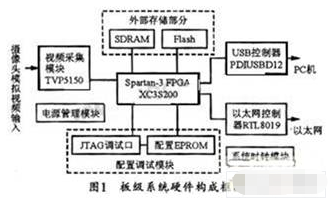

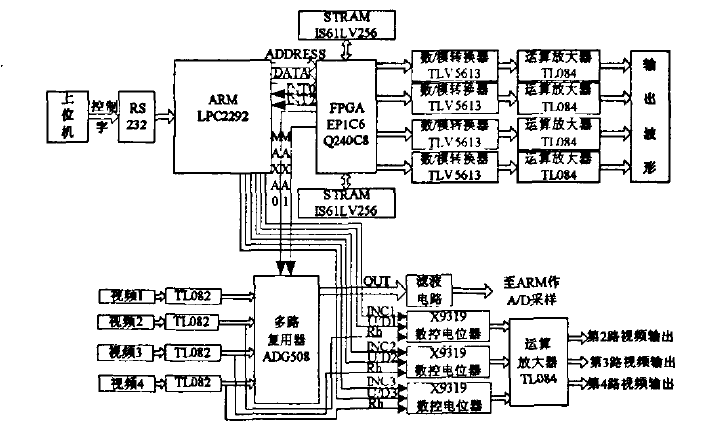

FPGA在電源和配置電路的支持下,即可構(gòu)成嵌入式系統(tǒng)的最小化系統(tǒng),并能實現(xiàn)片內(nèi)的所有功能。在此最小化系統(tǒng)上,就可以根據(jù)本設(shè)計的應(yīng)用需求,來擴(kuò)展外部存儲模塊、視頻采集模塊、USB接口模塊、以太網(wǎng)接口模塊等功能模塊電路,從而形成電路板級硬件平臺。該板級硬件平臺的結(jié)構(gòu)組成如圖1所示。

1.1 最小化系統(tǒng)

該FPGA是基于SRAM存儲結(jié)構(gòu)的器件。每次上電時可將配置數(shù)據(jù)從外部配置存儲器加載到內(nèi)部SRAM中,以使其構(gòu)建邏輯結(jié)構(gòu)從而實現(xiàn)邏輯功能。配置調(diào)試模塊主要包括配置存儲器、配置模式跳線開關(guān)和JTAG調(diào)試端口,其中JTAG調(diào)試端口是系統(tǒng)開發(fā)階段PC機與FPGA的通信接口,可用于從PC機下載FPGA配置數(shù)據(jù),并在程序調(diào)試階段作為聯(lián)機接口。本設(shè)計采用Xilinx公司Platform. Flash系列配置存儲器XCF02S,并采用14針JTAG接口。模式跳線開關(guān)可決定FPGA是由JTAG還是由配置存儲器來進(jìn)行配置。系統(tǒng)時鐘模塊可對XC3S200提供50 MHz高頻時鐘信號,它采用高穩(wěn)定性的石英晶體振蕩器分立元件。電源管理模塊采用DC/DC變換器來為系統(tǒng)各元件提供需要的各種電壓電流。以上部分與FPGA芯片相連即可構(gòu)成嵌入式系統(tǒng)工作的最小化系統(tǒng)。

1.2 外部存儲擴(kuò)展

由于XC3S200的片內(nèi)存儲容量有限且掉電即失,因此必須配置大容量的外部儲存器。本設(shè)計擴(kuò)展了4MByte的flash和32MByte的SDRAM (包括一片AMD公司的AM29LV320DT90EC型Flash和兩片HYNIX公司的HY57V281620HCT-PI型SDRAM)。其中Flash在系統(tǒng)中用于存放程序代碼、常量表以及一些在系統(tǒng)掉電后需要保存的用戶數(shù)據(jù)。而SDRAM掉電數(shù)據(jù)即失,但其存取速度大大高于Flash且可讀可寫,因而在系統(tǒng)中用作程序的運行空間、臨時數(shù)據(jù)及堆棧區(qū)等。

1.3 視頻采集模塊

TVP5150是TI公司推出的一款超低功耗的高性能混合信號視頻解碼芯片,可自動識別NTSC/PAL/SECAM制式的模擬信號,并將其按照YCbCr4:2:2的格式轉(zhuǎn)化成數(shù)字信號,然后以8位內(nèi)嵌同步信號的ITU-RBT.656格式輸出。TVP5150具有價格低、體積小、操作簡便等特點。FPGA對TVP5150芯片的操作是通過I2C總線實現(xiàn)的,數(shù)據(jù)傳輸連接方式采用最簡單的ITU-RBT.656方式。

1.4 USB接口模塊

USB接口模塊選用PHILIPS公司的高性能USB接口芯片PDIUSBD12。該芯片完全符合USB1.1規(guī)范,可支持DMA傳輸,并可通過高速8位并行接口和FPGA進(jìn)行通信,其最高并行接口速率可達(dá)到2 MB/s。

1.5 以太網(wǎng)接口模塊

該模塊采用Realtek公司生產(chǎn)的高度集成的以太網(wǎng)控制器RTL8019AS。RTL8019AS支持IEEE802.3標(biāo)準(zhǔn)和8位或16位數(shù)據(jù)總線。其內(nèi)置16KB的SRAM可用于收發(fā)緩沖。在全雙工模式時,其收發(fā)可同時達(dá)到10Mbps。RTL8019AS可支持10Base5、10Base2、10BaseT,并能自動檢測所連接的介質(zhì)。本設(shè)計采用RTL8019AS跳線接口模式,并通過16位數(shù)據(jù)總線連接FPGA。

2 片級硬件系統(tǒng)設(shè)計

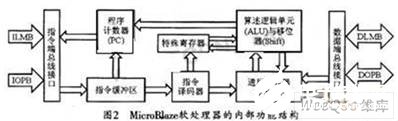

在Spartan-3上構(gòu)建嵌入式系統(tǒng)的基礎(chǔ)是MicroBlaze IP核。這是一種用硬件描述語言在FPGA內(nèi)部實現(xiàn)的32位微處理器,采用RISC指令集和Ha rvard體系結(jié)構(gòu)。可根據(jù)不同的外設(shè)和存儲器配置進(jìn)行定制,并可以針對應(yīng)用來調(diào)整處理器系統(tǒng)架構(gòu)。在Spartan-3系列芯片上進(jìn)行該配置大約占用500 Slices。該IP核具有32個32位通用寄存器和2個專用寄存器。其32位寬的指令系統(tǒng)能支持3個操作數(shù)和兩種尋址方式,而其獨立的32位指令和數(shù)據(jù)總線則可與IBM的OPB總線完全兼容。通過模塊中的LMB總線,其32位指令和數(shù)據(jù)可直接與片內(nèi)的塊存儲器相連。此外,該IP核還具有高速的指令和數(shù)據(jù)緩存(Cache)、三級流水線結(jié)構(gòu)、32位地址總線、硬件調(diào)試邏輯、8個輸入和8個輸出的快速鏈路(FSL)接口等。MicroBlaze軟處理器的內(nèi)部功能結(jié)構(gòu)如圖2所示。

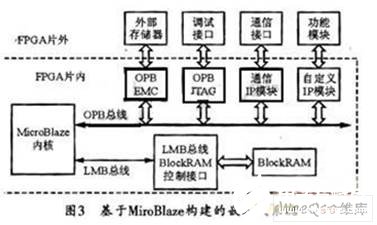

在FPGA上設(shè)計嵌入式系統(tǒng)時,可在最低層硬件資源上開發(fā)片內(nèi)外設(shè)IP核,或利用已開發(fā)的IP核搭建嵌入式系統(tǒng)的硬件部分,然后開發(fā)IP核的設(shè)備驅(qū)動、應(yīng)用接口(API)和應(yīng)用層(算法)。通過標(biāo)準(zhǔn)總線接口將局部存儲器總線(LMB)和片內(nèi)外設(shè)總線(OPB)連接到片內(nèi)外設(shè)IP核,MicroBlaze處理器就可以和各種外設(shè)IP核及片內(nèi)BlockRAM相連。該開發(fā)工具提供的IP核均有相應(yīng)的設(shè)備驅(qū)動和應(yīng)用接口,使用者只需利用相應(yīng)的函數(shù)庫來編寫自己的應(yīng)用軟件和算法程序即可。對于用戶自己開發(fā)的IP核,則需要自己編寫相應(yīng)的驅(qū)動和接口函數(shù)。利用MicroBlaze處理器構(gòu)建的基本嵌入式系統(tǒng)如圖3所示。

在FPGA上實現(xiàn)嵌入式系統(tǒng),主要是構(gòu)建片內(nèi)MicroBlaze處理器,并為處理器添加片內(nèi)外設(shè)以實現(xiàn)硬件模塊功能,同時應(yīng)添加片內(nèi)外設(shè)與芯片外部引腳的連接。在開發(fā)片內(nèi)外設(shè)的同時,應(yīng)開發(fā)外設(shè)功能的底層驅(qū)動程序,然后在MicroBlaze處理器上實現(xiàn)系統(tǒng)應(yīng)用程序。這是個軟件與硬件協(xié)同開發(fā)的過程。以MicroBlaze處理器為核心的系統(tǒng)開發(fā)可使用Xilinx公司提供的EDK(Embedded Development Kit)。該EDK提供有一個集成開發(fā)環(huán)境XPS(Xilinx Platform. Studio),它同時集成了硬件平臺產(chǎn)生器、軟件平臺產(chǎn)生器、仿真模型生成器、軟件編譯器和軟件調(diào)試器等工具。在此環(huán)境下調(diào)用各種工具即可完成軟硬件協(xié)同開發(fā)的整個流程。EDK提供有多種與MicroBlaze處理器相關(guān)的功能IP核,其中包括OPB 10/100M以太網(wǎng)控制器、PLB/OPB SDRAM控制器、UART中斷控制器、定時器及其它外圍設(shè)備接口等資源。使用EDK中的系統(tǒng)硬件平臺設(shè)計向?qū)В˙ase System Builder Wizard)可進(jìn)行MicroBlaze處理器的配置,而使用添加外圍設(shè)備向?qū)В↖mportPeripheral Wizard)則可調(diào)用既有IP核以生成片內(nèi)設(shè)備,并與處理器總線相連。

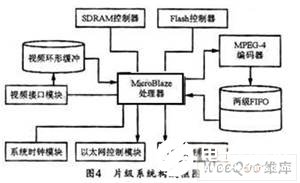

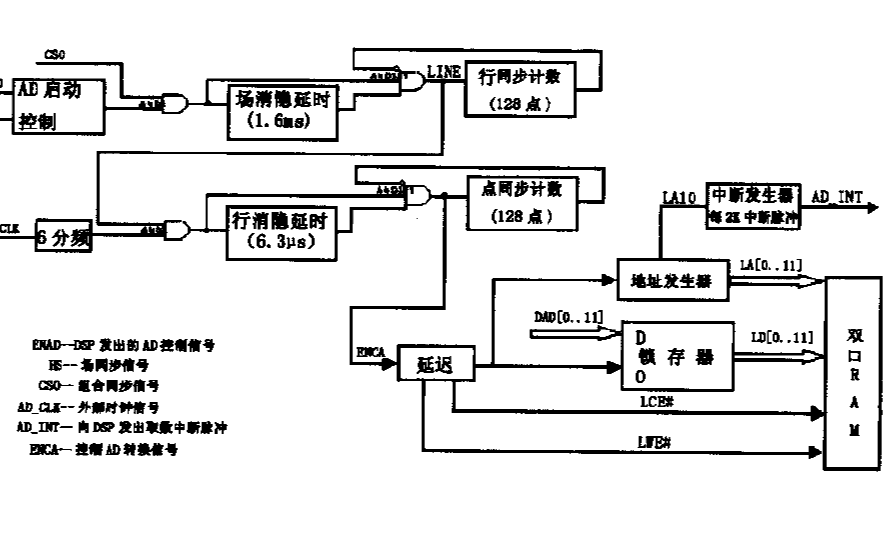

本系統(tǒng)的片內(nèi)主要功能模塊包括視頻接口模塊、環(huán)形緩沖區(qū)、碼流兩級FIFO緩沖區(qū)、MPEG-4編碼器、Flash控制器、SDRAM控制器、10/100M以太網(wǎng)控制模塊、USB控制模塊等。其中視頻接口模塊是MicroBlaze處理器與TVP5150的接口。MicroBlaze處理器對TVP5150的控制驅(qū)動程序可從TVP5150驅(qū)動程序模板移植而來,可用于實現(xiàn)TVP5150采集方式的配置,并將采集的視頻信號以4:2:0YUV格式存儲到環(huán)形緩沖區(qū)里。環(huán)形緩沖區(qū)是片內(nèi)與MicroBlaze處理器總線相連的SRAM存儲空間的一部分,其中數(shù)據(jù)隊列的首尾指針是由MicroBlaze處理器程序維護(hù)的。采用開發(fā)工具提供的FIFO模板可對其深度、位寬、讀寫時鐘、滿標(biāo)志等參數(shù)進(jìn)行設(shè)定,并將兩個FIFO相連以構(gòu)成兩級FIFO,然后將其入口與MPEG-4編碼器的輸出相連。FIFO的先一級與MicroBlaze處理器總線相連可支持DMA讀取。MPEG-4編碼器是Xilinx公司授權(quán)的MPEG-4 Simple Profile編碼器IP核,它接受環(huán)形緩沖區(qū)里未壓縮的4:2:0YUV格式視頻信號并可將其生成MPEG-4Simple Profile格式壓縮碼流。MPEG-4編碼器與MicroBlaze處理器總線和兩級FIFO輸入相連,可為EDK提供其驅(qū)動程序。Flash控制器、SDRAM控制器、10/100M以太網(wǎng)控制器的實現(xiàn)軟件在EDK中已提供,其與處理器總線的連接也在向?qū)Чぞ咧凶詣釉O(shè)定,其驅(qū)動程序就包含在其中。由于片外采用了高度集成的USB控制器,而片內(nèi)的USB控制模塊只是MicroBlaze處理器總線與引腳的直接相連,故其驅(qū)動程序只是參考PDIUSBD12的一般驅(qū)動程序在EDK軟件平臺上的移植。

本系統(tǒng)的片內(nèi)外設(shè)與MircoBlaze處理器的連接如圖4所示,其中箭頭表示視頻數(shù)據(jù)的流向。

3 系統(tǒng)軟件設(shè)計

系統(tǒng)中的MicroBlaze處理器對TVP515 0和PDIUSBD12的控制驅(qū)動程序可根據(jù)其通用驅(qū)動程序在EDK軟件平臺上移植生成。利用Xilinx公司提供的IP核可以搭建FPGA片內(nèi)硬件平臺,同時可獲得底層硬件驅(qū)動程序的支持,然后在此基礎(chǔ)上進(jìn)行系統(tǒng)應(yīng)用程序的開發(fā)。

外部模擬視頻信號經(jīng)TVP5150轉(zhuǎn)換為數(shù)字視頻信號后,即可進(jìn)入FPGA并通過視頻接口模塊直接排列到內(nèi)部環(huán)形緩沖區(qū)數(shù)據(jù)隊列的隊尾。

當(dāng)MircoBlaze處理器接收到MPEG-4編碼器可用中斷時,系統(tǒng)將檢測環(huán)形緩沖區(qū)是否為空。非空時,可將數(shù)據(jù)隊列的頭部數(shù)據(jù)取出送給MPEG-4編碼器,同時啟動編碼器編碼。

視頻信號經(jīng)過編碼器編成視頻原碼流后,即可進(jìn)入FPGA內(nèi)部二級FIFO緩存。當(dāng)FIFO先一級滿時向MircoBlaze處理器發(fā)出數(shù)據(jù)輸出中斷請求。

MircoBlaze處理器響應(yīng)來自FIFO的中斷后,可將FIFO先一級數(shù)據(jù)取出并以USB或以太網(wǎng)接口輸出,然后清空FIFO先一級。

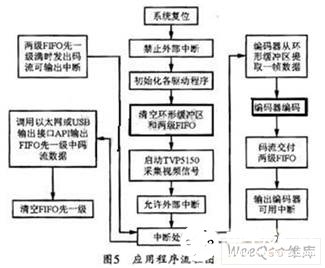

依據(jù)上面的工作過程,MircoBlaze處理器的應(yīng)用程序包括以下幾部分:

(1)系統(tǒng)復(fù)位初始化

即禁止外部中斷,初始化各驅(qū)動程序,清空環(huán)形緩沖區(qū)和兩級FIFO,檢測USB接口、以太網(wǎng)接口連接以決定用何種方式輸出,然后啟動對TVP5150的控制并進(jìn)行數(shù)據(jù)采集,最后啟用外部中斷。

(2)編碼器可用中斷服務(wù)

編碼器完成一幀數(shù)據(jù)編碼即可向MircoBlaze處理器發(fā)出中斷,然后由MircoBlaze處理器控制編碼器向環(huán)形緩沖區(qū)提取數(shù)據(jù),并在環(huán)形緩沖區(qū)耗盡時等待一定時間;

(3)碼流可輸出中斷服務(wù)

當(dāng)兩級FIFO先一級所準(zhǔn)備輸出的碼流滿時,可向MircoBlaze處理器發(fā)出中斷,然后在MircoBlaze處理器控制下,將該碼流交付給USB或以太網(wǎng)輸出接口API并由底層驅(qū)動輸出,最后再清空FIFO先一級。

圖5所示是其應(yīng)用程序流程圖。

4 結(jié)束語

本設(shè)計介紹了基于Spartan-3 FPGA實現(xiàn)通用視頻采集系統(tǒng)的實現(xiàn)方案。本系統(tǒng)的設(shè)計依賴于專用的設(shè)計軟件和IP模塊。由于采用了SOPC技術(shù),該系統(tǒng)可裁減、可擴(kuò)充、可升級,而多層次IP模塊的高度復(fù)用又使得本系統(tǒng)具有設(shè)計周期短,風(fēng)險投資小和設(shè)計成本低等優(yōu)勢。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

555文章

8142瀏覽量

355244 -

FPGA

+關(guān)注

關(guān)注

1643文章

21966瀏覽量

614144 -

芯片

+關(guān)注

關(guān)注

459文章

52192瀏覽量

436253

發(fā)布評論請先 登錄

基于FPGA和視頻解碼芯片的實時圖像采集系統(tǒng)設(shè)計

怎么在Xilinx Spartan-3 XC3S200 FPGA中使用鼠標(biāo)

如何使XC3S200 FPGA以理想的占空比輸出時鐘?

XC3S200配置出現(xiàn)問題

請問s3不支持AXI怎么辦?

采用FPGA實現(xiàn)多普勒測振計信號采集系統(tǒng)設(shè)計

如何采用Spartan-3 FPGA實現(xiàn)通用視頻采集系統(tǒng)的設(shè)計?

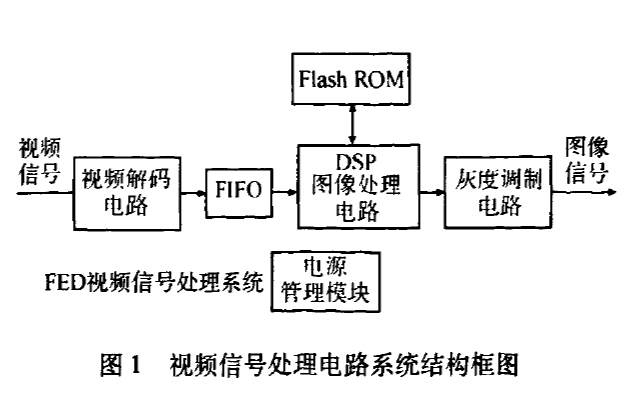

一種基于DSP與FPGA實現(xiàn)場發(fā)射平板顯示器視頻信號處理系統(tǒng)的方案

基于XC3S400和CY7C68013多路數(shù)據(jù)采集電路的設(shè)計

基于XC3S200的通用視頻采集系統(tǒng)的設(shè)計

基于FPGA和SAA7113芯片的視頻采集監(jiān)控方案

如何使用FPGA和ARM設(shè)計和實現(xiàn)多路視頻采集系統(tǒng)

使用FPGA控制實現(xiàn)圖像系統(tǒng)視頻圖像采集的設(shè)計資料說明

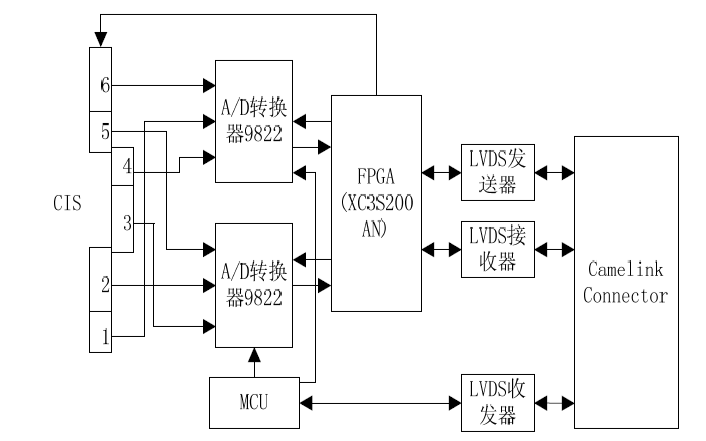

如何使用FPGA實現(xiàn)超長CIS圖像采集系統(tǒng)的設(shè)計

如何使用DSP和FPGA實現(xiàn)場發(fā)射平板顯示器視頻信號處理系統(tǒng)的方案說明

通過采用FPGA XC3S200芯片實現(xiàn)視頻采集系統(tǒng)的應(yīng)用方案

通過采用FPGA XC3S200芯片實現(xiàn)視頻采集系統(tǒng)的應(yīng)用方案

評論