作者:李陽;劉政林;湯加躍;鄒雪城

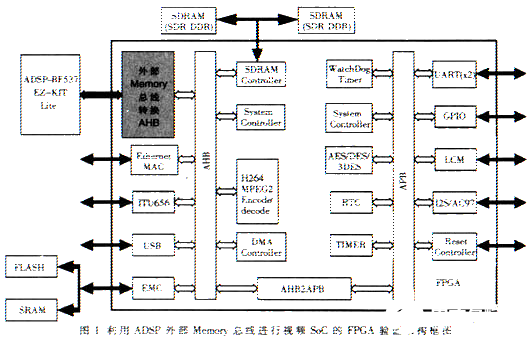

隨著硅片集成技術的高速發展,片上系統SoC(system-on-a-Chip)已經成為現代數字系統設計的必然趨勢。SoC和一般數字系統最主要的區別是前者在單一硅片內集成了獨立的嵌入式CPU,必要的存儲器控制器也要求集成到SoC芯片內,所以對SoC系統的軟硬件協同實時驗證便成為SoC設計的難點。基于IP的可重用設計方法已經成為數字系統設計工程師普遍采用的系統設計方法。于是,設計者采用第三方IP或自行設計的軟核或兩者的組合來搭建符合要求的系統。對于一個SoC系統,嵌入式CPU的選擇至關重要。第三方提供CPU的方式有軟核和固核,如果在設計過程中僅被授權采用第三方優化的固核(版圖級),則前端FPGA實時驗證問題自然凸現出來。解決的辦法是選擇相應CPU的驗證開發板或者采用其他處理器。本文介紹一種利用嵌入Blackfin處理器的ADSP-BF537作為處理器進行SoC的FPGA實時驗證的方案及其總線接口轉換模塊的設計。SoC系統驗證平臺結構框圖如圖1所示。

1 ADSP簡介

ADSP是ADI(Analog Device Inc.)公司推出的一系列高性能低功耗DSP芯片,而基于Blackfin處理器的ADSP-BF533一經推出便被很多國家的設計人員立即采用,后續系列產品ADSP-BF5xx也被更多的系統設計廠家應用到各自的產品中。正是因為ADSP-BF5xx系列芯片是以功能強大性能卓越的Blackfin處理器為內核而推出的高效DSP芯片,使得人們可以采用ADSP-BF5xx系列芯片作為處理器進行視頻SoC的FPGA實時驗證。Blackfin處理器集成了一個由ADI公司和Intel公司聯合開發的基于MSA(Micro Signal Architecture)的16/32位嵌入式處理器,支持32位RISC指令集,采用10級流水線,集成了兩個16位乘法加速器,內核主頻最高可以達到600MHz。

2 ADSP外部Momory總線介紹

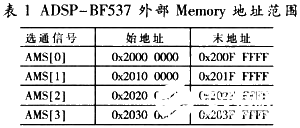

ADSP外部Memory總線可以進行同步或異步操作,前者是通過時鐘輸出端CLKOUT進行同步的。本文所采用的ADSP-BF537 Ez-kit Lite開發套件的外部Memory總線的可用地址僅為19位(ADDR[19:1]),并且采用AMS[3:0]選中相應的外部區域。ADSP-BF537的四個選通信號線對應的外部Memory地址范圍如表1所示。可以看出,直接利用ADSP外部Memory總線操作的地址空間只有4MB容量,顯然不能滿足SoC的選址需求,必須進行接口總線的轉換來提高尋址范圍。

ADSP-BF537外部Memory讀寫時序波形如圖2所示,其中的ARDY信號是由外設產生的。ADSP通過設置EBIU_AMBCTLx寄存器,允許傳輸過程中使用ARDY握手信號,用來增強系統運行的準確度。ARDY信號的有效電平是可以設置的。

EBIU_AMBCTLx寄存器還可以改變ADSP對外讀寫操作的時序,包括數據建立時間、讀寫通路時間以及數據保持時間。例如,圖2所示的寫操作建立時間、通路時間和保持時間分別是2個周期、2個周期和1個周期。如果使能ARDY信號,并設置為高電平有效,則在設定的讀寫時間內,ARDY為低電平表示外設不能寫入或者讀出數據,需要ADSP繼續保持相應的讀寫等待狀態,直到ARDY信號被拉為高電平;只有當ADSP檢測到ARDY為高電平時,才能將DATA數據作為有效數據。上述過程如圖2中的讀操作,ARDY信號被拉低了一個周期。

ADSP-BF537的外部Memory地址總線位寬是ADDR[19:1],這樣可以使ADSP靈活地對16/32位數據進行地址選址。例如,如果對連續地址進行16位數據的讀寫操作,ADDR[19:1]只需依次加1,而ADSP軟件開發工具中相應的內部變量數據類型定義為short即可;類似地,如果要讀寫的數據類型為int(32位)數據,則每次訪問外部地址時,ADSP會連續產生兩次讀寫操作,并且地址總線ADDR[19:1]是連續的。

3 AHB總線介紹

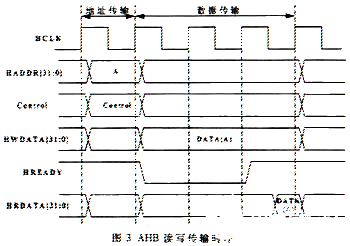

AHB(Advanced High-performance Bus)是AMBA總線中用途最為廣泛的一種高速總線,因其協議簡單、可綜合性強、支持主頻高、功耗低,已經被很多SoC芯片作為內部高速系統總線。大多數第三方IP廠商提供的功能模塊的接口都支持AMBA總線協議。AHB基本傳輸時序如圖3所示。

4消除信號的亞穩態現象

在本次視頻SoC的FPGA驗證方案中,采用ADSP的外部Memory總線,FPGA既可以利用同步時鐘輸出CLKOUT進行同步設計,也可以采用異步總線讀寫。如果不使用CLKOUT而采用異步設計,則在總線轉換接口模塊設計中,首先需要保證消除讀寫信號亞穩態現象。ADSP內核主頻可以達到600MHz,外部Memory總線的采樣時鐘(CLKOUT)動態調整范圍也很大,因此對異步輸入信號可以采用增加同步觸發器進行鎖存延時的方法來消除亞穩態。具體實現方法是在異步輸入信號的前端加2-3級同步觸發器。FPGA驗證證明:當CLKOUT頻率為50MHz,FPGA系統主頻為25MHz時,3級同步鎖存完全可以消除亞穩態,從而保證ADSP在外部Memory總線上正確進行數據傳輸。

5總線轉換狀態機設計

目前,大多數采用AMBA總線的SoC系統內部的總線位寬是32位,多數嵌入式CPU和第三方IP核總線位寬也均為32位,因為32位地址總線和數據總線已經可以滿足絕大多數SoC系統的存儲器映射寄存器的地址分配和數據交換以及外部SDRAM和FLASH的尋址需求。ADSP-BF537的外部Memory數據總線是16位,并且地址總線只有19位,因此必須通過增加必要的狀態來解決總線位寬的不匹配問題。

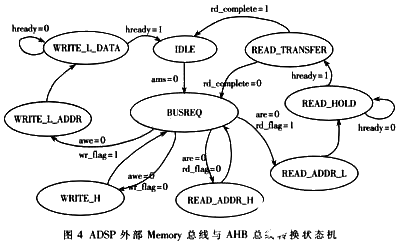

為了實現ADSP對外進行32位的地址操作和數據操作,可以利用Blackfin處理器分兩次進行讀寫操作。寫操作分兩次進行,第一次寫,先傳輸地址和數據的高16位,第二次寫才將32位的地址和數據信號傳輸到AHB總線上;進行讀操作時,需要AHB產生兩次讀動作,這樣才能使有效的32位數據被Blackfin處理器正確接收。第一次讀到有效的32位數據后傳輸高位,第二次讀到后傳輸低位,并且每次讀操作都需要Blackfin發出兩次讀動作,以便組合出AHB的32位地址。這樣就可以突破ADSP-BF537對外只能進行4MB空間存取的限制。以上描述過程的狀態機轉換圖如圖4所示。

利用ADSP作為SoC系統處理器進行SoC驗證時,ADSP進行的主要操作是讀寫系統內部各個功能模塊的Memory映射控制寄存器,并且通過SDRAM控制器對SoC系統的外部SDRAM進行數據交換操作。因此總線轉換狀態機分成讀傳輸和寫傳輸兩大部分。

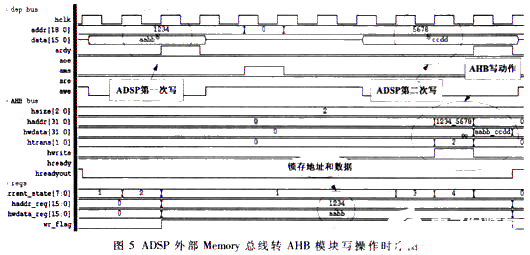

當ADSP需要進行外部Memory總線傳輸時,首先會把相應的ams信號拉低,這時總線轉換狀態機應該使AHB進入BUSREQ狀態,要求仲裁器釋放AHB總線給CPU(ADSP)。

對于一個寫操作,需定義一個wr_flag標志位來確定是否產生AHB寫動作。ams信號拉低后,經過可配置的寫建立時間后,寫控制信號awe被拉低,初始化的wr_flag為0,表明ADSP進行的是第一次寫操作。進入的WRITE_H狀態用來鎖存寫地址和寫數據的高16位,同時會把wr_flag置為1,但并不向AHB總線發出寫命令。一個周期后重新進入BUSREQ狀態,等待ADSP下一個寫命令。ADSP發出第二次寫命令后,狀態機檢測到awe=0和wr_flag=1后進入WRITE_L_ADDR狀態,表明需要向AHB發出寫命令,包括hwrite、haddr、htrans、hsize等AHB控制信號。haddr是兩次寫操作地址(16位)組合而成的32位地址,htrans=2和hsize=2,表明是非連續傳輸,傳輸數據位寬是32位。下一個周期,狀態進入WRITE_L_DATA,兩次寫操作數據也相應組合成32位。如果AHB slave的hready為高,則32位數據釋放到AHB總線上,同時復位AHB控制信號,下一個周期返回IDLE狀態;如果hready為低,則繼續保持WRITE_L_DATA狀態,直到AHB slave把hready拉高有效。如果等待時間過長,可以增加一個計數器使狀態機在一定時間后自動返回IDLE狀態,并標記相應的error狀態寄存器。例如,需要通過ADSP向haddr[31:0]=0x1234_5678地址內寫入hwdata[31:0]=0xaabb_ccdd,則測試平臺(采用vmt slave)模擬ADSP對外進行兩次寫操作,第一次向addr[18:0]=0x1234內寫0xaabb,第二次向addr[18:0]=0x5678內寫0xccdd,如圖5所示。第二次寫操作后正確產生AHB寫操作。

同樣,對于一個讀操作,狀態機也需要兩次對AHB發出讀動作,把讀到的slave數據分高低位兩次傳輸給ADSP,不同的是,為了保證AHB讀地址是32位,而不僅僅是ADSP外部Memory地址總線的19位,每次AHB的讀命令,需要ADSP兩次讀動作,第一次讀用來傳輸高位地址,第二次讀才能把完整的32位地址傳送到AHB上,使AHB產生讀操作。上述過程的狀態依次是圖4中的READ_ADDR_H、READ_ADDR_L、READ_HOLD、READ_TRANSFER。標志位rd_complete用來區分AHB的兩次讀動作,為0時在READ_TRANSFER狀態傳輸讀取數據的高16位,被ADSP讀取,下一個周期后進入BUSREQ狀態等待下一個讀命令;為1時在READ_TRANSTER狀態傳輸讀取數據的低16位,并返回IDLE狀態。例如需要讀取上述已經被寫入地址haddr[31:0]=0x1235_5678的值時,第一次ADSP發出讀addr[18:0]=0x1234,第二次發出讀addr[18:0]=0x5678,這時ADSP的data只傳輸高位數據0xaabb,ADSP再發兩次相同的讀命令后,data才傳輸低位數據0xccdd。對應的讀操作的仿真波形如圖6所示。

如前所述,ADSP外部Memory總線在對外讀寫時可以通過EBIU_AMBCTlx寄存器來選擇是否選通握手信號ARDY。為了提高傳輸的可靠性和準確度,在設計轉換模塊時需要考慮ARDY,如圖5、圖6中的讀寫操作時序圖所示,在每一次數據傳輸完成的最后一個狀態,需要將ARDY信號置1,然后在下一個IDLE或BUSREQ狀態將ARDY清0,這樣可以保證ADSP能正確讀到ADSP外部Memory數據總線上的有效數據,防止因ADSP對外讀寫時序設置不合理而造成系統不能正常運行。

6 FPGA實現

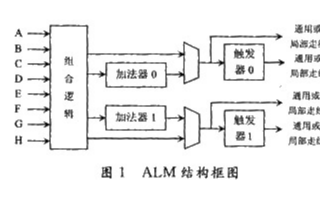

本模塊的設計是用于FPGA驗證用途的,對于大型視頻SoC系統的FPGA實時驗證,往往需要采用大容量的FPGA,因此本設計采用Altera Stratix II EP2S60器件進行FPGA驗證。采用Quartus綜合和布局布線后,一共需要140個ALUT和131個寄存器,最快時鐘可以達到300MHz。因為ADSP可以設置外部Memory總線的讀寫時序,所以對外訪問的速率不是惟一的。為了實現16位到32位的轉換雖然增加了讀寫的次數,但因為ADSP外部Memory同步時鐘頻率調整范圍很大,因此本設計完全可以滿足IP核功能驗證對頻率的要求,對于視頻SoC內部基本AHB總線和APB總線上的功能模塊都能正確實時驗證。基于ADSP-BF537內部嵌入的Blackfin處理器及其DSP接口,已經利用本接口模塊成功地驗證了AHB總線上的H264和MPEG一2的encode與decode加速器、Ethernet MAC控制器、SDRAM控制器以及APB總線上的UART、TIMER、AC97、GPIO和LCD控制器等低速外設。

隨著驗證環節在SoC產品開發過程中所占時間和開銷的迅速增加,Altera和Xilinx在其大容量FPGA芯片產品中,都集成了特定類型的CPU作為系統處理器,但它們都受到特定FPGA器件的限制。因此利用ADSP內嵌的強大Blackfin處理器和豐富的DSP外設,可以有效地提高驗證的效率和功能的完整性。本文的總線接口模塊的設計對具有不同讀寫時序的驗證板的正常工作起著重要的作用,SoC原型的搭建必然要求本模塊能真實反映實際AHB總線的動作,這樣對于保證各個功能模塊的完整性和實時工作將起很大的作用。

責任編輯:gt

-

FPGA

+關注

關注

1639文章

21887瀏覽量

610858 -

嵌入式

+關注

關注

5120文章

19407瀏覽量

312299 -

soc

+關注

關注

38文章

4284瀏覽量

220825

發布評論請先 登錄

相關推薦

基于Stratix II EP2S60改進中值濾波器的設計及實現,不看肯定后悔

Stratix II EP2S60 DSP Developm

針對Altera Stratix IV EP4SGX360和

針對Altera Stratix IV EP4SGX70和E

Altera推出業界密度最大的Stratix IV EP4S

一種線性卷積實時實現方案

基于Altera FPGA的視頻信號處理的設計與實現

Altera推出Quartus II v13.0,支持實現世界上最快的FPGA設計

如何設計Stratix II FPGA系統電源的詳細資料概述

業界密度最大的Stratix IV EP4SE820 FPGA(Altera)

鋯石FPGA A4_Nano開發板視頻:NiOS II硬件框架結構深入剖析2

鋯石FPGA A4_Nano開發板視頻:NiOS II硬件框架結構深入剖析(2)

采用StratixⅡ FPGA器件提高加法樹性能并實現設計

采用Altera Stratix II EP2S60器件實現SoC系統的FPGA實時驗證

采用Altera Stratix II EP2S60器件實現SoC系統的FPGA實時驗證

評論