引 言

在32位微處理器逐漸成為嵌入式系統主流的同時,嵌入式應用也變得越來越復雜。許多嵌入式系統都不得不借助于專用的操作系統來支撐自己的應用。uClinux作為類Unix操作系統,繼承了Linux的各種優秀的品質,成為首選的嵌入式系統的操作系統。

為自己的設備在操作系統下添加驅動程序,是嵌入式設計必不可少的部分。針對不同的設備類型,選擇合適的驅動程序的模式,同樣也是十分重要的。通常的設備驅動采用直接I/O的方式,如存儲器、看門狗等;而對于象網絡這樣的數據流設備的驅動,則應該用到中斷機制。

本文以uClinux為背景,以一種數據流設備為目標,介紹中斷驅動的I/O設備驅動的開發。

1 應用背景

1.1 硬件描述

本文介紹的驅動程序是應用在一種電信E1線路和以太網互聯設備上的。它是旁路接收E1數據并將其發送到以太網的某一臺服務器上,在服務器上對E1的話路和信令時隙分析。

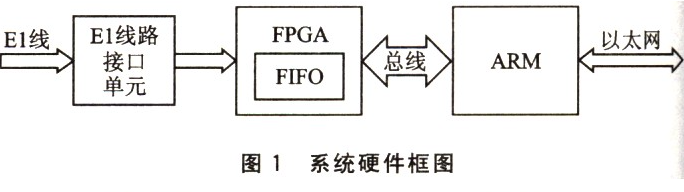

該設備中的處理器是采用三星公司出品的網絡型ARM處理器S3C4510B。E1線路接口采用Dallas半導體公司的專用El接口單元(LIU)芯片 DS2148,它完成波形整理、時鐘恢復和HDB3解碼。DS2148將整理后的E1數據流送給一片Altera公司的Cyclone系列的 FPGA(EPlC3T144C8),它將串行的E1數據流存入到FIFO,再通過ARM的32位外部總線將數據傳送給ARM。ARM將數據打包通過以太網發送到服務器上。圖l所示是本系統的硬件框圖。本文主要介紹接在ARM的外部總線上的FPGA,在uClinux下的驅動程序中斷機制的設計。

1.2硬件連接

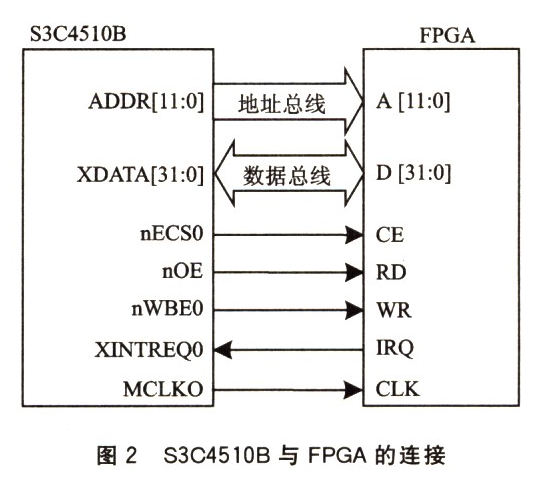

S3C4510B處理器和FPGA的連接電路如圖2所示。

1.3 FPGA內FIFO的結構

在FPGA內部設置了兩個FIFO。為了防止ARM和FPGA操作的沖突,ARM和FPGA對兩個FIFO操作采用乒乓方式,這樣ARM和FPGA就可以同時操作不同的FIFO,而不需要等待。FIFO的大小是4096位,能容納一個E1復幀的數據量。當FPGA將一個FIFO填滿后,會用中斷的方式通知ARM來讀FIFO,同時FPGA會置內部的F1FO狀態寄存器。 FIFO)狀態寄存器命名為fpga_imf,是一個32位的寄存器,用其中某幾位置“l”,表示對應的FIFO需要讀取。

2 軟件設計

中斷驅動的I/O是指,輸人數據在中斷期間被填充到緩沖區內,并由讀取該設備的進程取走緩沖區內的數據;輸出緩沖區由寫設備的進程填充,并在中斷期間取走數據。數據緩沖可以將數據的發送和接收與write及read系統調用分離開來,提高系統的整體性能。下面是uCllnux下的中斷程序的設計。

2.1 uClinux下的中斷程序

在uClinux系統中,通過調用下面這個函數向系統申請一個中斷通道(或中斷請求IRQ),并在處理完以后釋放掉它。

mt reqLIest_irq(unsigned int irq,void(*handler)(int,vold*,

struct pt_regs*),unsigned 10ng flags,const chat*device,

vold*dev_id);

void free_irq(unstgned int lrq,VOid*dev_id);

其中,irq是中斷號。在本系統中它對應于S3C4510B的21個中斷源。這里用的是中斷源O。handler指向要安裝的中斷處理函數的指針。 flags是一個與中斷管理有關的各種選項的字節掩碼。device傳遞給request_irq的字符串,在/proc/interrupts中用于顯示中斷的擁有者。dev_id指針用于共享的中斷信號線。函數的返回值為O時表示成功,或者返回一個負的錯誤碼。函數返回一EBUJSY通知另一個設備驅動程序已經使用了要申請的中斷信號線。下面是FPGA的設備中斷申請函數。這個函數是在驅動中的fpga_open函數中被調用的。

int fpga_open(struct inode*inocle,stuct_file*file){

int result;

result=request_irq(FPGA_IRQ,δfpga_isr,SA_INTER-RUPT,″fpga″,NULL);

if(resuIt!=O){

printk(KERN_INFO”Can not register FPGA ISR!\n”);}else{

printk(KERN_INFO″FPGA ISR Register successfully!\n”);

}

}

在申請了中斷通道后,系統會響應外部中斷0,而進入中斷處理程序。中斷處理程序的第一步是要先清除S3C4510B的中斷懸掛寄存器的外部中斷O位。這是為了讓FPGA可以產生新的中斷。在uClinux系統中是調用下面的宏來實現的。

責任編輯:lq6

-

寄存器

+關注

關注

31文章

5421瀏覽量

123398 -

嵌入式系統

+關注

關注

41文章

3667瀏覽量

130910 -

微處理器

+關注

關注

11文章

2371瀏覽量

83860

發布評論請先 登錄

嵌入式學習-飛凌嵌入式ElfBoard ELF 1板卡-I2C設備驅動之Linux下的I2C驅動簡介

飛凌嵌入式ElfBoard ELF 1板卡-I2C設備驅動之Linux下的I2C驅動簡介

恩智浦為無線連接SoC開發的統一WiFi驅動程序多芯片多接口驅動(MXM)

以uClinux為背景,介紹中斷驅動的I/O設備驅動的開發

以uClinux為背景,介紹中斷驅動的I/O設備驅動的開發

評論