大俠好,阿Q來也,今天是第二次和各位見面,請各位大俠多多關照。今天給各位大俠帶來一篇項目開發經驗分享“基于JESD204B的LMK04821芯片項目開發”第二篇,這是本人實打實的項目開發經驗,希望可以給有需要的大俠提供一些參考學習作用。

以后機會多多,慢慢分享一些項目開發以及學習方面的內容,歡迎各位大俠一起切磋交流。

204B實戰應用-LMK04821代碼詳解(二)

一、 SPI協議

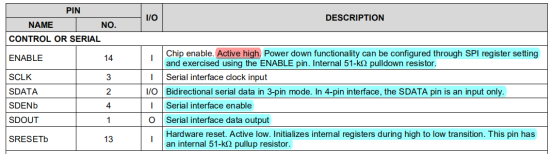

通過閱讀LMK04821數據手冊,我們可以從中知道,可以通過SPI協議對LMK04821進行寄存器的配置工作,進而實現我們設計所需要的功能。

SPI協議部分,咱們可以用3線,或者4線,在本次設計中,使用3線。關于SPI的時序部分,這兒就不再贅述,手冊里面都有詳細的描述。

圖1

二、 SPI寄存器配置模塊設計

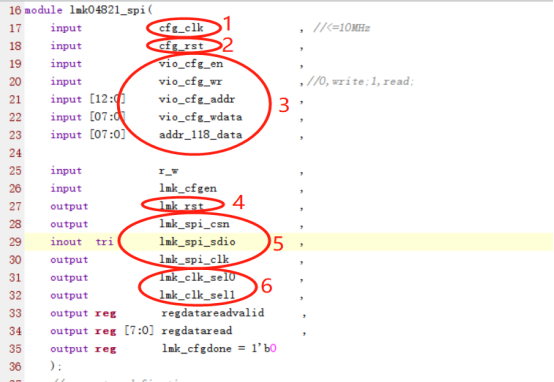

圖2

如圖2所示,就是配置LMK04821存器的單元,信號定義如下:

1、cfg_clk:系統時鐘;

2、cfg_rst:系統復位;

3、通過VIO控制的信號,這組信號存在的目的在于方便檢測自己配置寄存器的正確性。

vio_cfg_en:配置寄存器使能信號;

vio_cfg_wr:配置寄存器讀寫使能,0寫1讀;

vio_cfg_addr:配置的寄存器地址;

vio_cfg_wdata:寄存器中配置的值;

addr_118_data:預留信號,模塊中沒有用;

我們在配置LMK04821寄存器時,要驗證配置寄存器操作是否正確,就要有寫有讀,在對應的寄存器內寫入對應的數值,然后進行讀操作,觀察正確性。本次設計是在vivado環境下進行設計,通過添加VIO的IP核,來控制讀寫操作。同時,添加ILA配合VIO來進行讀寫數據操作的觀測。別的開發環境下思路一樣。

該組信號僅在回讀寄存器時使用,目的是為了驗證寄存器讀寫正確性。

圖3

4、lmk_rst:LMK04821復位信號,用于復位LMK04821,直接和LMK04821芯片相連;

5、3線制SPI信號:

lmk_spi_csn:片選;

lmk_spi_sdio:數據;

lmk_spi_clk:時鐘;

6、可編程管教:主要和LMK04821內部的PLL相關,本次設計中默認為0;

lmk_clk_sel0 :sel0;

lmk_clk_sel1 :sel1;

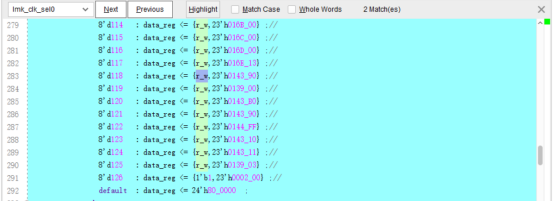

三、 SPI數據buffer定義

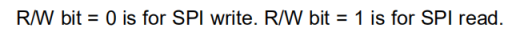

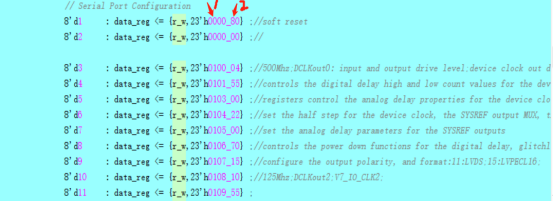

在本次設計中,SPI配置數據buffer,data_reg為24bit,r_w占1bit,箭頭1所指包含W1、W2以及地址位占13bit,具體見SPI時序圖;箭頭2所指數據位8bit。

圖4

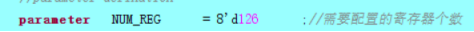

根據圖5我們可以知道,要配置LMK04821我們需要配置126個寄存器,這126個寄存器來源參見第一章實戰記錄。

其中,126個寄存器包含必須要配的寄存器、一些無關緊要的寄存器、以及功能實現所需要的寄存器等,有些寄存器需要配置多次。

圖5

四、 SPI時序實現

設計中,我們需要按照順序配置126個寄存器,也就是說SPI要執行126次。因此,在代碼實現過程中,注意寄存器配置的順序,并且保證每個寄存器都準確無誤的配置完成,才能進行下一個寄存器的配置。如果在設計中,要求LMK004821實現不同的功能,當配置的寄存器個數不一致時,在v文件中更改圖6所示的參數即可。

圖6

下一篇,將詳細介紹jesd_204B IP核應用的相關知識,各位大俠,盡請關注。

原文標題:FPGA項目開發:204B實戰應用-LMK04821代碼詳解(二)

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618329 -

芯片

+關注

關注

459文章

52502瀏覽量

440720

發布評論請先 登錄

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

JESD204B使用說明

調試ADS52J90板卡JESD204B接口遇到的問題求解

在FPGA里面例化了8個jesd204B的ip核同步接收8塊AFE芯片的信號,怎么連接設備時鐘和sysref到AFE和FPGA?

如何配置LMK04828時鐘芯片生成JESD204b需要的時鐘?

LMK04821遇到的問題求解

LMK04821 SPI通信不了是怎么回事?如何解決?

LMK04821測量SPI波形異常,無法寫入及讀取怎么解決?

從JESD204B升級到JESD204C時的系統設計注意事項

采用JESD204B的LMK5C33216超低抖動時鐘同步器數據表

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

基于JESD204B的LMK04821芯片項目詳解

基于JESD204B的LMK04821芯片項目詳解

評論