自從微處理器面世以來(lái)就有了嵌入式系統(tǒng)設(shè)計(jì)。現(xiàn)代嵌入式系統(tǒng)與以往不同的地方在于,極端的運(yùn)算要求需要使用多個(gè)CPU和DSP內(nèi)核、數(shù)十甚至上百個(gè)外設(shè)和硬件加速模塊,以及多級(jí)存儲(chǔ)器結(jié)構(gòu),并且所有這些都要通過(guò)復(fù)雜的多級(jí)總線和交叉總線相連。同時(shí),嵌入式系統(tǒng)的軟件規(guī)模也在呈指數(shù)上升。

提高嵌入式設(shè)計(jì)質(zhì)量和產(chǎn)能的一個(gè)方法,就是采用虛擬系統(tǒng)原型(VSP)。VSP是一種周期、寄存器和時(shí)序都十分精確的系統(tǒng)級(jí)快速軟件仿真模型。“編輯-編譯-執(zhí)行-調(diào)試”周期的時(shí)間與在實(shí)際硬件中相當(dāng)。一旦確定了最優(yōu)架構(gòu),勝人一籌的VSP就能成為系統(tǒng)的可操作規(guī)范(黃金版參考設(shè)計(jì))。硬件設(shè)計(jì)成員立即就能開始具體的硬件設(shè)計(jì),而軟件開發(fā)人員也可以利用VSP連接和開發(fā)剩余的系統(tǒng)軟件。

以下是給那些準(zhǔn)備采用這種極具建設(shè)性的設(shè)計(jì)方法的工程師所提供的一些建議。

應(yīng)該盡早使用VSP量化架構(gòu)性能。多處理器架構(gòu)要求重點(diǎn)關(guān)注總線和存儲(chǔ)器系統(tǒng)架構(gòu)。全面測(cè)試有助于確定總線架構(gòu)的瓶頸。如果不解決瓶頸問(wèn)題,那么可能會(huì)引起資源沖突,甚至導(dǎo)致系統(tǒng)癱瘓和進(jìn)程處于“饑餓”狀態(tài)。

測(cè)試候選架構(gòu)性能,并與實(shí)際或具有代表性的應(yīng)用軟件進(jìn)行對(duì)比。這種方法可以避免不確定因素以及與估計(jì)方法有關(guān)的錯(cuò)誤,并且更容易構(gòu)建。

使用VSP來(lái)捕捉以可執(zhí)行規(guī)范形式表示的意圖,從而推進(jìn)實(shí)現(xiàn)和驗(yàn)證。在明確描述系統(tǒng)操作方面,一個(gè)全面開發(fā)的VSP要比書面規(guī)范更加高效。

使用周期精確模型。這種描述會(huì)帶來(lái)更少的限制:它們可以用于時(shí)序重要的高度反應(yīng)系統(tǒng),并可以與實(shí)現(xiàn)驗(yàn)證結(jié)合使用。

在整個(gè)設(shè)計(jì)過(guò)程中對(duì)VSP進(jìn)行維護(hù),當(dāng)發(fā)生以實(shí)現(xiàn)為主導(dǎo)的架構(gòu)調(diào)整時(shí),對(duì)VSP進(jìn)行更新和重新發(fā)布。VSP可以用于調(diào)試在實(shí)際系統(tǒng)生成很長(zhǎng)時(shí)間后發(fā)生的系統(tǒng)問(wèn)題。

將VSP用于軟件開發(fā)。具有足夠性能的VSP不僅可以用于早期的設(shè)備驅(qū)動(dòng)創(chuàng)建,也能用于中間件和最終應(yīng)用的開發(fā)。提前開發(fā)和測(cè)試應(yīng)用軟件可以在實(shí)現(xiàn)完成前就發(fā)現(xiàn)缺陷,從而節(jié)省開發(fā)成本。

不應(yīng)該在開始軟件開發(fā)和系統(tǒng)級(jí)測(cè)試之前等待硬件開發(fā)。與傳統(tǒng)基于硬件原型的設(shè)計(jì)方法相比,VSP可以幫助用戶提前一年開始軟件的開發(fā)。

等待最終應(yīng)用開發(fā)完成后開始應(yīng)用層性能測(cè)試。對(duì)具有代表性的應(yīng)用進(jìn)行測(cè)試總比什么都不做好。

盡可能發(fā)掘功能唯一模型的作用。功能唯一的模型不能精確地處理總線時(shí)序和處理器運(yùn)行的異常情況。總線帶寬會(huì)影響程序訪問(wèn)對(duì)系統(tǒng)性能有重要影響的指令和數(shù)據(jù)資源。

繼續(xù)更適合實(shí)現(xiàn)而不是仿真的建模實(shí)踐。把重點(diǎn)放在最重要的方面。例如,考慮用于描述可綜合RTL描述的建模類型。因?yàn)槠渲饕康氖蔷C合,因此不需要用很多復(fù)雜冗長(zhǎng)的描述來(lái)如實(shí)地反映周期精確功能。過(guò)多的描述反而會(huì)降低仿真的速度。

使用由快速功能性模型和慢但精確的模型組成的混合建模方法。當(dāng)設(shè)計(jì)要經(jīng)歷多個(gè)工程更改時(shí)(會(huì)花費(fèi)相當(dāng)多時(shí)間和資源),要使多個(gè)模型在功能上保持同步。另外,慢但精確的模型缺乏足夠的速度進(jìn)行關(guān)鍵時(shí)序的全面測(cè)試。兩種模型分開使用的解決方案更簡(jiǎn)單也更具建設(shè)性。

對(duì)不充足的性能感到滿足。速度當(dāng)然是越快越好,但是同時(shí)要注意軟件開發(fā)會(huì)要求性能達(dá)到數(shù)十Mips。通常,必須使用數(shù)十億的時(shí)鐘才能充分開發(fā)軟件。

編輯:jq

-

處理器

+關(guān)注

關(guān)注

68文章

19828瀏覽量

233819 -

嵌入式

+關(guān)注

關(guān)注

5143文章

19566瀏覽量

315548 -

寄存器

+關(guān)注

關(guān)注

31文章

5425瀏覽量

123595

發(fā)布評(píng)論請(qǐng)先 登錄

嵌入式開發(fā)入門指南:從零開始學(xué)習(xí)嵌入式

嵌入式系統(tǒng)開發(fā)與硬件的關(guān)系 嵌入式系統(tǒng)開發(fā)常見問(wèn)題解決

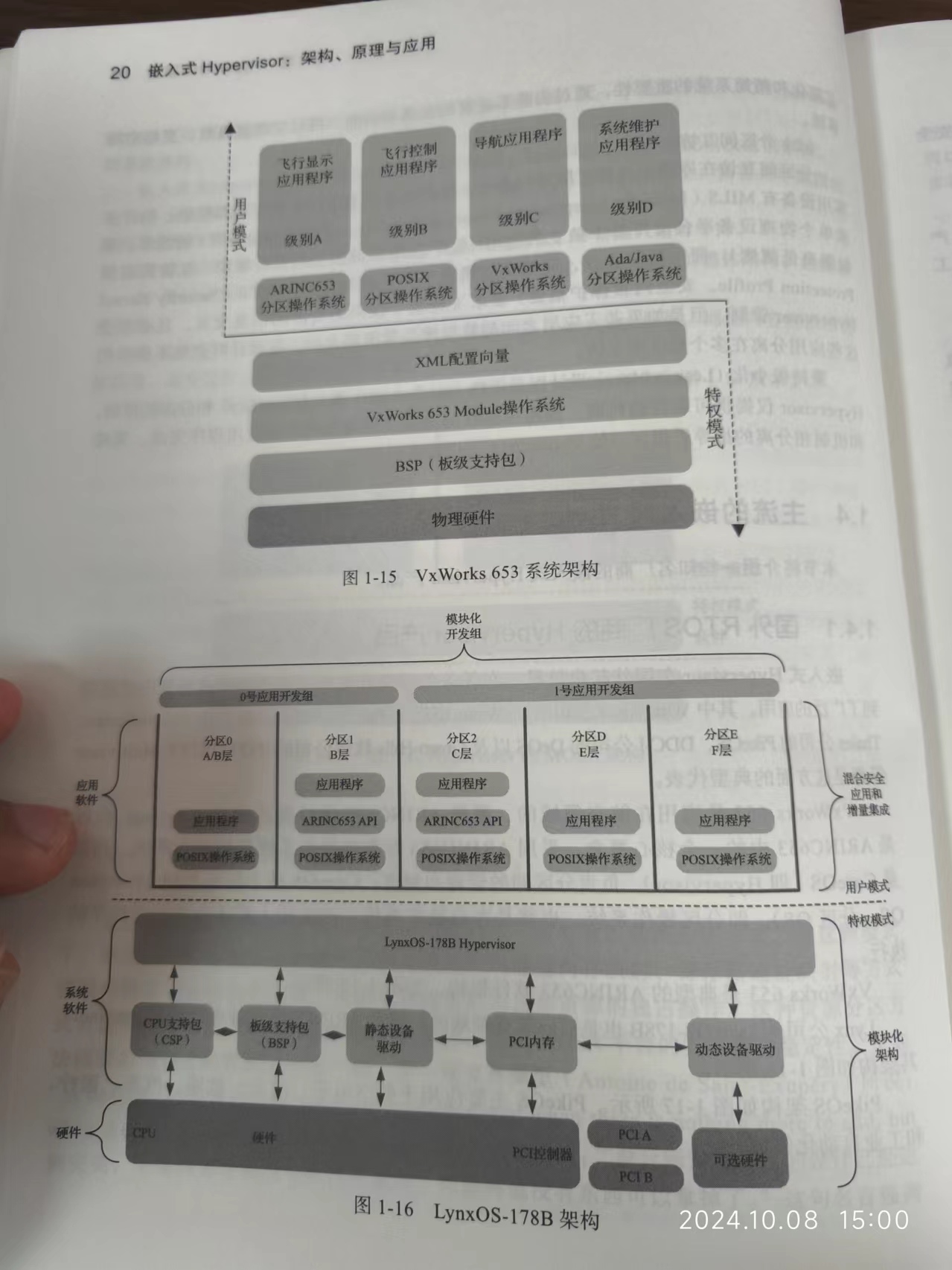

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+ 了解Hypervisor

嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用 閱讀體驗(yàn) +分離內(nèi)核的嵌入式Hyperviso

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+第三四章閱讀報(bào)告

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+第一二章讀后感

嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用 閱讀體驗(yàn) +Hypervisor基礎(chǔ)概念

嵌入式系統(tǒng)的啟動(dòng)流程

嵌入式系統(tǒng)的未來(lái)趨勢(shì)有哪些?

新書發(fā)布——《RT-Thread嵌入式實(shí)時(shí)操作系統(tǒng)內(nèi)核、驅(qū)動(dòng)和應(yīng)用開發(fā)技術(shù)》

淺述虛擬系統(tǒng)原型簡(jiǎn)化嵌入式多內(nèi)核設(shè)計(jì)

淺述虛擬系統(tǒng)原型簡(jiǎn)化嵌入式多內(nèi)核設(shè)計(jì)

評(píng)論