本實驗,為ZX-2開發板的綜合實驗,該實驗利用ZX-2開發板上的ADC、獨立按鍵、UART等外設,搭建了一個具備豐富功能的數據采集卡,ZX-2開發板負責進行數據的采集并將數據通過串口發送到PC機上,PC端,利用強大的串口調試工具——串口獵人,來實現數據的接收分析,并將數據分別以波形、碼表、柱狀圖的形式動態顯示出來,以讓使用者能夠直觀的看到ADC采集到的信號細節。同時,用戶也可以使用串口獵人通過串口給下位機(FPGA)發送指令,下位機將對接收到的指令進行解碼,然后依據解碼結果來配置FPGA中各個子模塊的控制寄存器,以實現通過串口控制FPGA中子模塊工作狀態的功能。

本實驗中,涉及到的應用模塊和知識點如下所示:

串口收發模塊的設計和使用;

串口收發模塊仿真模型的設計;

串口簡單數據幀的解碼;

串口幀轉Memory Mapped總線的設計;

Memory MappedSlave模塊的設計;

線性序列機設計思想的應用(ADC驅動);

獨立按鍵消抖的分析與實現;

直接數字頻率合成(DDS)的設計與實現;

使能時鐘對系統間模塊協調工作的重要性;

串口獵人的詳細使用;

完整系統的仿真驗證設計;

頭文件在設計中的運用;

本實驗不僅注重可綜合的代碼編寫,同時更注重代碼的仿真驗證。通過仿真,我們能夠尋找設計中可能存在的問題并修正。最終,在整個系統仿真無誤的基礎上,下載到開發板上一次性成功。

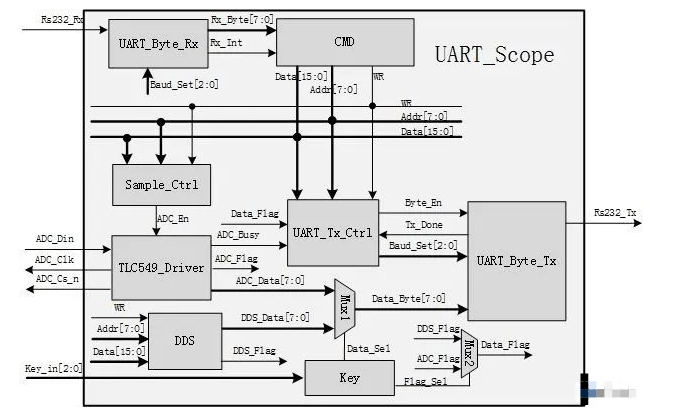

下圖為本設計的框架結構圖:

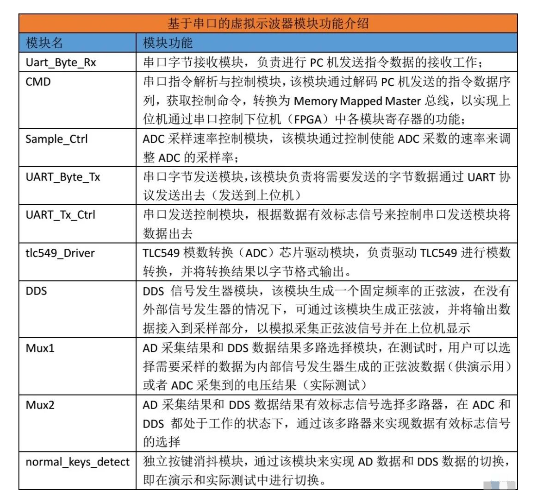

系統采用模塊化設計,在模塊劃分的過程中,重點考慮了系統的可擴展性,下表為對系統中各模塊功能的簡單介紹。

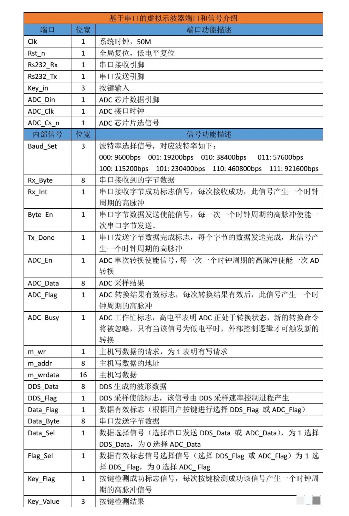

系統中各端口和信號的功能介紹如下:

本實驗為綜合性實驗,代碼量較大,因此這里只針對部分代碼進行講解。

責任編輯:lq6

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618517 -

存儲器

+關注

關注

38文章

7653瀏覽量

167411 -

adc

+關注

關注

99文章

6709瀏覽量

549231 -

串口

+關注

關注

15文章

1588瀏覽量

79946

原文標題:基于ZX-2型FPGA開發板的串口示波器(一)

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

1.6T光模塊的仿真

Simulink模型仿真與分析技巧

無線串口模塊—配置軟件以及串口助手的使用

請問怎樣去設計串口收發模塊仿真模型?

請問怎樣去設計串口收發模塊仿真模型?

評論