Xilinx 復(fù)位準(zhǔn)則:Xilinx FPGA復(fù)位策略

(1)盡量少使用復(fù)位,特別是少用全局復(fù)位,能不用復(fù)位就不用,一定要用復(fù)位的使用局部復(fù)位;

(2)如果必須要復(fù)位,在同步和異步復(fù)位上,則盡量使用同步復(fù)位,一定要用異步復(fù)位的地方,采用“異步復(fù)位、同步釋放”;

(3)復(fù)位電平選擇高電平復(fù)位;

(這里說明,由于 Altera 和 Xilinx 器件內(nèi)部結(jié)構(gòu)的不同,Altera 的 FPGA 推薦低電平復(fù)位)

一、異步復(fù)位同步釋放

針對(duì)異步復(fù)位、同步釋放,一直沒搞明白在使用同步化以后的復(fù)位信號(hào)時(shí),到底是使用同步復(fù)位還是異步復(fù)位?

比如針對(duì)輸入的異步復(fù)位信號(hào)rst,使用本地時(shí)鐘clk將其同步化以后得到一個(gè)新的復(fù)位信號(hào)sys_rst,當(dāng)使用sys_rst時(shí),是將sys_rst作為同步復(fù)位信號(hào)還是異步復(fù)位信號(hào)?

always @(posedge clk or posedge rst) begin if(rst)begin rst_r0 《 = 1‘b1; rst_r1 《 = 1’b1; end else begin rst_r0 《 = 1‘b0; rst_r1 《 = rst_r0; end end assign sys_rst = rst_r1;

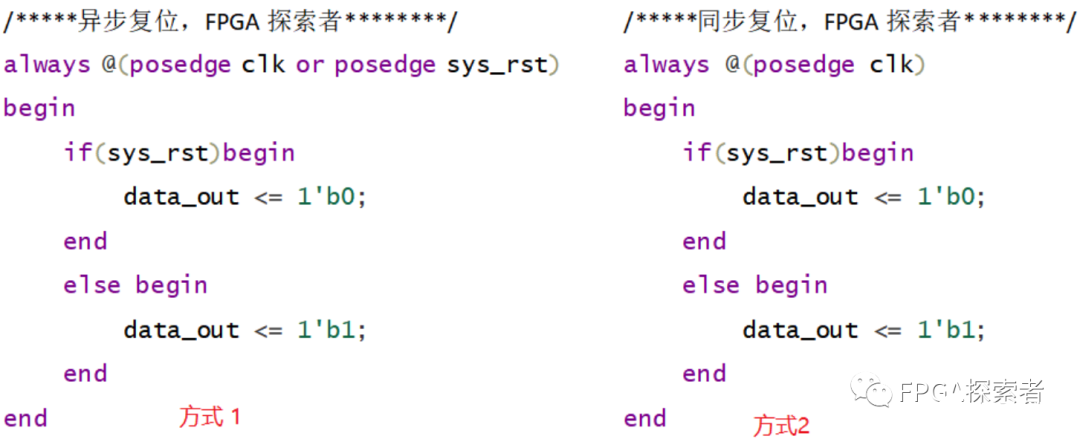

如下圖所示,選方式1還是方式2?

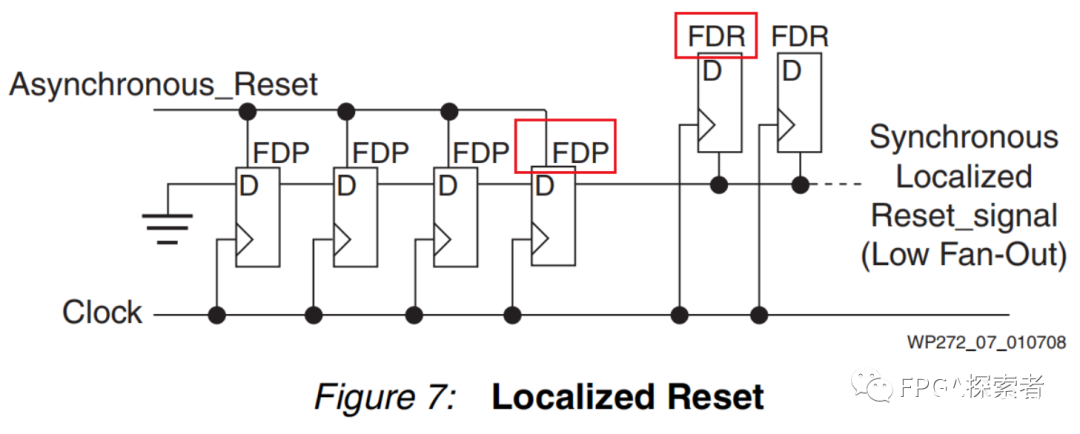

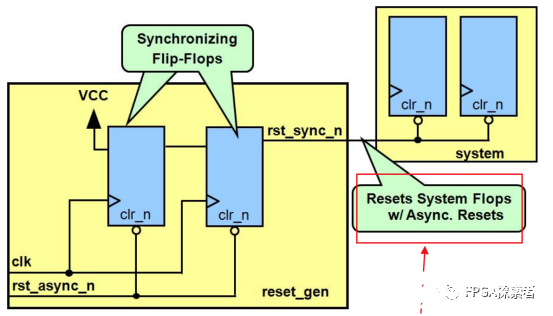

針對(duì)此問題查找了很多資料,網(wǎng)絡(luò)上多是將sys_rst繼續(xù)按照方式1異步復(fù)位使用,Xilinx復(fù)位白皮書wp272中提到的異步復(fù)位同步釋放 如圖所示:

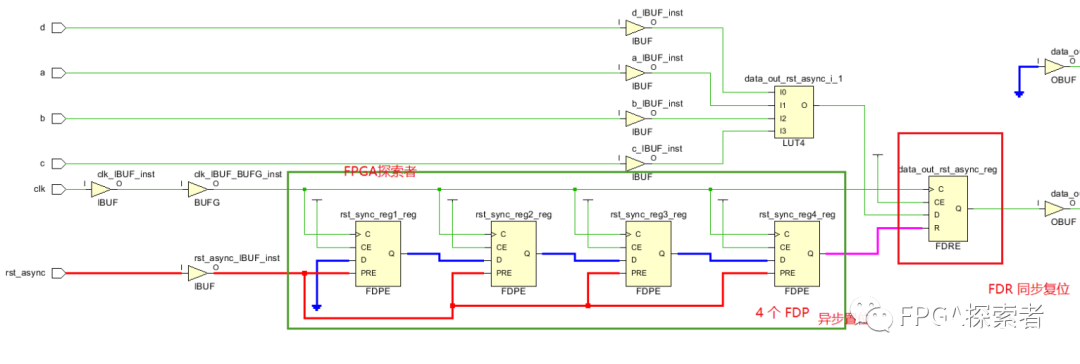

對(duì)于輸入的異步復(fù)位Asynchronous Reset,首先使用了4個(gè)觸發(fā)器來做同步(一般用2個(gè)即可,4個(gè)出現(xiàn)亞穩(wěn)態(tài)的概率更小),觸發(fā)器類型為FDP(異步置位),同步化以后的復(fù)位信號(hào)去使用時(shí)綜合出的觸發(fā)器類型為FDR(同步復(fù)位),即在Xilinx中是將sys_rst按照方式2同步復(fù)位使用。

使用FDP異步置位的原因是因?yàn)閄ilinx推薦高電平復(fù)位,當(dāng)異步復(fù)位信號(hào)到來時(shí),輸出復(fù)位電平“1”,即異步置位FDP,當(dāng)復(fù)位消失后,D觸發(fā)器在每個(gè)時(shí)鐘邊沿輸出前一級(jí)觸發(fā)器的值,一定周期后,最后一級(jí)的FDP穩(wěn)定輸出“0”。

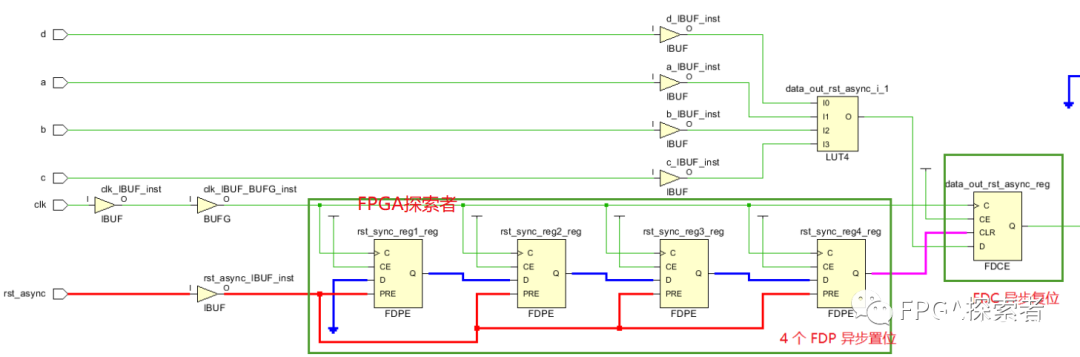

使用Xilinx A7系列FPGA實(shí)現(xiàn)異步復(fù)位、同步釋放代碼,確定同步化后的復(fù)位使用情況。

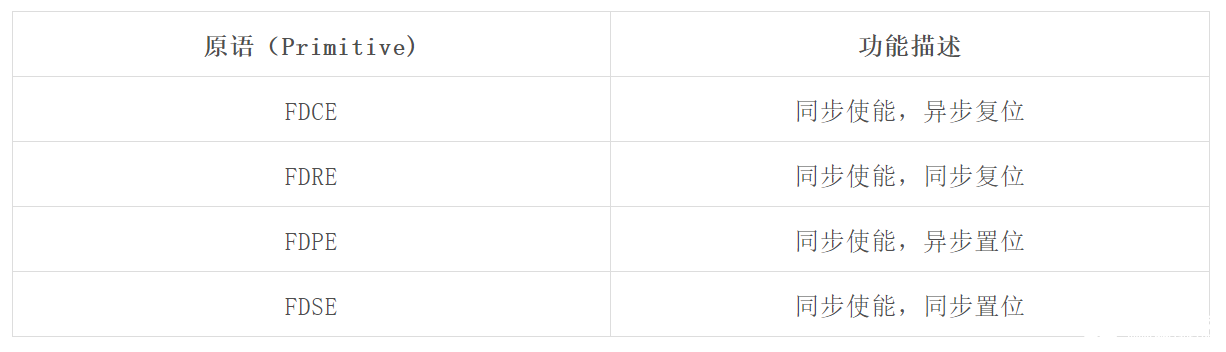

二、Xilinx復(fù)位程序?qū)Ρ?/strong>

1. 將同步化后的復(fù)位當(dāng)作異步復(fù)位信號(hào)

/******FPGA探索者******/ always @(posedge clk or posedge rst_async) begin if(rst_async == 1’b1) begin rst_sync_reg1 《= 1‘b1; rst_sync_reg2 《= 1’b1; rst_sync_reg3 《= 1‘b1; rst_sync_reg4 《= 1’b1; end else begin rst_sync_reg1 《= 1‘b0; rst_sync_reg2 《= rst_sync_reg1; rst_sync_reg3 《= rst_sync_reg2; rst_sync_reg4 《= rst_sync_reg3; end end wire sys_rst; assign sys_rst = rst_sync_reg4; always @(posedge clk) begin if(sys_rst == 1’b1) begin data_out_rst_async 《= 1‘b0; end else begin data_out_rst_async 《= a & b & c & d; end end

綜合并布局布線后的原理圖如圖所示,顯然,綜合后對(duì)sys_rst復(fù)位,將其作為異步復(fù)位綜合出FDCE同步使能異步復(fù)位(這里不考慮使能),和白皮書WP272給出的參考電路顯然不一致。

2. 將同步化后的復(fù)位當(dāng)作同步復(fù)位信號(hào)

/******FPGA探索者******/ always @(posedge clk or posedge rst_async) begin if(rst_async == 1’b1) begin rst_sync_reg1 《 = 1‘b1; rst_sync_reg2 《 = 1’b1; rst_sync_reg3 《 = 1‘b1; rst_sync_reg4 《 = 1’b1; end else begin rst_sync_reg1 《 = 1‘b0; rst_sync_reg2 《 = rst_sync_reg1; rst_sync_reg3 《 = rst_sync_reg2; rst_sync_reg4 《 = rst_sync_reg3; end end wire sys_rst; assign sys_rst = rst_sync_reg4; always @(posedge clk) begin if(sys_rst == 1’b1) begin data_out_rst_async 《 = 1‘b0; end else begin data_out_rst_async 《 = a & b & c & d; end end

綜合并布局布線后的原理圖如圖所示,顯然,綜合后對(duì)sys_rst復(fù)位,將其作為同步復(fù)位綜合出FDRE同步使能異步復(fù)位(這里不考慮使能),和白皮書WP272給出的參考電路一致。

異步復(fù)位相比較同步復(fù)位,在Xilinx的FPGA中資源是一致的,異步復(fù)位的優(yōu)勢(shì)在于復(fù)位信號(hào)一來就能檢測(cè)到,不需要保持至少一個(gè)時(shí)鐘周期才能在時(shí)鐘邊沿檢測(cè)到,通過仿真來驗(yàn)證上述電路是否能實(shí)現(xiàn)異步復(fù)位一來就能檢測(cè)到。

三、仿真結(jié)果

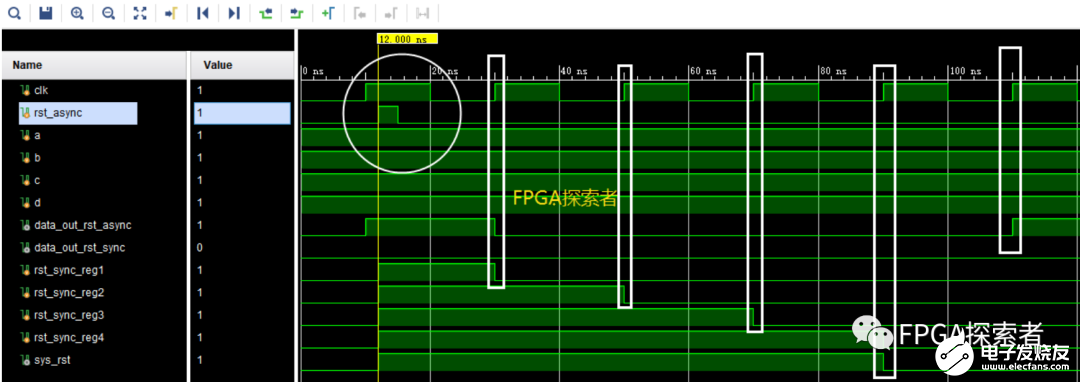

設(shè)置時(shí)鐘50MHz,時(shí)鐘周期20ns,給一個(gè)持續(xù)時(shí)間3ns的異步復(fù)位信號(hào),且持續(xù)時(shí)間均不出現(xiàn)在時(shí)鐘上升沿檢測(cè)期間,可以看到:

(1)rst_async異步復(fù)位一旦給出,用于同步的4個(gè)寄存器rst_sync_reg1~4立刻輸出高電平“1”,在下一個(gè)時(shí)鐘上升沿檢測(cè)到同步復(fù)位并將輸出data_out_rst_async復(fù)位;

(2)異步復(fù)位信號(hào)釋放后,經(jīng)過同步的sys_rst經(jīng)過一定周期后在時(shí)鐘邊沿同步釋放;

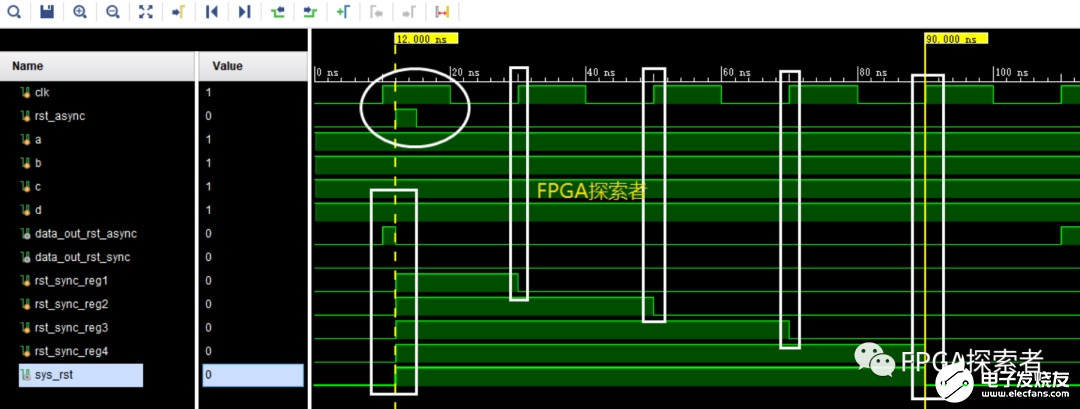

按照同樣的復(fù)位,將sys_rst看作異步復(fù)位,仿真結(jié)果如下,相比于上圖,區(qū)別在于異步復(fù)位信號(hào)rst_async一旦產(chǎn)生,輸出立刻復(fù)位,且同樣是同步釋放,好像這種處理才更符合異步復(fù)位、同步釋放。。。。。。

那么為什么Xilinx白皮書還是將sys_rst按照同步復(fù)位去做的呢?難道寫錯(cuò)了?

綜合考慮可能有這樣的因素:

(1)當(dāng)作同步復(fù)位的差別只在于復(fù)位時(shí)間會(huì)稍晚一些,要在時(shí)鐘的下一個(gè)邊沿檢測(cè)到,但是還是能夠識(shí)別到輸入的rst_async異步復(fù)位信號(hào),所以從復(fù)位角度來說,都能夠后實(shí)現(xiàn)復(fù)位效果;

(2)根據(jù)Xilinx復(fù)位準(zhǔn)則,我們知道同步復(fù)位相比異步復(fù)位有很多好處,具體參見:Xilinx FPGA 復(fù)位策略白皮書,既然兩者對(duì)后級(jí)復(fù)位沒有功能上的差別,那么優(yōu)先選擇同步復(fù)位;

經(jīng)過異步復(fù)位同步釋放處理后,相比于純粹的異步復(fù)位,降低了異步復(fù)位信號(hào)釋放導(dǎo)致亞穩(wěn)態(tài)的可能性;相比同步復(fù)位,能夠識(shí)別到同步復(fù)位中檢測(cè)不到的復(fù)位信號(hào)(如上圖所示的rst_async在同步復(fù)位是檢測(cè)不到的);綜合兩者的優(yōu)勢(shì),異步復(fù)位同步釋放。

四、Altera復(fù)位

Altera還是把這個(gè)同步后的復(fù)位當(dāng)作異步復(fù)位來用的,且推薦低電平復(fù)位。

從上面的分析來看,這里當(dāng)作異步復(fù)位還是同步復(fù)位對(duì)于復(fù)位結(jié)果本身沒有太大的影響,區(qū)別在于Xilinx是推薦同步復(fù)位來節(jié)省資源(比如DSP48E或BRAM,異步復(fù)位比同步復(fù)位耗資源),而Altera的FPGA中帶異步復(fù)位的觸發(fā)器,想要同步復(fù)位需要消耗更多的資源。

編輯:lyn

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618813 -

Xilinx

+關(guān)注

關(guān)注

73文章

2185瀏覽量

125438 -

同步復(fù)位

+關(guān)注

關(guān)注

0文章

27瀏覽量

10877 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13516

發(fā)布評(píng)論請(qǐng)先 登錄

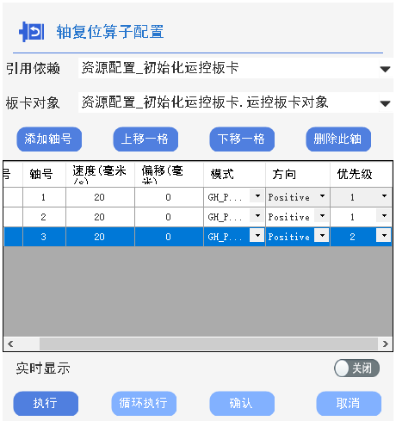

GraniStudio零代碼平臺(tái)軸復(fù)位算子支持多少個(gè)軸同時(shí)復(fù)位,有哪些回零模式?

復(fù)位電路的核心功能和主要類型

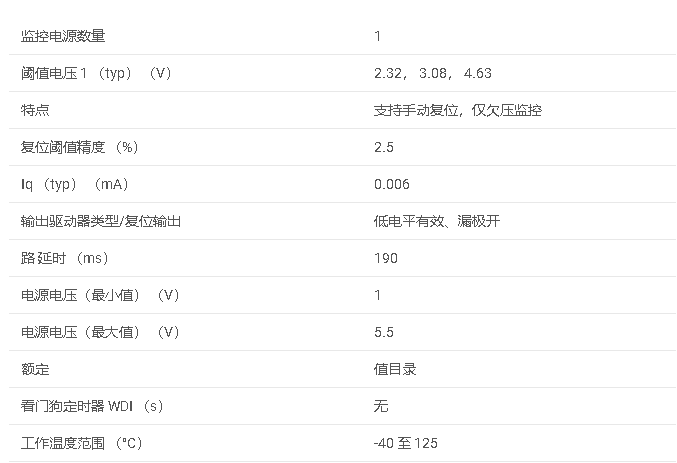

LM3724系列 低功率電壓監(jiān)控和復(fù)位IC,帶手動(dòng)復(fù)位功能數(shù)據(jù)手冊(cè)

復(fù)位電路的作用、控制方式和類型

FPGA復(fù)位的8種技巧

復(fù)位電路的設(shè)計(jì)問題

復(fù)位電路的三種方式 復(fù)位電路的原理和作用

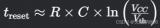

復(fù)位電路的電容多大的 復(fù)位電路設(shè)計(jì)類型有哪幾種

復(fù)位電路靜電整改案例分享(一)——交換機(jī)復(fù)位電路

詳細(xì)講解同步后的復(fù)位是同步復(fù)位還是異步復(fù)位?

詳細(xì)講解同步后的復(fù)位是同步復(fù)位還是異步復(fù)位?

評(píng)論