1 多時(shí)鐘域的異步復(fù)位同步釋放

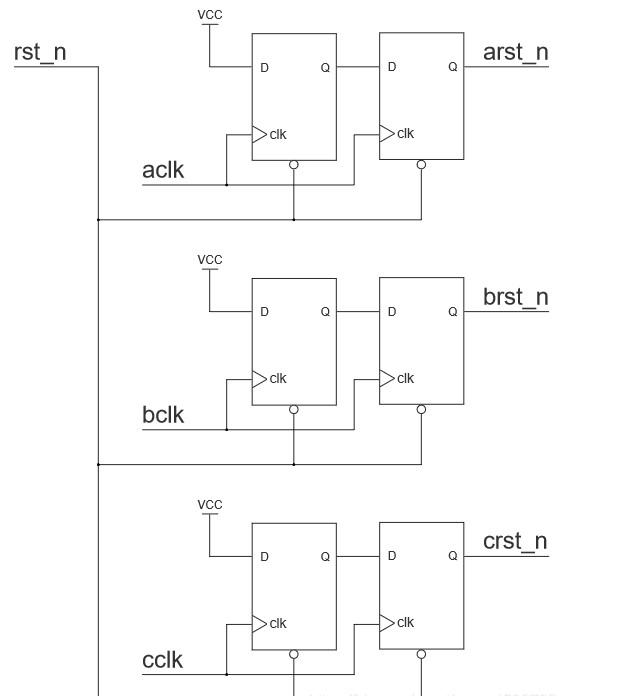

當(dāng)外部輸入的復(fù)位信號(hào)只有一個(gè),但是時(shí)鐘域有多個(gè)時(shí),使用每個(gè)時(shí)鐘搭建自己的復(fù)位同步器即可,如下所示。

verilog代碼如下:

module CLOCK_RESET( input rst_n, input aclk, input bclk, input cclk, output reg arst_n, output reg brst_n, output reg crst_n );

reg arst_n0,arst_n1;reg brst_n0,brst_n1;reg crst_n0,crst_n1;

always @(posedge aclk or negedge rst_n) if(rst_n==0) begin arst_n0《=1‘b1; arst_n1《=1’b0; arst_n《=1‘b0; end else begin arst_n《=arst_n1; arst_n1《=arst_n0; end always @(posedge bclk or negedge rst_n) if(rst_n==0) begin brst_n0《=1’b1; brst_n1《=1‘b0; brst_n《=1’b0; end else begin brst_n《=brst_n1; brst_n1《=brst_n0; end always @(posedge cclk or negedge rst_n) if(rst_n==0) begin crst_n0《=1‘b1; crst_n1《=1’b0; crst_n《=1‘b0; end else begin crst_n《=crst_n1; crst_n1《=crst_n0; end endmodule

2 多時(shí)鐘域的按順序復(fù)位釋放

當(dāng)多個(gè)時(shí)鐘域之間對(duì)復(fù)位釋放的時(shí)間有順序要求時(shí),將復(fù)位同步器級(jí)聯(lián)起來(lái)就可以構(gòu)成多個(gè)時(shí)鐘域按順序的復(fù)位釋放(實(shí)際上就是延遲兩拍)。

verilog代碼:

module CLOCK_RESET( input rst_n, input aclk, input bclk, input cclk, output reg arst_n, output reg brst_n, output reg crst_n );

reg arst_n0,arst_n1;reg brst_n0,brst_n1;reg crst_n0,crst_n1;

always @(posedge aclk or negedge rst_n) if(rst_n==0) begin arst_n0《=1’b1; arst_n1《=1‘b0; arst_n《=1’b0; end else begin arst_n《=arst_n1; arst_n1《=arst_n0; end always @(posedge bclk or negedge rst_n) if(rst_n==0) begin brst_n1《=1‘b0; brst_n《=1’b0; end else begin brst_n《=brst_n1; brst_n1《=arst_n; end always @(posedge cclk or negedge rst_n) if(rst_n==0) begin crst_n1《=1‘b0; crst_n《=1’b0; end else begin crst_n《=crst_n1; crst_n1《=brst_n; end endmodule

原文標(biāo)題:RTL設(shè)計(jì)- 多時(shí)鐘域按順序復(fù)位釋放

文章出處:【微信公眾號(hào):FPGA開(kāi)源工作室】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1747瀏覽量

131856 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59979

原文標(biāo)題:RTL設(shè)計(jì)- 多時(shí)鐘域按順序復(fù)位釋放

文章出處:【微信號(hào):leezym0317,微信公眾號(hào):FPGA開(kāi)源工作室】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一文解析跨時(shí)鐘域傳輸

FPGA復(fù)位的8種技巧

復(fù)位電路的設(shè)計(jì)問(wèn)題

怎么判斷同步清零和異步清零

異步置零和同步置零的區(qū)別在哪里

同步電路和異步電路怎么判斷正負(fù)極

同步電路和異步電路的優(yōu)缺點(diǎn)

同步電路和異步電路的優(yōu)缺點(diǎn)有哪些

FPGA同步復(fù)位和異步復(fù)位

FPGA異步信號(hào)處理方法

同步FIFO和異步FIFO區(qū)別介紹

L431采用PLL異步時(shí)鐘,復(fù)位后ADC采樣值發(fā)生偏差的原因?

verilog同步和異步的區(qū)別 verilog阻塞賦值和非阻塞賦值的區(qū)別

同步置數(shù),異步置數(shù),同步清零,異步清零的概念

什么是復(fù)位同步電路 reset synchronizer?

RTL中多時(shí)鐘域的異步復(fù)位同步釋放

RTL中多時(shí)鐘域的異步復(fù)位同步釋放

評(píng)論