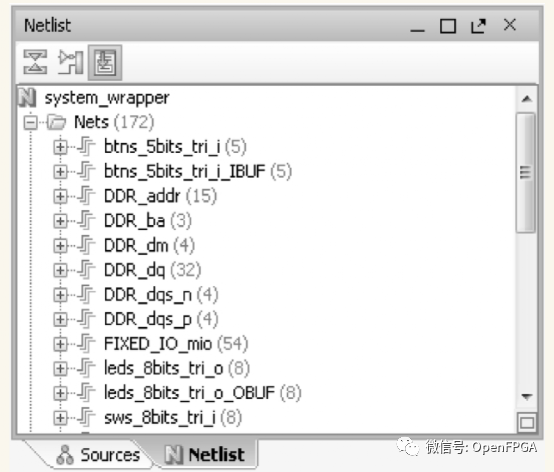

我們都知道FPGA的實現過程分為2步:分析綜合與布局布線后就可以產生目標文件,這兩個步驟中間有個非常重要的文件,那就是-網表。 下圖是Vivado中網表列表示例:

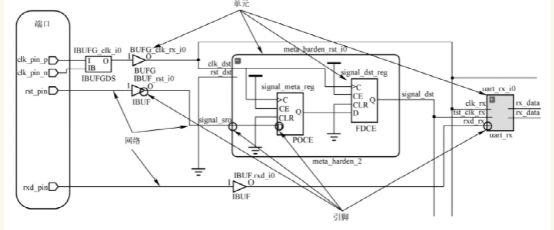

Vivado中網表列表示例 在vivado集成環境中,網表時對設計的描述,如網表由單元(cell)、引腳(pin)、端口(port)和網絡(Net)構成。下圖是一個電路的網表結構:

電路的網表結構

(1)單元是設計單元

1、設計模塊(Verilog HDL)/實體(VHDL)。

2、元件庫中的基本元素(Basic Elements ,BLEs)實例。如LUT、FF、DSP、RAM等。

3、硬件功能的類屬表示。

4、黑盒。

(2)引腳是單元上的連接點

(3)端口是設計的頂層端口

(4)網絡用于實現引腳之間,以及引腳到端口的連接。

編輯:jq

-

dsp

+關注

關注

556文章

8150瀏覽量

355785 -

RAM

+關注

關注

8文章

1391瀏覽量

116966 -

端口

+關注

關注

4文章

1046瀏覽量

32764

原文標題:【Vivado那些事】Vivado中電路結構的網表描述

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

Vivado HLS設計流程

數字電路設計中:前端與后端的差異解析

VirtualLab Fusion應用:如何建立一個真實光柵結構的光導

Vivado Design Suite用戶指南:邏輯仿真

Vivado中電路結構的網表描述

Vivado中電路結構的網表描述

評論