作者:徐孟祥,楊飛,張爾揚

引言

低壓差分信號傳輸LVDS(Low Voltage Differential Signaling)是高速、低電壓、低功率、低噪聲通用I/O接口標準。這種信號傳輸使用非常小的信號幅度(典型值為350mV),通過一對平行的PCB走線或平衡電纜傳輸數據。這對平行差分信號線的電流及電壓振幅相反,噪聲同時耦合到2條信號線上。由于采用差分輸入方式,輸入信號只與2個信號的差值有關,因而可將共模干擾抑制掉。另外,由于2條差分信號線距離很近,電流傳輸方向相反,其磁場相互抵消,電場相互耦合,因而與單線傳輸相比,電磁輻射小得多。

LVDS已廣泛應用于接口器件和現場可編程門陣列(FPGA)、專用集成電路(ASIC)中,采用LVDS的系統成功實現了高速互連。然后,并非所有的LVDS I/O接口都有良好的性能。例如,一些ASIC或FPGA的LVDS I/O可能不象標準器件中的LVDS I/O那樣適合在PCB板上驅動差分跡線(trace)。由于PCB板布局存在的問題,甚至導致設計良好的標準器件的信號傳輸質量變差。當用ASIC或FPGA等作為系統核心件時,有時不可能使器件盡可能靠近連接器放置,這樣會造成跡線變線、反射增大、損耗增加。為了消除互連中存在的問題,國家半導體公司推出一系列體積小巧的緩沖器。文中將對其LVDS超高速交叉點開關SCAN90CP02的功能及應用進行介紹。

1 SCAN90CP02簡介

SCAN90CP02型電路是美國國家半導體公司推出的1.5Gb/s的2x2低壓差分信號傳輸模擬交叉點開關(crosspoint switch)。其高速數據通路和直通(flow-through)引腳可使電路內部的抖動達到最小。當信號在有損的背板和電纜上傳輸時,其可配置的預增強功能(0/25/50/100%可選)能克服外部ISI(Inter Symbol Interference,符號間干擾)抖動的影響。其差分輸入可連接到LVDS和Bus LVDS信號上,也可與共模邏輯(CML)和低電壓正射極耦合邏輯(LVPCL)等信號電平相連。SCAN90CP02要用非塊式交叉點結構,可配置為1:2時鐘或數據分配器、2:1冗余復用器、交叉功能及用于信號增強和短線隱藏的雙緩沖器。圖1是SCAN90CP02的內部方框圖。

SCAN90CP02集成的IEEE 1149.1(JTAG)和1149.6測試輸入電路TAP(Test Access Port)支持單端LVTTL/CMOS和差分LVDS PCB互連的可測試性。這些功能有助于縮短測試時間,降低測試與開發方面的成本。電路采用3.3V電源、CMOS工藝和LVDS I/O,確保其在整個工業級溫度范圍(-40℃到+85℃)內實現高性能和低功耗。

SCAN90CP02可以真正地消除抖動,從而提高系統的可靠性,使用戶能用成本較低的線路實現互連。由于SCAN90CP02設有預增強功能,因此不但可以執行正常的開關功能,而且可作為緩沖器使用,以便將現有的FPGA、ASIC及串行/解串器(SerDes)等的LVDS信號放大。另外,該電路的LVDS輸出不支持多站式(multidrop)BLVDS環境。

SCAN90CP02的特點如下:

●每通道的傳輸速率達1.5Gb/s。

●低功耗,在雙中繼器模式下,最高速率時的電流僅為70mA。

●低輸出抖動。

●可配置的預增強功能(0/25/50/100%)可驅動有損耗的背板和電纜。

●具有直通(Flow-through)引腳引出線。

●LVDS/BLVDS/CML/LVPECL輸入,LVDS輸出。

●適用IEEE 1149.1和1149.6標準。

●單電源3.3V供電。

●可對輸入和輸出進行單獨控制以降低功耗。

●工業級溫度范圍(-40℃至±85℃)。

SCAN90CP02采用28引腳LLP封裝或32引腳LQFP封裝。

電路的預增強功能用于補償遠距離傳輸或者有損耗的傳輸媒質。為使功耗最小,電路為每個輸出提供了獨立的引腳。而且預增功能是可編程設備的。

2 SCAN90CP02的應用

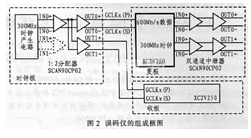

在筆者的設計項目中,需要用高達600Mb/s的速率來傳送數據,由發射機和接收機完成數據收發、調制及信道匹配等任務。為檢驗整個通信系統數據傳輸質量的好壞,筆者另外設計了一臺高速誤碼率測試儀。該測試儀由3塊電路板組成,分別是時鐘產生板、發板和收板。在時鐘產生板和發板上各用了一塊SCAN90CP02,一是可使電路板上的輸出信號盡可能靠近連接器,減輕板上核心電路的布線壓力,使其位置放置更加自由;二是完成電平轉換任務,將LVPECL電平轉換成LVDS電平;三是補償走線的損耗,保證信號有較好的傳輸質量。該誤碼儀的框圖如圖2所示,圖中重點突出了SCAN90CP02的連接方式。以下詳細介紹該測試儀中的各種電路板。

(1)鐘板。時鐘板的SCAN90CP02配置成1:2分配器方式,EN0、EN1、SEL0和SEL1都置為低電平。時鐘板產生的300MHz時鐘信號為LVPECL電平,經SCAN90CP02轉換成2路LVDS電平,分別送往誤碼儀的發板和收板。

(2)發板。發板以Xilinx公司的VirtexII系列XC2V250型電路為核心,由一些外圍電路和控制電路組成,完成偽碼產生、數據成幀、并串變換等功能。輸出的600Mb/s數據和300MHz時鐘經SCAN90CP02中斷通過連接器送到發射機。SCAN90CP02配置成雙通道中斷器方式,SEL1置高電平,其他控制端置電平。

(3)收板。收板以Xilinx公司的VirtexII系列XC2V250型電路為核心,由一些外圍電路和控制電路組成。實現幀同步、數據恢復、串并變換、比較計數和誤碼統計顯示等功能。

SCAN90CP02的預增強控制端采用撥碼開關來選擇高、低電平,以增加設計的靈活性。

3 結束語

在許多應用中特別是用高損耗的背板及電纜連接時,一些電路(如ASIC和FPGA等)的驅動能力往往不足,這就需要使用帶有預增強功能的電路(如SCAN90CP02)預先將信號放大,這樣不但可以保證接收器獲得足夠的輸入信號電壓,而且還可增大傳輸距離,改善信號質量。特別是采用LVDS傳輸方式時,其抗干擾能力大大增強,同時也降低了電磁輻射。

責任編輯:gt

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614953 -

集成電路

+關注

關注

5420文章

11979瀏覽量

367458 -

開關

+關注

關注

19文章

3275瀏覽量

94988

發布評論請先 登錄

美國國家半導體兩款低功率LVDS 2x2交叉點開關電路

SCAN90CP02,pdf datasheet (1.5

MAX4989 USB 2.0高速4選2交叉點開關

SCAN90CP02型LVDS交叉點開關的功能及應用

SCAN90CP02 具有預強制和 IEEE 1149.6 功能的 1.5 Gbps 2x2 LVDS 交叉點交換器

DS25CP152 3.125Gbps LVDS 2x2交叉點開關數據表

DS25CP152Q汽車應用3.125 Gbps LVDS 2x2交叉點開關數據表

DS25CP102Q汽車應用3.125 Gbps 2X2 LVDS交叉點開關數據表

DS25CP104A/CP114 3.125 Gbps 4x4 LVDS交叉點開關數據表

DS10CP154A 1.5Gbps 4x4 LVDS交叉點開關數據表

DS90CP22 800 Mbps 2x2 LVDS交叉點開關數據表

DS90CP02 1.5 Gbps 2x2 LVDS交叉點開關數據表

DS10CP152 1.5Gbps 2X2 LVDS交叉點開關數據表

DS10CP152Q汽車1.5 Gbps 2X2 LVDS交叉點開關數據表

LVDS超高速交叉點開關SCAN90CP02的性能特點及應用分析

LVDS超高速交叉點開關SCAN90CP02的性能特點及應用分析

評論