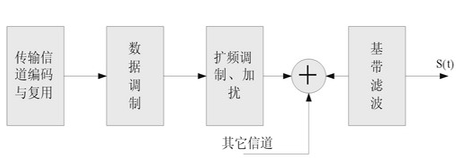

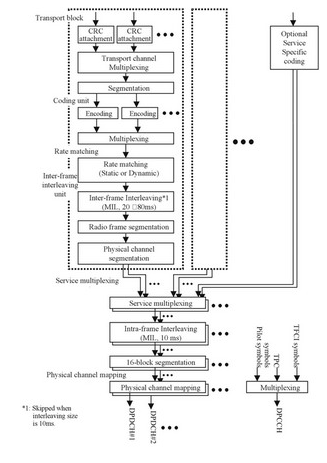

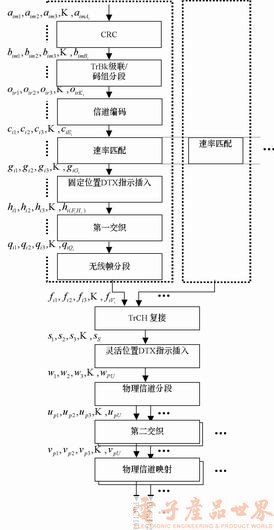

TD-SCDMA系統的基帶處理流程如圖1所示。其中,傳輸信道編碼復用包括以下一些處理步驟:CRC校驗、傳輸塊級聯/分割、信道編碼、無線幀均衡、第 1次交織、無線幀分割、速率匹配、傳輸信道復用、比特擾碼、物理信道分割、第2次交織、子幀分割、物理信道映射等,如圖2所示。

圖1 TD-SCDMA基帶處理框圖

圖2 傳輸信道編碼復用結構

在圖2中,每個傳輸信道(TrCH)對應一個業務,由于各種業務對時延的要求不同,所以其傳輸時間間隔(TTI)是不同的,TTI可以是10ms、20ms、40ms或80ms。

實現方案

本文提出了DSP+FPGA線性流水陣列結構的實現方案:使用DSP與大規模FPGA協同處理基帶發送數據。該處理單元以DPS芯片為核心,構造一個小的DSP系統。

在基帶處理單元中,低層的信號預處理算法處理的數據量大,對處理速度的要求高,但運算結構相對比較簡單,因而適于用FPGA進行硬件實現,這樣能同時兼顧速度及靈活性。相比之下,高層處理算法的特點是所處理的數據量較低層算法少,但算法的控制結構復雜,適于用運算速度高、尋址方式靈活、通信機制強大的DSP芯片來實現。

DSP處理器利用其強大的I/O功能實現單元電路內部和各個單元之間的通信。從DSP的角度來看,FPGA相當于它的協處理器。DSP通過本地總線對 FPGA進行配置、參數設置及數據交互,實現軟硬件之間的協同處理。DSP和FPGA各自帶有RAM,用于存放處理過程所需要的數據及中間結果。除了 DSP芯片和FPGA外,硬件設計還包括一些外圍的輔助電路,如Flash EEPROM、外部存儲器等。其中,Flash EEPROM中存儲了DSP的執行程序;外部存儲器則作為FPGA的外部RAM擴展,用于存放數據處理過程中所需的映射圖樣。

基帶處理單元的需求估計

基帶處理單元的需求估計主要包含以下兩個方面:

1.各個業務傳輸通道的數據處理:以對稱情況下無線信道承載的最高業務速率384kbps為例進行分析。傳輸塊大小為336bit,24塊級聯,加上 CRC,系統在1個10ms幀內所要處理的最大數據量為8448bit:根據3GPP協議TS 25.222規定的下行數據基帶處理流程(見圖2),并按固定位置復用的方式進行處理,每個數據位必須經過最多13個環節的處理過程,估算平均每環節上每比特的處理要求為23條指令。則10ms內必須完成的處理指令數是:8448×13×23=2525952條。對應的處理能力要求是252MIPS。

2.消息處理:包含消息的解釋、對應控制參數的計算、發給對應的FPGA。估計不超過一條承載64kbps業務的無線信道的基帶數據處理的需求。

綜合考慮上述兩個方面,則整個基帶數據處理的等效需求是:

以TMS320C5510為例,其主時鐘能工作在160MHz或200MHz,運算速度達400MIPS。基于C的軟件開發環境和匯編級并行處理的優化程序,優化后的并行執行效率一般為80%,等效的處理能力為320MIPS。可見,若將整個基帶數據處理交給該DSP芯片完成,其處理能力無法滿足整個處理單元的需求,而且,隨著視頻電話、手機電視等大數據量業務的應用,數據處理需求量將更大。因此,在基帶處理的實現方案中,數據量小的業務,如隨路信令、 AMR語音業務可由DSP處理;而數據量大的業務,如64kbps、144kbps和384kbps速率的業務,大部分處理環節由FPGA完成。具體實現如下:

DSP作為主控單元,完成數據提取、消息解析和部分基帶數據處理功能,如第二次交織和成幀等;

FPGA則在DSP的調度下完成基帶數據處理環節中大部分比較耗時的處理功能,如:CRC校驗、信道編碼、速率匹配等,在接收端可用于Viterbi譯碼、聯合檢測等。

在384kbps業務信道加隨路信令的處理中,384Rbps業務數據由DSP通過同步高速接口,以DMA方式遞交給FPGA,在FPGA中處理;而隨路信令因其數據量小,在FPGA處理384kbps業務數據時,隨路信令數據在DSP中同時處理。此方法減少了數據處理時間,提高了處理速度。

結語

本文介紹了一個軟硬件結合的設計方案。硬件電路的實際測試表明,該結構不僅在高速率業務的處理時延上符合規范要求,而且對不同類型的業務處理有較強的適應能力,滿足TD-SCDMA系統對多媒體業務傳輸的支持。

責任編輯:gt

-

dsp

+關注

關注

555文章

8148瀏覽量

355445 -

FPGA

+關注

關注

1643文章

21979瀏覽量

614491 -

芯片

+關注

關注

459文章

52243瀏覽量

436715

發布評論請先 登錄

FPGA+DSP導引頭信號處理中的FPGA技術該怎么實現?

求大神分享一種WCDMA系統基帶處理的DSP FPGA實現方案

基于DSP和FPGA的熱像儀電子處理單元全數字化設計

WCDMA系統基帶處理的DSP+FPGA實現方案

采用DSP芯片的MELP聲碼器的算法設計方案

TD-SCDMA系統基帶處理的DSP+FPGA實現方案

基于DSP和FPGA芯片實現基帶處理單元的設計方案

基于DSP和FPGA芯片實現基帶處理單元的設計方案

評論