摘要:在對FFT(快速傅立葉變換)算法進行研究的基礎上,描述了用FPGA實現(xiàn)FFT的方法,并對其中的整體結構、蝶形單元及性能等進行了分析。 傅立葉變換是數(shù)字信號處理中的基本操作,廣泛應用于表述及分析離散時域信號領域。但由于其運算量與變換點數(shù)N的平方成正比關系,因此,在N較大時,直接應用DFT算法進行譜變換是不切合實際的。然而,快速傅立葉變換技術的出現(xiàn)使情況發(fā)生了根本性的變化。本文主要描述了采用FPGA來實現(xiàn)2k/4k/8k點FFT的設計方法。

1整體結構

一般情況下,N點的傅立葉變換對為: 其中,WN=exp(-2 pi/N)。X(k)和x(n)都為復數(shù)。與之相對的快速傅立葉變換有很多種,如DIT(時域抽取法)、DIF(頻域抽取法)、Cooley-Tukey和Winograd等。對于2n傅立葉變換,Cooley-Tukey算法可導出DIT和DIF算法。

本文運用的基本思想是Cooley-Tukey算法,即將高點數(shù)的傅立葉變換通過多重低點數(shù)傅立葉變換來實現(xiàn)。雖然DIT與DIF有差別,但由于它們在本質(zhì)上都是一種基于標號分解的算法,故在運算量和算法復雜性等方面完全一樣,而沒有性能上的優(yōu)劣之分,所以可以根據(jù)需要任取其中一種,本文主要以DIT方法為對象來討論。

N=8192點DFT的運算表達式為: 式中,m=(4n1+n2)(2048k1+k2)(n=4n1+n2,k=2048k1+k2)其中n1和k2可取0,1,...,2047,k1和n2可取0,1,2,3。 由式(3)可知,8k傅立葉變換可由4×2k的傅立葉變換構成。

同理,4k傅立葉變換可由2×2k的傅立葉變換構成。而2k傅立葉變換可由128×16的傅立葉變換構成。128的傅立葉變換可進一步由16×8的傅立葉變換構成,歸根結底,整個傅立葉變換可由基2、基4的傅立葉變換構成。2k的FFT可以通過5個基4和1個基2變換來實現(xiàn);

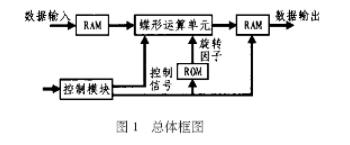

4k的FFT變換可通過6個基4變換來實現(xiàn);8k的FFT可以通過6個基4和1個基2變換來實現(xiàn)。也就是說:FFT的基本結構可由基2/4模塊、復數(shù)乘法器、存儲單元和存儲器控制模塊構成,其整體結構如圖1所示。 圖1中,RAM用來存儲輸入數(shù)據(jù)、運算過程中的中間結果以及運算完成后的數(shù)據(jù),ROM用來存儲旋轉因子表。蝶形運算單元即為基2/4模塊,控制模塊可用于產(chǎn)生控制時序及地址信號,以控制中間運算過程及最后輸出結果。

2蝶形運算器的實現(xiàn)

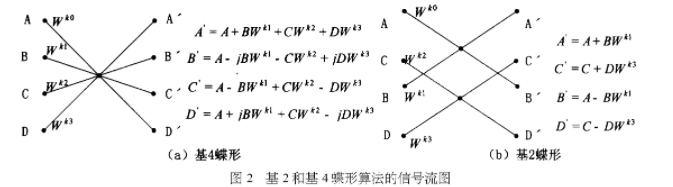

基4和基2的信號流如圖2所示。

圖中,若A=r0+j*i0,B=r1+j*i1,C=r2+j*i2,D=r3+j*i3是要進行變換的信號,Wk0=c0+j*s0=1,Wk1=c1+j*s1,Wk2=c2+j*s2,Wk3=c3+j*s3為旋轉因子,將其分別代入圖2中的基4蝶形運算單元,

則有: A′=[r0+(r1×c1-i1×s1)+(r2×c2-i2×s2)+(r3×c3-i3×s3)]+j[i0+(i1×c1+r1×s1)+(i2×c2+r2×s2)+(i3×c3+r3×s3)]?? (4) B′=[r0+(i1×c1+r1×s1)-(r2×c2-i2×s2)-(i3×c3+r3×s3)]+j[i0-(r1×c1-i1×s1)-(i2×c2+r2×s2)+(r3×c3-i3×s3)] (5) C′=[r0-(r1×c1-i1×s1)+(r2×c2-i2×s2)-(r3×c3-i3×s3)]+j[i0-(i1×c1+r1×s1)+(i2×c2+r2×s2)-(i3×c3+r3×s3)] (6) D′=[r0-(i1×c1+r1×s1)-(r2×c2-i2×s2)+(i3×c3+r3×s3)]+j[i0+(r1×c1-i1×s1)-(i2×c2+r2×s2)-(r3×c3-i3×s3)]?? (7)

而在基2蝶形中,Wk0和Wk2的值均為1,這樣,將A,B,C和D的表達式代入圖2中的基2運算的四個等式中,則有: A′=r0+(r1×c1-i1×s1)+j[i0+(i1×c1+r1×s1)]?? (8) B′=r0- (r1×c1-i1×s1)+j[i0-(i1×c1+r1×s1)] (9) C′=r2+(r3×c3-i3×s3)+j[i0+(i3×c3+r3×s3)]?? (10) D′=r2-(r3×c3-i3×s3)+j[i0-(i3×c3+r3×s3)]?? (11) 在上述式(4)~(11)中有很多類同項,如i1×c1+r1×s1和r1×c1-i1×s1等,

它們僅僅是加減號的不同,其結構和運算均類似,這就為簡化電路提供了可能。同時,在蝶形運算中,復數(shù)乘法可以由實數(shù)乘法以一定的格式來表示,這也為設計復數(shù)乘法器提供了一種實現(xiàn)的途徑。 以基4為例,在其運算單元中,實際上只需做三個復數(shù)乘法運算,即只須計算BWk1、CWk2和DWk3的值即可。

這樣在一個基4蝶形單元里面,最多只需要3個復數(shù)乘法器就可以了。在實際過程中,在不提高時鐘頻率下,只要將時序控制好?煴憧衫?用流水線(Pipeline)技術并只用一個復數(shù)乘法器就可完成這三個復數(shù)乘法,大大節(jié)省了硬件資源。

3FFT的地址

FFT變換后輸出的結果通常為一特定的倒序,因此,幾級變換后對地址的控制必須準確無誤。 倒序的規(guī)律是和分解的方式密切相關的,以基8為例,其基本倒序規(guī)則如下: 基8可以用2×2×2**基2變換來表示,則其輸入順序則可用二進制序列(n1 n2 n3)來表示,變換結束后,其順序?qū)⒆優(yōu)椋ǎ睿?n2 n1)。

如:X?煟埃保保?→ x?煟保保埃牐?即輸入順序為3,輸出時順序變?yōu)椋丁?更進一步,對于基16的變換,可由2×2×2×2,4×4,4×2×2等形式來構成,相對于不同的分解形式,往往會有不同的倒序方式。以4×4為例,其輸入順序可以用二進制序列(n1 n2 n3 n4)來表示變換結束后,其順序可變?yōu)椋ǎǎ睿?n4)(n1 n2))。

如:X?煟埃保保保?→ x?煟保保埃保牎<詞淙胨承蛭?7,輸出時順序變?yōu)椋保场?在2k/4k/8k的傅立葉變換中,由于要經(jīng)過多次的基4和基2運算,因此,從每次運算完成后到進入下一次運算前,應對運算的結果進行倒序,以保證運算的正確性。

4旋轉因子

N點傅立葉變換的旋轉因子有著明顯的周期性和對稱性。其周期性表現(xiàn)為: FFT之所以可使運算效率得到提高,就是利用 FFT之所以可使運算效率得到提高,就是利用了對稱性和周期性把長序列的DFT逐級分解成幾個序列的DFT,并最終以短點數(shù)變換來實現(xiàn)長點數(shù)變換。

根據(jù)旋轉因子的對稱性和周期性,在利用ROM存儲旋轉因子時,可以只存儲旋轉因子表的一部分,而在讀出時增加讀出地址及符號的控制,這樣可以正確實現(xiàn)FFT。因此,充分利用旋轉因子的性質(zhì),可節(jié)省70%以上存儲單元。 實際上,由于旋轉因子可分解為正、余弦函數(shù)的組合,故ROM中存的值為正、余弦函數(shù)值的組合。

對2k/4k/8k的傅立葉變換來說,只是對一個周期進行不同的分割。由于8k變換的旋轉因子包括了2k/4k的所有因子,因此,實現(xiàn)時只要對讀ROM的地址進行控制,即可實現(xiàn)2k/4k/8k變換的通用。

5存儲器的控制

因FFT是為時序電路而設計的,因此,控制信號要包括時序的控制信號及存儲器的讀寫地址,并產(chǎn)生各種輔助的指示信號。同時在計算模塊的內(nèi)部,為保證高速,所有的乘法器都須始終保持較高的利用率。這意味著在每一個時鐘來臨時都要向這些單元輸入新的操作數(shù),而這一切都需要控制信號的緊密配合。

為了實現(xiàn)FFT的流形運算,在運算的同時,存儲器也要接收數(shù)據(jù)。這可以采用乒乓RAM的方法來完成。

這種方式?jīng)Q定了實現(xiàn)FFT運算的最大時間。對于4k操作,其接收時間為4096個數(shù)據(jù)周期,這樣?煟疲疲緣淖畬笤慫閌奔渚褪牽矗埃梗陡鍪?據(jù)周期。另外,由于輸入數(shù)據(jù)是以一定的時鐘為周期依次輸入的,故在進行內(nèi)部運算時,可以用較高的內(nèi)部時鐘進行運算,然后再存入RAM依次輸出。

為節(jié)省資源,可對存儲數(shù)據(jù)RAM采用原址讀出原址寫入的方法,即在進行下一級變換的同時,首先應將結果回寫到讀出數(shù)據(jù)的RAM存貯器中;而對于ROM,則應采用與運算的數(shù)據(jù)相對應的方法來讀出存儲器中旋轉因子的值。

在2k/4k/8k傅立葉變換中,要實現(xiàn)通用性,控制器是最主要的模塊。2k、4k、8k變換具有不同的內(nèi)部運算時間和存儲器地址,在設計中,針對不同的點數(shù)應設計不同的存儲器存取地址,同時,在完成變換后,還要對開始輸出有用信號的時刻進行指示。

6硬件的選擇

本設計的硬件實現(xiàn)選用的是現(xiàn)場可編程門陣列(FPGA)來滿足較高速度的需要。本系統(tǒng)在設計時選用的是ALTERA公司的STRATIX芯片,該芯片中包含有DSP單元,可以完成較為耗費資源的乘法器單元。

同時,該器件也包含有大量存儲單元,從而可保證旋轉因子的精度。 除了一些專用引腳外,FPGA上幾乎所有的引腳均可供用戶使用,這使得FPGA信號處理方案具有非常好的I/O帶寬。大量的I/O引腳和多塊存儲器可使設計獲得優(yōu)越的并行處理性能。其獨立的存儲塊可作為輸入/工作存儲區(qū)和結果的緩存區(qū),這使得I/O可與FFT計算同時進行。

在實現(xiàn)的時間方面,該設計能在4096個時鐘周期內(nèi)完成一個4096點的FFT。若采用10MHz的輸入時鐘,其變換時間在200μs左右。而由于最新的FPGA使用了MultiTrack互連技術,故可在250MHz以下頻率穩(wěn)定地工作,同時,FFT的實現(xiàn)時間也可以大大縮小。

FFT運算結果的精度與輸入數(shù)據(jù)的位數(shù)及運算過程中的位數(shù)有關,同時和數(shù)據(jù)的表示形式也有很大關系。一般來說,浮點方式比定點方式精度高。而在定點計算中,存儲器數(shù)據(jù)的位數(shù)越大,運算精度越高,使用的存儲單元和邏輯單元也越多。在實際應用中,應根據(jù)實際情況折衷選擇精度和資源。

本設計通過MATLAB進行仿真證明:其實現(xiàn)的變換結果與MATLAB工具箱中的FFT函數(shù)相比,信噪比可以達到65db以上,完全可以滿足一般工程的實際應用要求。

作者:連冰,宮豐奎,張力,李兵兵

編輯:jq

-

RAM

+關注

關注

8文章

1391瀏覽量

116964 -

數(shù)字信號處理

+關注

關注

16文章

567瀏覽量

46604 -

FDT

+關注

關注

0文章

5瀏覽量

9311

原文標題:基于FPGA的快速傅立葉變換

文章出處:【微信號:vision263com,微信公眾號:新機器視覺】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

進群免費領FPGA學習資料!數(shù)字信號處理、傅里葉變換與FPGA開發(fā)等

傅立葉變換在機器學習中的應用 常見傅立葉變換的誤區(qū)解析

傅立葉變換與時域信號的關系 傅立葉變換在音頻信號處理中的應用

如何使用傅立葉變換進行頻譜分析

傅立葉變換在圖像處理中的作用

傅立葉變換與拉普拉斯變換的區(qū)別

傅立葉變換的基本概念 傅立葉變換在信號處理中的應用

多平臺FPGA工程快速移植與構建

經(jīng)典傅里葉變換與快速傅里葉變換的區(qū)別

無線通信頻譜分析儀的技術原理和應用場景

在TMS320C62x上實現(xiàn)的擴展精度基數(shù)-4快速傅里葉變換

簡述DC變換器的控制方式

拓撲篇丨LLC諧振變換器快速設計與開發(fā)

拓撲篇丨LLC諧振變換器快速設計與開發(fā)

簡述FPGA的快速傅立葉變換

簡述FPGA的快速傅立葉變換

評論