PC/104嵌入式控制PC出現(xiàn)于20世紀(jì)80年代末,并于1992年形成IEEEP966.1標(biāo)準(zhǔn)。它一方面繼承了PC的所有資源,另一方面又對PC的各個方面做了優(yōu)化設(shè)計,使其與IBM PC完全兼容,并具有體積小,功耗低,工作溫度寬,可靠性高等特點。采用了獨特的“自棧式”總線連接、模塊化結(jié)構(gòu),使用起來靈活方便;采用面向?qū)ο蟮挠布O(shè)計方法,使得在PC/104標(biāo)準(zhǔn)上開發(fā)的擴展模塊具有更強的通用性和更長的生命期;它以其優(yōu)良的品質(zhì)、高可靠性及模塊化,廣泛應(yīng)用于工業(yè)控制、航空航天、軍事、醫(yī)療、消防設(shè)備、智能儀器儀表、導(dǎo)航、通訊、數(shù)控、自動化生產(chǎn)設(shè)備、便攜式計算機等領(lǐng)域。

CAN(Controller Area Network)總線是一種有效支持分布控制或?qū)崟r控制的串行通信網(wǎng)絡(luò),采用多主協(xié)議,廢除了傳統(tǒng)的站地址編碼,而采用對通信數(shù)據(jù)塊進行編碼的方法,使網(wǎng)絡(luò)內(nèi)節(jié)點個數(shù)在理論上不受限制。它具有總線仲裁、錯誤檢測、自動重發(fā)等功能。由于采用了許多新技術(shù)及獨特的設(shè)計,CAN總線具有高實時性、卓越性能、高可靠性、能獨特靈活設(shè)汁和低廉價格,已廣泛應(yīng)用于工業(yè)現(xiàn)場、控制、智能大廈、小區(qū)安防、交通工具、醫(yī)療儀器、環(huán)境監(jiān)控等眾多領(lǐng)域。目前,它已被公認為是幾種最有前途的現(xiàn)場總線之一。隨著科技的發(fā)展,同一系統(tǒng)應(yīng)用多種總線技術(shù)已經(jīng)成為一種趨勢。本設(shè)計利用FPGA完成PC/104總線和CAN總線之間的相互通訊,將兩總線相結(jié)合,優(yōu)勢互補,使兩總線有更大應(yīng)用價值和更廣闊的使用前景。

1 硬件設(shè)計

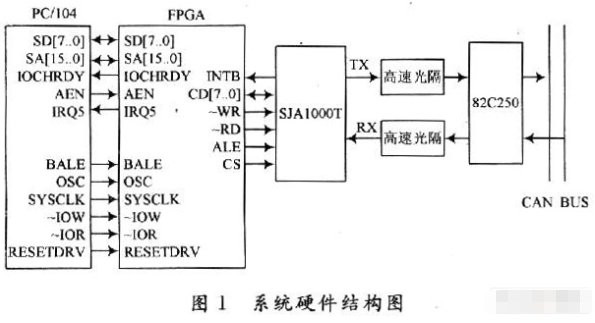

1.1 系統(tǒng)硬件結(jié)構(gòu)

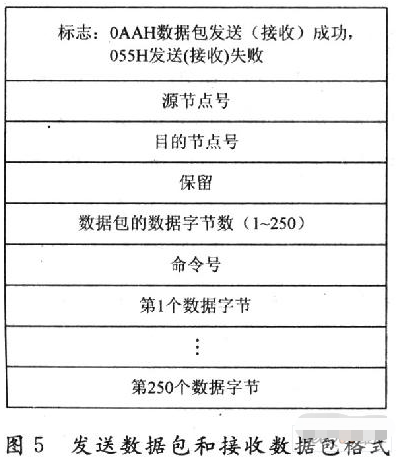

本設(shè)計采用PC/104模板形式,具有很強的方便性和可擴展性,其系統(tǒng)的硬件結(jié)構(gòu)如圖1所示。

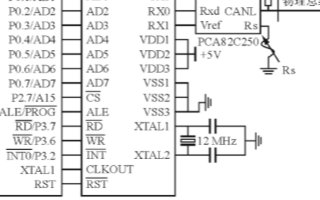

由于PC/104總線采用的是地址數(shù)據(jù)總線分離的總線結(jié)構(gòu),而CAN總線協(xié)議控制器SJA1000T采用的是地址數(shù)據(jù)總線分時復(fù)用的總線結(jié)構(gòu),因此系統(tǒng)使用FPGA器件EP20K100實現(xiàn)總線轉(zhuǎn)換和時序邏輯控制轉(zhuǎn)換。該通訊板采用I/O映射方式,其內(nèi)部寄存器地址為280H~2BFH。為了增強系統(tǒng)的抗干擾能力,在控制器SJA1000T與收發(fā)器82C250之間接入光電耦合器6N137。光耦6N137的上升時間典型值為30 ns,隔離電壓為3 000 V,其支持最大頻率值超過30 MHz。

1.2 FPGA設(shè)計

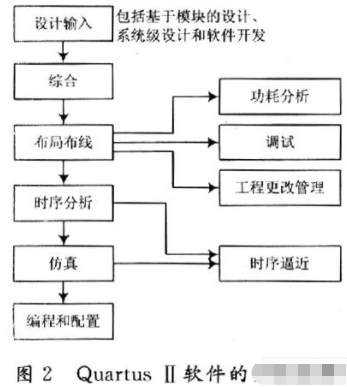

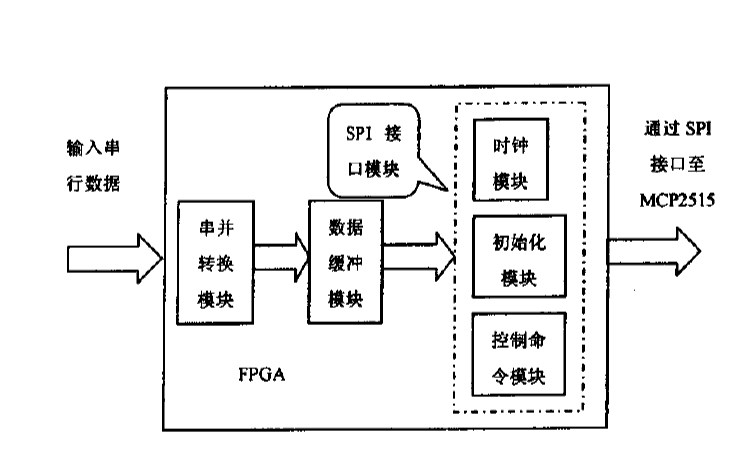

QuartusⅡ是Altera公司在21世紀(jì)初推出的FP-GA/CPLD開發(fā)環(huán)境,是Altera前一代FPGA/CPLD集成開發(fā)環(huán)境MAx+PlusⅡ的更新?lián)Q代產(chǎn)品,其功能強大,界面友好,使用便捷。QuartusⅡ軟件集成了Al-tera的FPGA/CPLD開發(fā)流程中所涉及的所有工具和第三方軟件接口。QuartusⅡ軟件的開發(fā)流程如圖2所示。

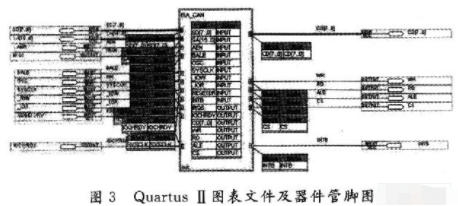

采用原理圖輸入和硬件描述語言相結(jié)合的方式,進行編譯后寫人器件中;同時可在線更改寫入內(nèi)容,修改和調(diào)試簡單易行。FPGA的設(shè)計主要由兩部分組成:第一部分實現(xiàn)時序邏輯控制信號的轉(zhuǎn)換,第二部分實現(xiàn)地址譯碼和地址數(shù)據(jù)線的復(fù)用。QuartusⅡ圖表文件及器件管腳如圖3所示。

由于PC/104的地址總線和數(shù)據(jù)總線是各自獨立的,SJA1000T的地址總線和數(shù)據(jù)總線是分時復(fù)用的,所以它們之間不能直接相連,必須通過時序邏輯控制,再配合軟件來實現(xiàn)讀/寫操作。對SJA1000T的操作方法是:首先,對地址為CAN首地址+0(A2A1A0=000)的端口進行寫操作(WR為低,有效),CANALE為高,有效,此時復(fù)用的地址、數(shù)據(jù)總線上的數(shù)據(jù)被視為地址信號,進入SJA1000T內(nèi)部鎖存器;然后,對地址為cAN首地址+1(A2A1A0=001)的端口進行讀或?qū)懖僮鳎≧D/WR為低,有效),CANALE為低,上述中的地址信號已被鎖存,此時復(fù)用的地址、數(shù)據(jù)總線上的數(shù)據(jù)被視為數(shù)據(jù)信號,這樣即可完成對SJA1000T的各個寄存器和緩沖區(qū)的讀或?qū)懖僮鳌?/p>

1.3 硬件電路測試

主要檢測硬件結(jié)構(gòu)及電路板設(shè)計是否正確。建立一個簡單的通訊連接,將兩個通訊板連接進行測試,用通訊板A作為輸出,通訊板B作為輸入。編程通過通訊板A發(fā)送數(shù)據(jù),內(nèi)容為8個隨機數(shù),檢測通訊板B接收數(shù)據(jù),如果不同則作加1計數(shù)。反之將通訊板B作為輸出,通訊板A作為輸入,進行相同測試。測試200萬次循環(huán)未見異常。

2 軟件設(shè)計

2.1 軟件流程圖

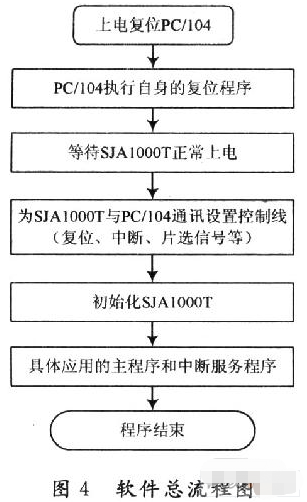

在該通訊板的設(shè)計中,控制部分的核心采用了PC/104嵌入式計算機系統(tǒng)。由于PC/104嵌入式計算機系統(tǒng)幾乎具有和一般的PC機一樣的強大功能,所以該通訊板的開發(fā)是在和系統(tǒng)模塊棧接在一起后,直接在嵌入式計算機上進行的。這些工作都是采用C語言進行編程設(shè)計的。采用C語言的優(yōu)點在于其快速性、高效性。在利用嵌入式計算機強大資源的條件下,C語言能滿足模塊的實時性要求。在系統(tǒng)軟件的設(shè)計中,采用了結(jié)構(gòu)化、模塊化的設(shè)計方法,滿足了儀器功能的要求。本接口系統(tǒng)的軟件任務(wù)基本為在CAN協(xié)議芯片SJA1000T有中斷發(fā)生時,根據(jù)SJA1000T的中斷寄存器的內(nèi)容完成相應(yīng)的操作(如發(fā)送、接收數(shù)據(jù)幀等)。其流程圖如圖4所示。

系統(tǒng)設(shè)計中要進行接口驅(qū)動程序的設(shè)計,為保證操作系統(tǒng)的穩(wěn)定和安全,驅(qū)動程序必須按一定的規(guī)范來編寫。本系統(tǒng)的驅(qū)動程序主要考慮以下內(nèi)容:設(shè)置端口和中斷號,設(shè)置通訊板通訊默認參數(shù),通訊板內(nèi)存分配,映射I/O地址,創(chuàng)建通訊板事件和數(shù)據(jù)接收事件,初始化中斷等。

SJA1000T初始化只有在復(fù)位模式下才能進行,初始化主要包括:工作方式的設(shè)置、接收濾波方式的設(shè)置、接收屏蔽寄存器和接收代碼寄存器的設(shè)置、波特率設(shè)置和中斷允許寄存器的設(shè)置等。SJA1000T在完成初始化后就可以回到工作狀態(tài)進行正常的通訊任務(wù)了。

2.2 CAN多幀數(shù)據(jù)通信打包和解包技術(shù)

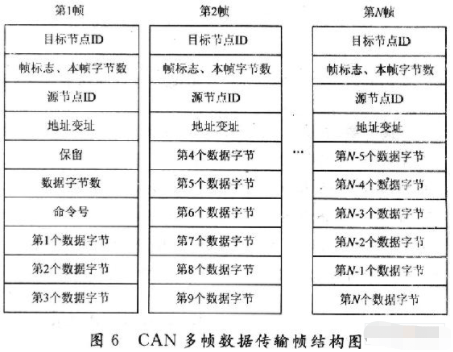

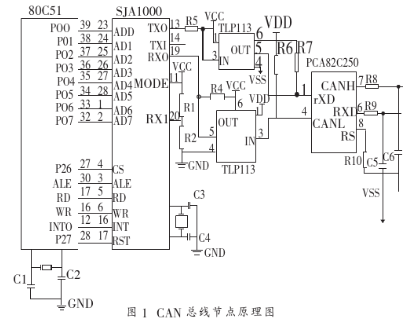

CAN通信數(shù)據(jù)傳輸采用短幀結(jié)構(gòu),每幀最多發(fā)送8個字節(jié)的有效數(shù)據(jù),總線的有效傳輸速率很低,當(dāng)在傳輸?shù)臄?shù)據(jù)量超過8個字節(jié)有效數(shù)據(jù)時,給用戶編程帶來了一定的困難。利用如圖5所示的CAN的數(shù)據(jù)包格式,只需將待傳輸?shù)臄?shù)據(jù)進行相應(yīng)的打包和解包操作即可實現(xiàn)數(shù)據(jù)的單幀和多幀傳輸,有效地簡化了數(shù)據(jù)通信。

采用如圖5所示的CAN數(shù)據(jù)包格式,無論是單幀還是多幀傳輸,只要把數(shù)據(jù)填入相應(yīng)的發(fā)送緩沖區(qū)即可,在接收方,則將數(shù)據(jù)解包并放入接收緩沖區(qū)即可。與上述數(shù)據(jù)包格式相對應(yīng),當(dāng)CAN總線進行多幀傳輸時,其CAN的多幀數(shù)據(jù)傳輸幀結(jié)構(gòu)如圖6所示。

在圖6中,當(dāng)發(fā)送的有效數(shù)據(jù)個數(shù)不超過4個時,一幀數(shù)據(jù)即可傳輸;當(dāng)有效數(shù)據(jù)超過4個時,則需要多幀傳輸。此處的地址變址是指從發(fā)送緩沖區(qū)所取的存放于該幀的第一個有效數(shù)據(jù)的存儲地址相對于緩沖區(qū)首地址的偏移量,如第一幀中地址變址為4,第二幀中的地址變址是10。地址變址的設(shè)置,使得對數(shù)據(jù)包的解包和打包實現(xiàn)起來較容易。

3 結(jié) 語

該通訊板設(shè)計簡單,只需一塊FPGA,一個CAN控制器SJA1000T和收發(fā)器PCA82C250,為增強系統(tǒng)的穩(wěn)定性,在通信通道上均采用光電隔離技術(shù),保護PC機避免因地環(huán)流而損壞,增強系統(tǒng)在惡劣環(huán)境中使用的可靠性。該通訊板采用的CAN數(shù)據(jù)包格式提高了總線的有效傳輸速率,經(jīng)測試達到500 Kb/s,提高了通訊板通訊的實時性。本設(shè)計方案已成功應(yīng)用于工業(yè)控制器中,效果理想。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1644文章

21989瀏覽量

615230 -

控制器

+關(guān)注

關(guān)注

114文章

17022瀏覽量

183276 -

總線

+關(guān)注

關(guān)注

10文章

2956瀏覽量

89451

發(fā)布評論請先 登錄

車載智能控制器 工程機械控制器 CAN總線控制器 碩博電子 #控制器 #can總線 #國產(chǎn)化替代

PowerPC 60x總線的存儲器控制器的設(shè)計與實現(xiàn)

PCI總線目標(biāo)控制器的設(shè)計

PCI總線從設(shè)備控制器的設(shè)計與實現(xiàn)

利用單總線控制器通訊

基于CAN總線的家庭控制器的設(shè)計與實現(xiàn)

基于Lonworks總線的模糊控制器實現(xiàn)

基于MCS-51單片機和CAN總線控制器實現(xiàn)總線節(jié)點的設(shè)計

采用CAN總線控制器SJA1000實現(xiàn)控制電路接口的設(shè)計

如何使用FPGA和CAN控制器MCP2515實現(xiàn)慣導(dǎo)系統(tǒng)的CAN總線接口的設(shè)計

基于QuartusⅡ和控制器實現(xiàn)總線通訊板的設(shè)計

基于QuartusⅡ和控制器實現(xiàn)總線通訊板的設(shè)計

評論