嵌入式系統(tǒng)是以應(yīng)用為中心,以計(jì)算機(jī)技術(shù)為基礎(chǔ),并且軟硬件可裁剪,適用于應(yīng)用系統(tǒng)對(duì)功能、可靠性、成本、體積、功耗有嚴(yán)格要求的專用計(jì)算機(jī)系統(tǒng)。它一般由嵌入式微處理器、外圍硬件設(shè)備、嵌入式操作系統(tǒng)以及用戶的應(yīng)用程序4部分組成,用于實(shí)現(xiàn)對(duì)其他設(shè)備的控制、監(jiān)視或管理等功能。

不管是在科研設(shè)備中還是在家用微波爐中,都可以看到嵌入式控制技術(shù)的影子,嵌入式控制技術(shù)已經(jīng)成功的應(yīng)用在各種領(lǐng)域中,并且越來越廣泛的進(jìn)入到人們的生活中。

在控制電路的設(shè)計(jì)中,數(shù)據(jù)的輸入/輸出端口是控制器完成數(shù)據(jù)輸出和接收功能的關(guān)鍵部分,因此這一部分電路設(shè)計(jì)的好壞關(guān)系到控制器能否正常工作。

1 數(shù)字輸入端口邏輯設(shè)計(jì)分析

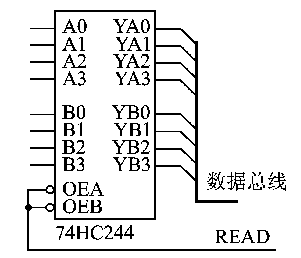

以控制器為中心,按照數(shù)據(jù)的流向分,控制器的端口分為數(shù)字輸入端和數(shù)字輸出端兩種,其中最簡(jiǎn)單的一種I/O形式是數(shù)字輸入。下面從最簡(jiǎn)單的數(shù)字輸入端設(shè)計(jì)來討論在輸入端口設(shè)計(jì)中遇到的實(shí)際問題和解決方法。由于控制器的數(shù)據(jù)輸入輸出引腳數(shù)量少,并且在使用時(shí)要分時(shí)復(fù)用,因此一般控制器和外部設(shè)備之間使用緩沖器或鎖存器連接。如圖1所示,緩沖器74HC244放置在處理器和外部器件之間,當(dāng)處理器要讀取連接在外部接口上的設(shè)備信號(hào)時(shí),處理器通過READ引腳使74HC244輸出引腳有效。這樣,外部設(shè)備數(shù)據(jù)就能夠通過74HC244的A0“A3和B0”B3引腳傳輸?shù)?4HC244的緩沖器中,然后被送到數(shù)據(jù)總線上,微控制器就能夠讀入設(shè)備的數(shù)據(jù)了。

圖1所示的接口方式適合于輸入端少的情況,而對(duì)于現(xiàn)在面向便攜式設(shè)備的SoC設(shè)計(jì),不僅要求性能高、體積小,更要求功耗低。一般而言,SoC的靜態(tài)功耗很小,而對(duì)負(fù)載電容充放電的動(dòng)態(tài)功耗很大。如果總線上掛著很多功能設(shè)備,那么會(huì)導(dǎo)致總線的電容負(fù)載很大。如果總線與片外設(shè)備聯(lián)系,那么控制器還要驅(qū)動(dòng)很長(zhǎng)的片外連線以及片外設(shè)備。如果系統(tǒng)設(shè)計(jì)有許多數(shù)字輸入端,那么采用74HC244這種輸入方案就會(huì)有些問題。這是由于74HC244三態(tài)輸出端的最小電容值為20 pF,比SoC內(nèi)部各節(jié)點(diǎn)的電容負(fù)載0.05 pF高出三個(gè)量級(jí),過多的74HC244連接會(huì)使處理器數(shù)據(jù)總線上的電容負(fù)載值比較大,使得數(shù)據(jù)總線無法接收數(shù)據(jù)。

為了減小電容對(duì)數(shù)據(jù)輸入的影響,可以對(duì)圖1所示的方案改進(jìn)成如圖2所示的方案,采用數(shù)據(jù)選擇器來替代74HC244,比如用74HC257。74HC257輸出端的最大電容值為15 pF,比74HC244的輸出端電容稍小一些。從圖2中可以看到,采用74HC257可以使控制器的一條數(shù)據(jù)總線連接兩條輸入端,這就相當(dāng)于一條數(shù)據(jù)總線的輸入電容值只有7.5 pF。當(dāng)然,也可以采用8選1的數(shù)字邏輯電路,比如74LS138或74HC151,但是它們沒有三態(tài)功能,因此要與74HC244結(jié)合使用,來提供數(shù)字輸入功能。這樣能使處理器每條數(shù)據(jù)總線的輸入電容降為只使用74HC244時(shí)的1/8。

如果系統(tǒng)設(shè)計(jì)中不需要對(duì)多于數(shù)據(jù)總線數(shù)量的數(shù)字輸入端進(jìn)行同時(shí)取樣,以上的74HC244 和 74HC257方案就完全可以適用。如果在系統(tǒng)設(shè)計(jì)中,要求必須同時(shí)取樣大量的數(shù)字輸入端,就必須 在電路設(shè)計(jì)中使用鎖存器來鎖存數(shù)據(jù)。在電路設(shè)計(jì)中,經(jīng)常使用的鎖存器是74HC374和74HC574,這兩種鎖存器的功能相當(dāng)。由于74HC574的輸入引腳和輸出引腳分列在集成塊的兩邊,這樣的排列使制作印刷電路板時(shí)的布線比較簡(jiǎn)單;另一方面,74HC574的輸出電容值為15 pF,這個(gè)值與74HC244的輸出電容值幾乎一樣,因此在設(shè)計(jì)中一般選用74HC574,電路連接如圖3所示,使用鎖存器可以同時(shí)取樣大量的數(shù)據(jù)輸入端。

數(shù)據(jù)選擇器可以降低每條總線的負(fù)載電容值,而不能同時(shí)取樣數(shù)據(jù)輸入端。使用數(shù)據(jù)鎖存器,會(huì)增大數(shù)據(jù)總線的電容負(fù)載,這樣就必須在取樣數(shù)據(jù)線的數(shù)量和采用數(shù)據(jù)選擇器的數(shù)量之間找到一個(gè)恰當(dāng)?shù)狞c(diǎn)。

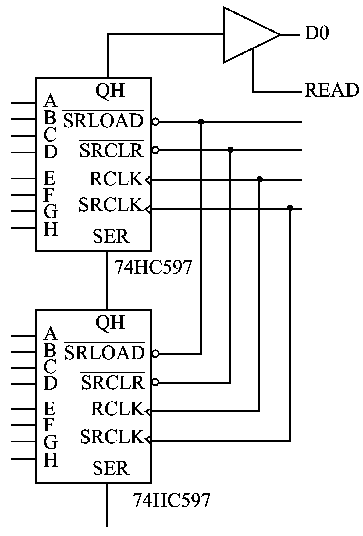

圖4給出了一個(gè)較好的解決方案。在電路中,移位寄存器74HC597被級(jí)聯(lián)在一起,并且與控制器的總線相連接, 這樣可以給處理器提供大量的數(shù)字輸入引腳,同時(shí)每條總線上的電容負(fù)載值又可以達(dá)到最小。

74HC597是移位寄存器,它有8個(gè)觸發(fā)器與輸入引腳相連,這些觸發(fā)器是邊沿觸發(fā)的輸入鎖存器;同時(shí),74HC597有另外的8個(gè)邊沿觸發(fā)的鎖存器串聯(lián)在一起,構(gòu)成移位寄存器。在圖4中,當(dāng)膠粘邏輯一個(gè)上升沿信號(hào)給RCLK時(shí),數(shù)據(jù)輸入引腳的信號(hào)被同時(shí)取樣,接下來處理器通過膠粘邏輯傳送一個(gè)信號(hào)給SRLOAD,使取樣得到的數(shù)據(jù)從輸入鎖存器移入移位寄存器。在移位寄存器內(nèi),處理器通過SRCLK使數(shù)據(jù)每一時(shí)鐘周期移動(dòng)一位,數(shù)據(jù)在READ端允許讀出時(shí),由D0引腳送到數(shù)據(jù)總線上。

還可以對(duì)這個(gè)電路進(jìn)行簡(jiǎn)單變形,將74HC597的QH信號(hào)引腳通過一個(gè)多路緩沖器連接到每一條數(shù)據(jù)總線上,比如采用74HC244,這樣改進(jìn)后,減少了處理串行數(shù)據(jù)的時(shí)間,并且可以一次讀出。

2 數(shù)據(jù)輸入端口保護(hù)設(shè)計(jì)分析

前面已經(jīng)討論了多種解決微處理器數(shù)據(jù)總線和外部設(shè)備接口的方法,下面將從實(shí)踐的角度討論避免系統(tǒng)外部干擾的方法。

在電路設(shè)計(jì)中,使CMOS器件的輸入端懸空是一種不良的設(shè)計(jì)習(xí)慣,因?yàn)镃MOS器件是電壓控制,而未被連接的輸入端有靠近CMOS門檻電壓輸入的趨勢(shì),使得芯片內(nèi)部的三極管作不必要的開關(guān)動(dòng)作,這既增加了噪聲干擾,又耗費(fèi)了系統(tǒng)的功率。一般,使用上拉電阻或下拉電阻,把未被連接的輸入引腳與電源或接地點(diǎn)連接,使它們有一個(gè)確定的電壓值。CMOS輸入引腳的最大輸入電流非常小,只有1 μ A左右,因此選用1 MΩ作為上拉電阻或下拉電阻。

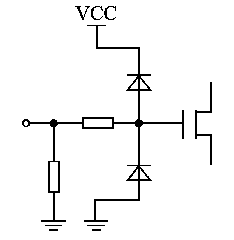

在許多嵌入式系統(tǒng)中,輸入引腳的有效電壓一般是5 V以上或?yàn)樨?fù)值(對(duì)地),在這種情況下,使用幾個(gè)電阻就可以防止輸入引腳過壓。如圖5所示,CMOS集成塊內(nèi)部的2個(gè)二極管可以把電壓鉗位在CMOS器件輸入電壓值,這2個(gè)二極管是高速CMOS器件(74HC系列)靜電保護(hù)措施的一部分。

如圖6所示,在輸入端連接2個(gè)肖特基二極管,這樣可以更安全的保護(hù)輸入端口,但是成本會(huì)高一些。前端電壓降到集成塊內(nèi)部2個(gè)二極管導(dǎo)通電壓的1/3,內(nèi)部的2個(gè)二極管不會(huì)導(dǎo)通,電流全部通過前端正向偏壓的肖特基二極管。這種電壓保護(hù)電路在有些應(yīng)用設(shè)計(jì)中是必須的。在一般設(shè)計(jì)中,沒有輸入引腳需要這樣的額外保護(hù),因?yàn)檫@樣的外部電壓保護(hù)需要使用非常講究的印刷電路板,并且往電路板上安裝這些元件也需要一些制造成本,對(duì)于只采用無源元件的設(shè)計(jì)來說,這個(gè)安裝成本是不能忽略的。

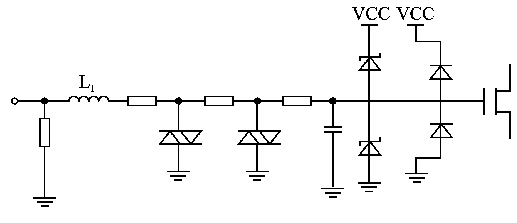

圖7給出了另外一種保護(hù)方法,它有兩種作用:一是電容和電阻構(gòu)成一個(gè)低通濾波器,用來減小輸入信號(hào)的尖脈沖,而低頻信號(hào)能夠通過;二是低通濾波器還有靜電保護(hù)的功能。

下面討論這種設(shè)計(jì),如果是理想電容器,1個(gè)0.1 μF的電容串聯(lián)一個(gè)22 k Ω電阻就能夠提供靜電保護(hù)。但是實(shí)際器件是不會(huì)工作在理想狀態(tài)下的,在電路中,有等效串聯(lián)電阻和等效串聯(lián)電感存在,如圖8所示。

電容生產(chǎn)商通常會(huì)給出圖表,用來描述他們生產(chǎn)的電容器的典型ESR(等效串聯(lián)電阻)和ESL(等效串聯(lián)電感),方便設(shè)計(jì)者建立適當(dāng)?shù)碾娐纺P停治鲭娐返?a target="_blank">工作原理。但是建立這樣的模型還是很困難,因?yàn)殡娐纺P椭杏行┢骷?a target="_blank">參數(shù)是不好確定的。解決這一困難的方法只有通過實(shí)驗(yàn)去驗(yàn)證,這要增加試驗(yàn)設(shè)備的成本。

電路中的防靜電保護(hù)裝置還有瞬態(tài)電壓抑制器TVS(Transient Voltage Suppressor),它是一種二極管形式的高效能保護(hù)器件。當(dāng)TVS二極管的兩極受到反向瞬態(tài)高能量沖擊時(shí),它能以10-12秒量級(jí)的速度,將其兩極間的高阻抗變?yōu)榈妥杩梗崭哌_(dá)數(shù)kW的浪涌功率,使兩極間的電壓箝位于一個(gè)預(yù)定值,有效地保護(hù)電子線路中的精密元器件,免受各種浪涌脈沖的損壞。由于它具有響應(yīng)時(shí)間快、瞬態(tài)功率大、漏電流低、擊穿電壓偏差小、箝位電壓較易控制、無損壞極限、體積小等優(yōu)點(diǎn),已廣泛應(yīng)用于計(jì)算機(jī)、數(shù)碼相機(jī)等精密電子設(shè)備的保護(hù)電路中。

圖示電路對(duì)于大多數(shù)設(shè)計(jì)來說顯得過分復(fù)雜,但如果不使用光電隔離器件,對(duì)于精密的設(shè)計(jì)或者條件要求嚴(yán)格的設(shè)計(jì)來說是最好的。在這樣的設(shè)計(jì)中,元件價(jià)格和電路板元件位置的排列也是要考慮的要素。

由于在制造金屬膜電阻時(shí),金屬線中插入了一些絕緣層來改變金屬線的幾何結(jié)構(gòu)以達(dá)到一個(gè)準(zhǔn)確的電阻值,而這使得靜電容易從絕緣面滲入金屬層。使用這種類型電阻構(gòu)成的電路有兩種后果:第一,當(dāng)有靜電電壓時(shí),實(shí)際有效電阻值會(huì)比其標(biāo)稱值小;第二,容易形成電離通道,改變電阻的實(shí)際值。表面貼片電阻有另外一個(gè)問題,那就是當(dāng)有靜電電壓時(shí),它們與金屬層的焊接點(diǎn)會(huì)形成發(fā)熱點(diǎn),這是由于金屬表面不均勻的電流密度引起的。這樣會(huì)造成貼片電阻被靜電電流燒毀,在電路中選用電阻時(shí),普通的炭膜電阻是最好的選擇。

光電隔離器件也可以用于數(shù)字輸入引腳靜電保護(hù)和防干擾,它們可以用來隔離幾kV的電壓,而輸入設(shè)備必須提供比CMOS門電路需要的電流大1000倍的輸入電流給光電隔離器件。光電隔離器件轉(zhuǎn)換速度比較慢,并且在設(shè)計(jì)中還要考慮如何保護(hù)光電隔離器件中的LED不受靜電的破壞,設(shè)計(jì)中,要根據(jù)設(shè)計(jì)的需要進(jìn)行合適的選擇。

結(jié)語

輸入接口設(shè)計(jì)是嵌入式控制器系統(tǒng)的關(guān)鍵部分,因?yàn)榍度胧娇刂破魍獠繑?shù)據(jù)的接收,外部設(shè)備狀態(tài)的反饋都要通過接口才能交給處理器。設(shè)計(jì)輸入端口時(shí)主要考慮兩個(gè)方面的實(shí)際情況:一是負(fù)載能力,即輸入信號(hào)能否被控制器接收,二是靜電的防護(hù),現(xiàn)在很多處理器采用CMOS工藝封裝,這能夠滿足低功耗的要求,同時(shí)對(duì)靜電防護(hù)要求更高。

責(zé)任編輯:gt

-

嵌入式

+關(guān)注

關(guān)注

5096文章

19191瀏覽量

308043 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7550瀏覽量

88746 -

微處理器

+關(guān)注

關(guān)注

11文章

2274瀏覽量

82818

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字輸入端口邏輯電路的設(shè)計(jì)及應(yīng)用分析

數(shù)字輸入端口邏輯電路的設(shè)計(jì)及應(yīng)用分析

評(píng)論