提出一種可進化IP核的設計和實現方法。這種IP核采用進化硬件的設計思想,將遺傳算法運用于硬件電路的設計中,使電路能根據當前的環境自動進行內部電路的時化,從而生成最有效的電路,并能在普通的FPGA器件上實現。可進化IP核以HDL源泉代碼的形式表示,與普通IP核的復用方式相同,可被綜合到不同的目標可重構器件中去,大大減少了復雜系統的設計時間,提高了設計的利用率,是可進化硬件一個頗具潛力的發展方向。

隨著信息技術的飛速發展,計算機系統面臨的問題越來越復雜,如何保證復雜系統的可靠性成為一個不容忽視的問題。可進化硬件給我們提供了一個很好的解決方案。可進化硬件EHW(Evolvable Hardware)是將進化算法和可編程邏輯元件融合在一起而產生的一種新的硬件研究流派。當所使用的環境發生變化時,或被放置于未知的環境中時,這種硬件會自動地改變內部結構,使之經常處于最適合狀態,快速高效地完成規定的任務。

可編程門陣列(FPGA)以其獨有的優點為國外多數研究人員用作硬件進化平臺。EHW利用FPGA的在線可編程技術(ISP)及動態重構技術,將FPGA的配置信息作為染色體,通過遺傳算法(GA)對其進行反復的適應度計算,交叉和變異,最終進化出符號環境要求的個體(即電路配置),從而使電路適合環境的變化。

與此同時,隨著FPGA技術的發展,芯片的性能越來越強、規模越來越大、開發的周期越來越長,使得芯片設計業正面臨一系列新的問題:設計質量難以控制,設計成本也越來越高。IP(Intelligence Property)技術解決了當今芯片設計業所面臨的難題。IP是指可用來生成ASIC和PLD的邏輯功能塊,又稱IP核(IP Core)或虛擬器件(VC)。設計者可以重復使用已經設計并經過驗證的IP核,從而專注于整個系統的設計,提高設計的效率和正確性,降低成本。目前數字IP已得到了充分的發展,可以很方便地購買到IP核并整合到SoC的設計中。

因此,可以考慮將進化硬件的思想應用于IP核的設計中,設計一種可進化的IP核,根據當前的環境進化出相應的電路,并能夠在普通的可重構器件中實現。

1 什么是可進化IP核

從進化硬件的經驗可知,系統通常只有一部分是適應性的(可進化的),另一部分可以通過傳統的不可變的電路來實現。同樣,使用IP核構造的系統也是有些IP核是可進化的,有些IP核是不可變的。可進化的那些IP核稱為可進化組件或可進化IP核。

可進化IP核像普通的IP核一樣被存儲在組件庫中,在被下載并放在一個可重構器件中后,它們將自動地進化它們的內部電路。當不再需要適應性行為時,可以從可重構器件中刪除可進化IP核。可進化IP核和普通IP核的復用方式相同。

2 可進化IP核的一般體系結構

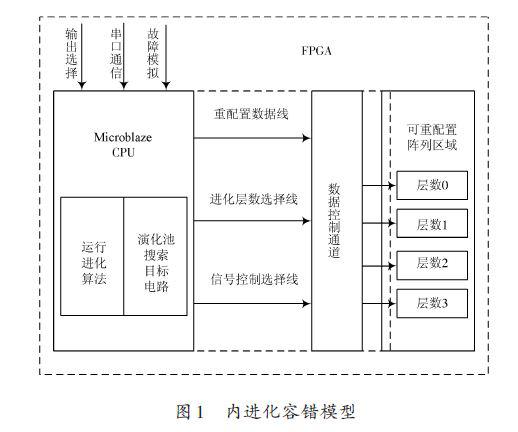

如圖1所示,可進化IP核由可重構電路,基因單元和控制器構成(本文中可重構電路是指可進化IP核內的一個部分;可重構器件是指整個可重構平臺,如FPGA)。這里要強調的是,基因單元不包含適應度計算,它只實現基因的操作、染色體存儲和適應度存儲。適應度的計算和環境由其它的核來提供。基因單元生成一些配置并上載到可重構電路中去,環境對這些配置進行評估,并將適應度值發送給IP核。可進化IP核實際上是一個由環境控制的電路生成器。

環境(由其它核提出)和可進化IP核之間的通信如下:首先IP核被初始化(生成初始化種群),然后進入如下無限循環——當環境發生變化后,環境計算當前電路配置的適應度,并判斷電路是否適應環境。如果染色體存儲器中的配置不可用,則向IP核發出控制信息,IP核開始進化。即基因單元把硬件配置信息作為染色體,根據適應度對其進行交叉、變異等遺傳操作,生成一個新的種群。環境對新種群進行適應度計算,并判斷是否有滿足當前環境的個體(配置)。若沒有,向IP核發控制信息,遺傳單元繼續對電路配置進行進化,直至有滿足當前環境的配置為止;若有,則將適應度值發給IP核,IP核用這個新生成的最優配置來重配置可重構電路,并在染色體存儲器中保存當前最優配置及其適應度值,等待來自環境的下一個請求。

環境總是要求下載當前最優的進化電路,因此,IP核必須保存目前為止最優的配置,并且在需要的時候提供出去。可進化IP核總是屏蔽重構過程,因此它對于外部環境來說是不可見的。

對于一些特殊的應用,必須為它們開發專用的可進化IP核,因為反映應用的要求基因單元和可重構電路的體系結構將使進化過程優于一個隨機的搜索。由于適應度計算是在IP核外進行的,因此IP核原則上支持動態適應度函數和無限的進化。可進化IP核可以用軟件實現。

3 可進化IP核的實現

3.1 實現中的問題

可復用的IP核通常有軟核、固核和硬核三種。本文討論的是軟核。本文的目標是,設計和實現以HDL源代碼(例如,VHDL)表示的可進化IP核。其優點是IP核的表示獨立于平臺,這樣它們就可以在各種不同的目標結構中運行。要解決的主要問題是,可進化的IP核的內部可重構電路的自動重構(因為它們是可進化的)。

當一個可進化IP核從一個組件庫中被下載到可重構器件的一個指定位置時,它的內部可重構電路必須進行重構。這就意味著這個可重構器件中的一些可編程塊必須能配置這個可重構器件的其它內部可編程塊。另外,這個可進化IP核(它的基因單元)能被放置于這個可編程陣列(即可重構器件)的任何位置,也就是說,這個可重構器件中必須支持內部重構。

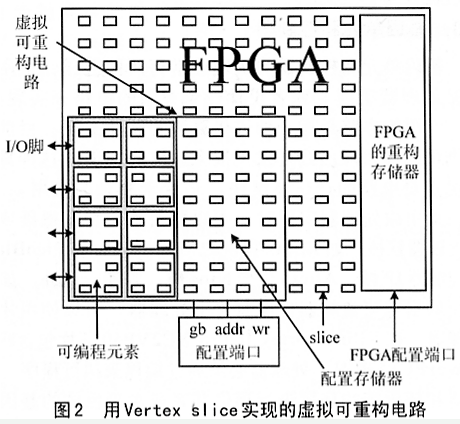

FPGA以其動態可重構的優點,無疑是可進化IP核的最佳實現平臺。然而,通常的FPGA并不支持內部重構,而只允許通過一個特殊的配置接口外部重構(如圖2)。目前,只存在一種支持內部重構的平臺,就是單元陣列,但這種芯片目前還相當少。因此,為了在普通FPGA器件實現可進化IP核,使之能在實際應用中發揮作用,必須采用其它的一些方法。硬件虛擬化是基于FPGA的系統常用的一種設計技術。從這個思想出發,本文采用了一個被稱為虛擬可重構電路的技術來實現可進化硬件中的內部可重構電路。但文中對設計虛擬可重構電路的概念進行了擴展。

3.2 虛擬可重構電路

一些FPGA芯片支持部分重構,也就是允許可重構系統的一部分重構,而不影響其余部分的運行。部分重構的優點在于,其重構所花的時間比全部重構更少。本文以支持部分重構的Xilinx Virtex FPGA為例,來說明虛擬可重構電路的實現。IP核可以動態地下載到FPGA或從FPGA刪除。所有的操作都通過Virtex重構端口和Jbits接口來完成。當一個可進化IP核被下載時,它的重構位串在指定位置構靠下列單元;虛擬可重構電路、基因單元和控制器。

圖2表明,虛擬可重構電路實際上是一種在普通FPGA上實現的新的可重構電路。本例中由八個可編程元素構成,由Virtex單元(slice)實現。Virtex單元實現新的可編程元素陣列、新的布線電路和新的配置存儲器。虛擬電路能內部重構,但如果有其它新的配置存儲器與之連接,也可從FPGA的I/O引腳配置。

這種方法的優點在于:可根據具體的應用需要準確地設計可編程元素陣列、布線電路和配置存儲器。虛擬可重構電路的重構方式和粒度能準確地反映具體應用的需要。通過虛擬可重構電路,很容易把領域知識插入到基因單元和可重構電路的體系結構中,從而獲得電路軟件模型的精確實現。

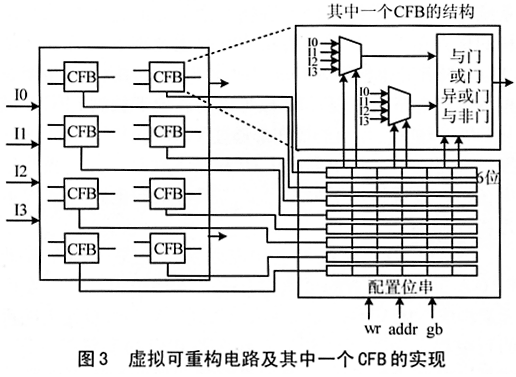

圖3給出了一個虛擬可編程元素的例子。這個虛擬可重構電路由8個這樣的元素構成,有4個輸入和2個輸出。這些虛擬可編程元素稱為可重配置功能塊CFB(Configurable Functional Blocks)。每個CFB對應一個配置位串(這里的位串為6位),其中兩個配置位決定了CFB的功能,其它四位定義了輸入的連接信息。布線電路由多路器組成,它們由配置存儲器中的位串控制。配置存儲器由Virtex單元構成,一個Virtex單元包含兩個觸發器,用于存儲配置位串中的兩位。配置存儲器的所有位都連到多路器,多路器控制布線和CFB中功能的選擇。

虛擬可重構電路中CFB的數量由具體的應用決定。虛擬可重構電路用結構級VHDL語言來描述,但是一些基本的電路(例如“MAX”電路)用行為級來描述。虛擬可重構能在不同的目標器件下綜合,目標器件并不需要支持部分重構。

3.3 基因單元和控制器

基因單元和控制器的實現通常有兩種選擇:采用普通微處理器實現,或者設計一個專用的電路來實現。

專用的電路是指一種進化算法的硬件實現,目前在可進化硬件領域已經開發了很多這樣的實現。這種算法的優點是電路的進化速度快,適合于復雜的應用。

采用微處理器實現時,可以購買或免費獲得現成的微處理器軟核,如Xilinx提供的MicroBlaze和PicoBlaze微控制器IP核,Altera生產Nios核,等等。此外,如果給出的目標可重構器件中有片上處理器,可以使用片上處理器,Xilinx Virtex II Pro XC2VP50芯片包含四個PowerPC處理器。處理器必須通過編程來執行程序,它們能和核周圍的環境進行通信并完成對染色體的基因操作。此外,處理器還負責內部虛擬可重構電路的重構。

4 結論

文中定義了數字系統設計的一個新的抽象級別,并將一些組件的方法引入可進化硬件的設計。為了實現可進化IP核,使用一種虛擬可重構電路。這種方法在門的數量方面代價稍大,但卻能大大加快進化硬件的速度。

可進化IP核的設計目的主要是以合理的代價實現適應性和高性能實時系統,最常見的如圖像壓縮。本文提出的核的結構和接口都只是最基本的,實際應用中還可進行擴充。例如,還可以給核擴充一個讀配置的端口,這個對于某些應用來說是必需的。或者在可進化IP核中包含兩個虛擬可重構電路RC1和RC2。RC1實現當前最優的進化電路。電路不斷進化在RC2中完成。如果RC2中進化出更好的電路,就把它的配置送入RC1,然后RC1以一系列數字電路的形式表現出對變化的環境的最佳的響應。

與以往的方法相比,本文提出的方法具有更強的適應性和可移植性。可進化IP核以HDL源代碼的形式表示,易于重用和修改。此外,進化的配置位串也可以作為一種變化的IP核在其它應用中被重用。可進化IP核縮短了電路設計的時間,提高了設計的利用率,促進可進化硬件向實用化的發展。

責任編輯:gt

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618813 -

PLD

+關注

關注

6文章

230瀏覽量

60224 -

IP核

+關注

關注

4文章

338瀏覽量

50839

發布評論請先 登錄

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

Altera浮點矩陣相乘IP核怎么提高運算速度?

基于EHW 的可進化傳感器的研究

基于SOPC技術的異步串行通信IP核的設計

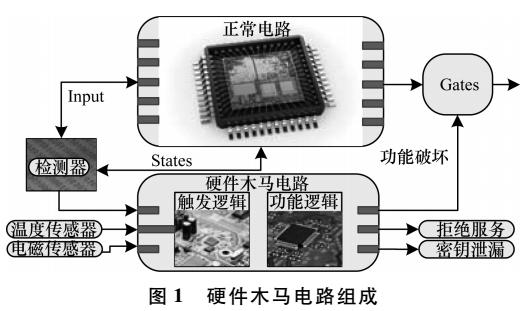

基于特征匹配的IP軟核硬件木馬檢測

基于可進化硬件EHW實現IP核的改進設計

基于可進化硬件EHW實現IP核的改進設計

評論