1、位寬太小

在FPGA設(shè)計中,我們經(jīng)常需要用寄存器來寄存某些“數(shù)量類”的變量,比如FIFO的深度啦、或者計數(shù)器的最大值啦;又或者輸入輸出信號也需要將位寬用parameter參數(shù)化以便更好的調(diào)用等。

舉個簡單的小例子:系統(tǒng)頻率100M(周期10ns),假設(shè)需要要求設(shè)計一個計時器計時100ns,那么需要計數(shù)次數(shù)為:100ns/10ns - 1 = 9,9這個數(shù)需要用多大位寬的寄存器表示呢?很簡單,以2為底取對數(shù)就行,答案是最少4位寬。為了方便地復(fù)用這個模塊,我們把計時時間參數(shù)化并放到模塊外,如下:

module counter #(

parameter TIME = 'd10 //計時時間,單位10ns

)(

input clk_100M ,

input rst

);

reg [3:0] cnt; //計數(shù)器

//計時器

always@(posedge clk_100M)begin

if(rst)

cnt else if(cnt == TIME - 1)

cnt else

cnt end

endmodule

假設(shè)我們下次設(shè)計需要一個計時器的話,直接調(diào)用上面的counter模塊并把TIME這個參數(shù)改成自己需要的參數(shù)就可以,這樣做理論上是可以的,只是會有一個致命的隱患。不妨再假設(shè):我現(xiàn)在調(diào)用了counter模塊,并將TIME設(shè)置為20,以實現(xiàn)計時200ns的功能。當(dāng)TIME = 20這個參數(shù)傳遞到被例化模塊后,可以發(fā)現(xiàn)由于cnt寄存器的位寬僅為4位,其能表示的最大值為4'b1111(即十進制下的數(shù)字15),每次其到達15后就溢出為0重新開始了,也就是說這個200ns的計時器實際上根本就計數(shù)不到200ns。

這個隱患發(fā)生的原因就是在設(shè)計寄存器cnt時的位寬只有4位,無法滿足“大量時間的計時任務(wù)”。

2、自己寫一個Function

現(xiàn)在來想一下如何解決上述的位寬不匹配的問題。將寄存器的位寬設(shè)計為一個較大的數(shù)值(如固定為32bit)不失為一個不錯的方法,但是如果將這條規(guī)則適用到每一個寄存器,則勢必造成大量的資源浪費(你資源多你隨便玩)。而且該方法指標不治本,我們需要做的是,這個寄存器應(yīng)該有多大就設(shè)計多大的位寬(有多大的腳就穿多大的鞋,鞋子太大一定能穿,但你腳不一定舒服)。

前面說過寄存器的位寬的計算方法:以2為底取對數(shù)。所以我們只需要設(shè)計一個Function(可綜合),來實現(xiàn)此項功能即可。剛好在Xilinx的許多源碼都出現(xiàn)了這個簡單的Function,我們直接拿過來用就是的:

// function 實現(xiàn)

function integer clogb2 (input integer bit_depth);

begin

for(clogb2=0; bit_depth>0; clogb2=clogb2+1)

bit_depth = bit_depth >> 1;

end

endfunction

// 使用案例

localparam integer C_TRANSACTIONS_NUM = clogb2(C_M_AXI_BURST_LEN-1);

reg [C_TRANSACTIONS_NUM : 0] write_index;

reg [C_TRANSACTIONS_NUM : 0] read_index;

上面的代碼就是定義了一個求位寬的function,用其求得某類寄存器的位寬,然后再對寄存器賦值時就直接使用求得的位寬來賦值,這樣復(fù)用起來就比較方便了。

我們將這個代碼放到上面的計數(shù)器模塊中后,不管需要計數(shù)多大時間,都能計算出相匹配的寄存器位寬了。

3、無法在輸入輸出端口使用

自己寫Function實現(xiàn)對2取對數(shù)的功能也有一定的局限性:無法對輸入輸出端口信號使用該Function。Function是定義在模塊內(nèi)部,所以若輸入輸出端口也需要根據(jù)輸入的parameter參數(shù)來以2為底取對數(shù)的話此種方法就無能為力了。比如:設(shè)計一個同步FIFO,輸出信號fifo_cnt(計數(shù)器)是對寫入FIFO的數(shù)據(jù)進行計數(shù)的寄存器,其最大值即為FIFO的深度DATA_DEPTH ,所以fifo_cnt的位寬就需要在定義模塊輸入輸出端口時確定,顯然這無法使用自己構(gòu)造的 cblogb2 Function。那該當(dāng)如何?

//計數(shù)器法實現(xiàn)同步FIFO

module sync_fifo_cnt

#(

parameter DATA_WIDTH = 'd8 , //FIFO位寬

parameter DATA_DEPTH = 'd16 //FIFO深度

)

(

input clk , //系統(tǒng)時鐘

input rst_n , //低電平有效的復(fù)位信號

input [DATA_WIDTH-1:0] data_in , //寫入的數(shù)據(jù)

input rd_en , //讀使能信號,高電平有效

input wr_en , //寫使能信號,高電平有效

output reg [DATA_WIDTH-1:0] data_out, //輸出的數(shù)據(jù)

output empty , //空標志,高電平表示當(dāng)前FIFO已被寫滿

output full , //滿標志,高電平表示當(dāng)前FIFO已被讀空

output reg [$clog2(DATA_DEPTH) : 0] fifo_cnt //$clog2是以2為底取對數(shù)

);

//省略部分代碼

endmodule

4、$clog2系統(tǒng)函數(shù)

其實辦法也有,在上面的代碼中也展示出來了,就是使用 $clog2 這個Verilog的系統(tǒng)函數(shù)。$clog2是Verilog--2005標準新增的一個系統(tǒng)函數(shù),功能就是對輸入整數(shù)實現(xiàn)以2為底取對數(shù),其結(jié)果向上取整(如5.5取6)。有一點需要說明的是,目前Vivado2017以上的版本都是支持這個系統(tǒng)函數(shù)的(Quartus II不清楚 )。但是百度搜索這條結(jié)果的時候有兩條結(jié)論是錯誤的:

1、Vivado不支持$clog2系統(tǒng)函數(shù)

2、$clog2系統(tǒng)函數(shù)在Vivado實現(xiàn)的是以e為底取對數(shù),而不是2

接下來寫個簡單的模塊驗證下Vivado對$clog2系統(tǒng)函數(shù)的支持如何

`timescale 1ns / 1ps

module clog2_test#(

parameter integer num = 325

)

(

input clk,

input rst,

output reg [$clog2(num) - 1:0] result

);

always @(posedge clk)begin

if(rst)

result else

result end

endmodule

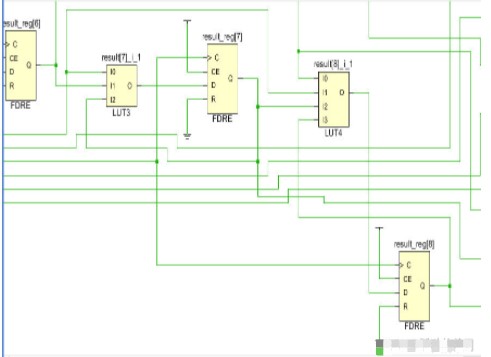

可以看到最后編譯出的結(jié)果是9位的,也就說明Vivado是支持這個系統(tǒng)函數(shù)的(版本:2019.2)。

其他變量的位寬設(shè)計同理。

審核編輯:湯梓紅

-

寄存器

+關(guān)注

關(guān)注

31文章

5423瀏覽量

123418 -

計數(shù)器

+關(guān)注

關(guān)注

32文章

2284瀏覽量

96051 -

參數(shù)

+關(guān)注

關(guān)注

11文章

1867瀏覽量

32874

發(fā)布評論請先 登錄

Ansible Playbook中的變量使用技巧

Verilog中signed和$signed()的用法

Verilog例化說明

Verilog 電路仿真常見問題 Verilog 在芯片設(shè)計中的應(yīng)用

Verilog 與 ASIC 設(shè)計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

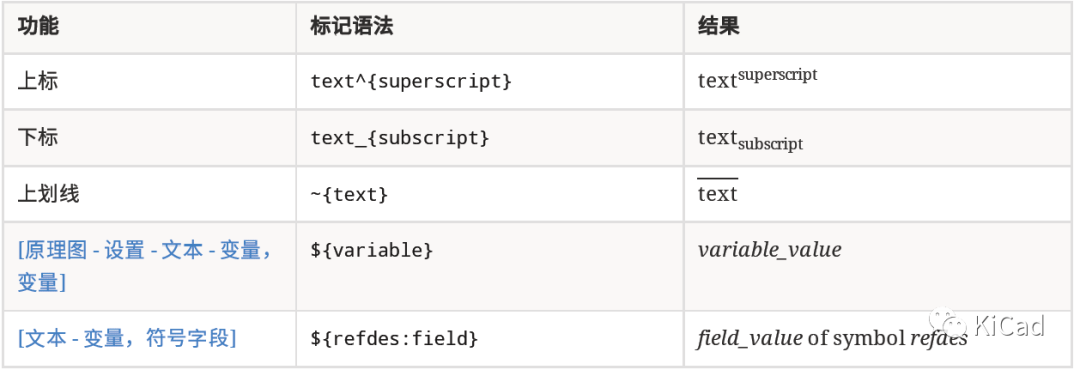

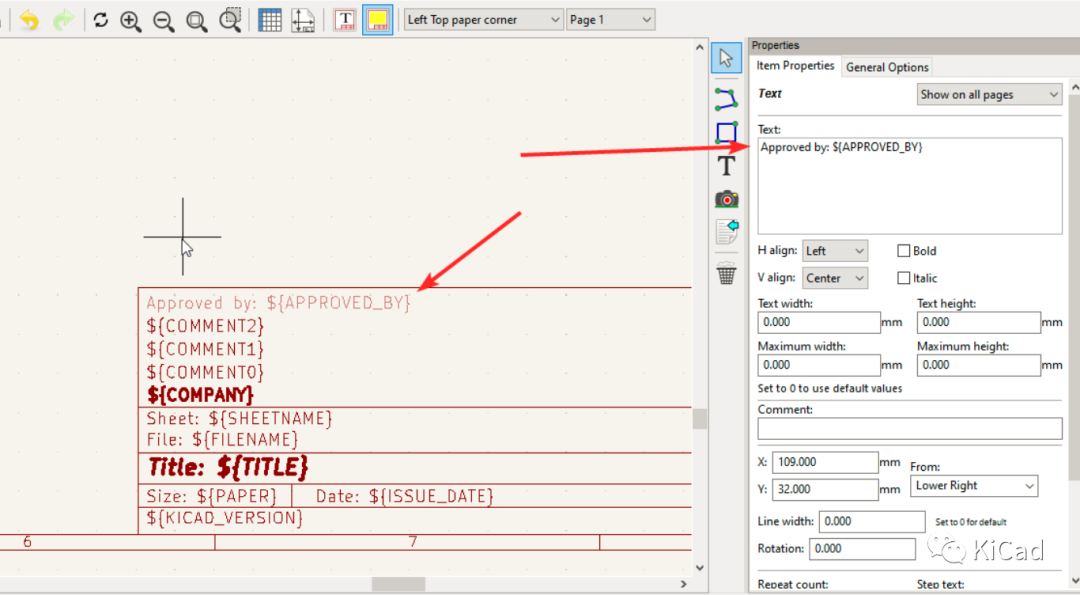

如何在文本字段中使用上標、下標及變量

RISC-V的指令集位寬的幾點學(xué)習(xí)心得

FPGA Verilog HDL有什么奇技巧?

Keil中變量不被初始化方法

Verilog設(shè)計中如何匹配變量的位寬

Verilog設(shè)計中如何匹配變量的位寬

評論